## S magazine

SOLUTIONS FOR HIGH-PERFORMANCE SIGNAL PROCESSING DESIGNS

Simplifying DSP System Designs

## INSIDE

FPGA-Based MPEG-4 Codec

Implementing

Matrix Inversions in

Fixed-Point Hardware

Designing with the Virtex-4 XtremeDSP Slice

The Design and Implementation of a GPS Receiver Channel

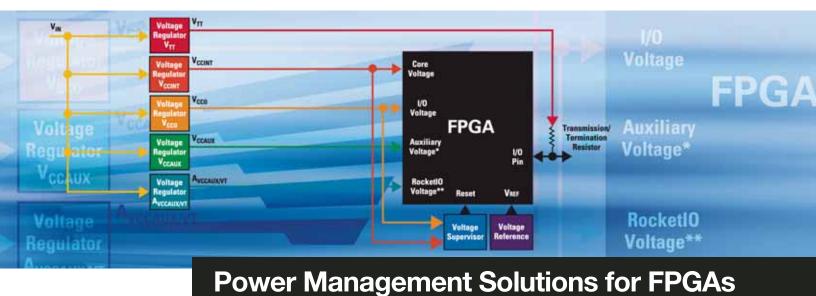

## Support Across The Board.

## **National Devices supported:**

- Voltage Regulators

- Voltage Supervisors

- Voltage References

## Xilinx Devices supported:

- Virtex<sup>TM</sup>

- Virtex-E

- Virtex-II

- Virtex-II Pro

- Virtex-4FX, 4LX, 4SX

- Spartan™-II

- Spartan™-IIE

- Spartan-3, 3E, 3L

Avnet Electronics Marketing has collaborated with National Semiconductor® and Xilinx® to create a design guide that matches National Semiconductor's broad portfolio of power solutions to the latest releases of FPGAs from Xilinx.

Featuring parametric tables, sample designs and step-by-step directions, this guide is your fast, accurate source for choosing the best National Semiconductor Power Supply Solution for your design. It also provides an overview of the available design tools, including application notes, development software and evaluation kits.

Go to em.avnet.com/powermgtguide to request your copy today.

Enabling success from the center of technology™

1 800 332 8638 www.em.avnet.com

## CONTENTS

| VIEWPOINT                                                | ,                          |

|----------------------------------------------------------|----------------------------|

| Setting Industry Direction for High-Performance DSP      |                            |

| MULTIMEDIA, VIDEO, and IMAGING                           |                            |

| FPGA-Based MPEG-4 Codec                                  | 8                          |

| Rapid Development of Video/Imaging Systems               | 10                         |

| Encoding High-Resolution Ogg/Theora Video with Recon     | figurable FPGAs13          |

| Implementing DSP Algorithms Using Spartan-3 FPGAs        | 10                         |

| Using FPGAs in Wireless Base Station Designs             | 20                         |

| Accelerated System Performance with APU-Enhanced Proc    | cessing24                  |

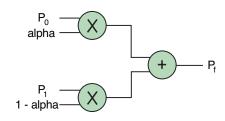

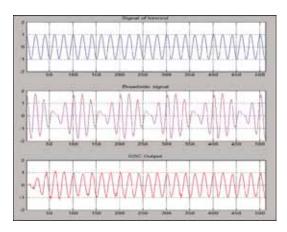

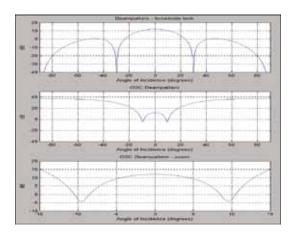

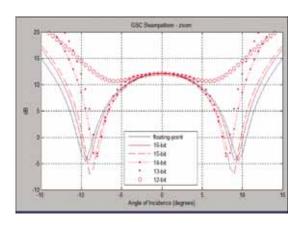

| Alpha Blending Two Data Streams Using a DSP48 DDR 1      | Technique28                |

| DEFENSE SYSTEMS                                          |                            |

| Implementing Matrix Inversions in Fixed-Point Hardware   | 32                         |

| Integrating MATLAB Algorithms into FPGA Designs          | 37                         |

| Software-Defined Radio: The New Architectural Paradigm   | n4(                        |

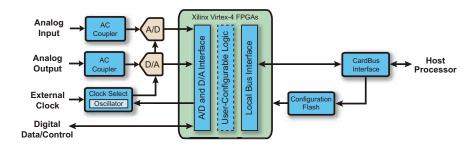

| Virtex-4 FPGAs for Software Defined Radio                | 44                         |

| DIGITAL COMMUNICATION                                    |                            |

| Real-Time Analysis of DSP Designs                        | 46                         |

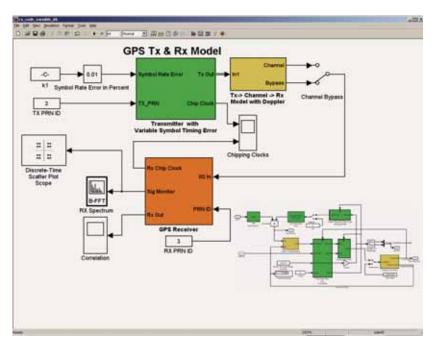

| The Design and Implementation of a GPS Receiver Chan     | nel50                      |

| GENERAL PURPOSE AND IMPLEMENTATION                       |                            |

| Designing Control Circuits for High-Performance DSP Syst | ems55                      |

| Signal Processing Capability with the NuHorizons Sparta  | ın-359                     |

| Designing with the Virtex-4 XtremeDSP Slice              | 62                         |

| Synthesis Tool Strategies                                | 66                         |

| CUSTOMER SUCCESS                                         |                            |

| A Weapon Detection System Built with Xilinx FPGAs        | 68                         |

| EDUCATION                                                |                            |

| DSP Design Flow – Intermediate Level                     | 72                         |

| PRODUCT BRIEFS                                           |                            |

| Virtex-4 SX 35 XtremeDSP Development Kit for Digital Co  | mmunication Applications74 |

| Virtex-II Pro XtremeDSP Development Kit for Digital Comm | • •                        |

| Virtex-4 DSP Brochure                                    | • •                        |

## High-Performance DSP — Vision, Leadership, Commitment

FPGAs are increasingly being used for signal processing applications. They provide the necessary performance and flexibility to tackle many of today's most challenging DSP applications, from MIMO digital communication systems to H.264 encoding to a high-definition broadcast system.

Within such systems, FPGAs are ideally suited for high-performance signal-processing tasks traditionally serviced by an ASIC or ASSP. But you can also use FPGAs to create high-performance DSP engines that boost the performance of your programmable DSP system by performing complementary co-processing functions.

This unique coupling of high performance and flexibility – through exploiting parallelism and hardware reconfiguration – places Xilinx in an ideal position to set the industry direction in the high-performance segment of the DSP market.

Our DSP vision is built on five key pillars:

- Customer and market focus we will create products that meet the needs of our customers and create products in those market segments that are the best fit for our FPGAs.

- **Design methodology** as most DSP designers don't speak VHDL or Verilog, we will continue to evolve software technologies to support languages that they do speak like Simulink and MATLAB.

- Tailored system solutions this includes algorithms, tools, services, and devices for focus markets.

- Ecosystem partnerships/alliances with industry leaders like Texas Instruments, The MathWorks, and Xilinx Global Alliance members to deliver total DSP solutions.

- Awareness educating you on how to quickly access FPGAs for signal processing regardless of your background skill set.

This month we are also launching new DSP Roadmaps for the high-performance segment of the DSP market. These roadmaps cover many areas, including digital communications, multimedia video and imaging, defense systems, design tools and methodologies, development platforms, and base IP solutions. The roadmaps demonstrate our continued investment and commitment in solving your current and future signal-processing challenges.

Finally, we are proud to deliver to you the first edition of *DSP Magazine*. Packed with articles demonstrating how you can create optimized DSP designs using FPGAs, this magazine is one of many ways in which we will provide you the knowledge to finish your DSP designs faster. I would like to dedicate this first Xilinx *DSP Magazine* to you, the customer.

Omid Tahernia Vice President and General Manager Xilinx DSP Division

# Setting Industry Direction for High-Performance DSP Xilinx launches new market-focused DSP Roadmaps.

by Jack Elward Senior Director, Program Management, DSP Division jack.elward@xilinx.com

Have you ever been on a long trip, in somewhat unfamiliar territory, and in search of your next move? You would certainly welcome a map that shows what the road holds in store ahead. Not only is it informative, it can also be reassuring. A good road map will contain enough details about your intended travel path so that you can confidently charge forward or plan for back-ups and alternatives. Of course, sometimes you will want to contact your travel advisor for more details.

Such is the intent of the DSP Roadmap from Xilinx. In publishing the most comprehensive, detailed set of IP, product, and tools plans ever attempted, we intend to shine a floodlight on our next few years of technical releases.

## **DSP Strategic Pillars**

The Xilinx® DSP initiative is based on five strategic pillars:

- Market focus

- Design methodology

- Tailored solutions

- Ecosystem

- Awareness

These pillars are manifested in the DSP Roadmap in the following important ways:

For market focus, we listen to customers and their needs and select highgrowth markets where we can add the most value through our products and services. Xilinx target segments include digital communications (both wired and wireless), aeronautics and defense, and MVI (multimedia, video, and imaging). Other DSP markets (such as test and measurement, industrial, and telemetrics) are well served by our current products and their future roadmaps.

Design methodology refers to a growing awareness that traditional users of FPGAs (using VHDL and Verilog) represent only about 10% of the DSP design community. The vast majority of these designers are:

More familiar with software design tools such as C, C++, and MATLAB,

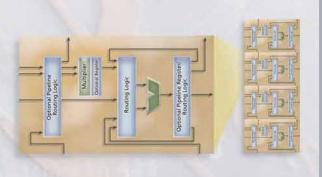

## Complete DSP Design Solutions

- · New DSP Division, Partnerships, Specialists

- · Design Services, Education and Support

- · System Generator for DSP, Third-Party EDA

- · Development Platforms, Starter Kits

- RACH Rx, Searcher, MPEG4

- Optimized Next Generation Co-Processing Interfaces

Figure 1 - Solutions spectum

and a methodology that assumes a robust library of function calls and hardware layer abstraction

- Schooled or experienced in using DSP products from TI, ADI, and Freescale

- In search of higher bandwidth and performance, which can be best delivered through the parallelism of FPGAs

- Concerned with system-level integration, software compatibility and reuse, and rapid prototyping

The tailored solutions strategic pillar is a natural evolution of our traditional building blocks (such as FFT, FIR filters, and other "base blocks") for general DSP applications. There are three clear tines in this fork: IP, tools, and FPGA devices.

In addressing the ecosystem, Xilinx is acknowledging a successful strategy already employed throughout our history. We started off as one of the first fabless semiconductor companies and forged strategic alliances with companies like IBM and TI. Now, with a broad set of IP and tools developed by and offered from third-party vendors, we demonstrate how important it is to go beyond our internal development resources to provide increasingly complete solutions.

Finally, awareness is crucial in affecting the sea change that we desire in positioning Xilinx as a major supplier of DSP solutions. We are clearly positioned and recognized as the world leader in programmable logic, but traditional customer surveys of "DSP supplier awareness" show that we have an uphill climb in the field of entrenched DSP providers such as TI. The roadmaps are a primary vehicle in communicating the expansion of expertise and product offerings, which the recently formed DSP division is capable of delivering.

The DSP Roadmaps cover a broad range of products and services. Figure 1 shows the solution spectrum, ranging from DSP devices to design tools and design services. Tools are inclusive of IP, libraries, boards, and kits.

## **IP** and Solutions

Traditional offerings for DSP designers have been horizontal in nature and apply to

market segments. Elements such as FFTs, FIR filters/compilers, encryption, and linear algebra are good examples. The DSP Roadmaps continue to offer enhancements to the functionality and performance, along with forward migration into new generations of FPGA families.

We are also introducing new building blocks to work in conjunction with complex, hard IP embedded into Xilinx FPGA families, such as the PowerPC<sup>TM</sup> 405

processor and DSP48 blocks. These cores include a floating point co-processor connected to the PowerPC through a dedicated hardware port, and several cores embracing the versatility and inherent performance of the DSP48 slices in their cascaded configuration.

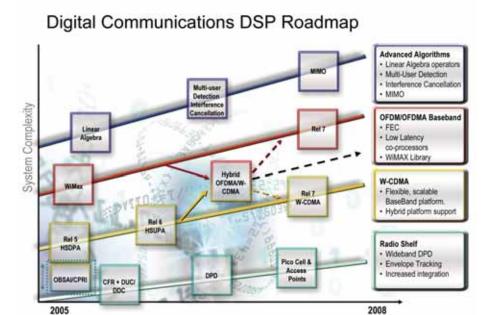

The IP offerings are tailored to meet the needs of specific vertical markets. Therefore, we have created roadmaps to address the following areas: Digital

Figure 2 – Digital Communications DSP Roadmap

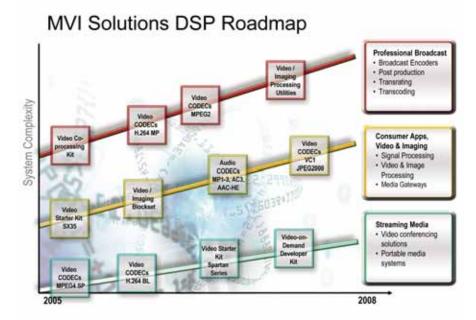

Figure 3 – Multimedia, Video, and Imaging Systems DSP Roadmap

Communication Systems; Multimedia, Video, and Imaging (MVI) Systems; and Defense Systems (represented in Figures 2, 3, and 4, respectively). Each of these roadmaps contains specialized components or solution platforms. This represents the collective expertise of developers, application engineers, and field technical experts in conjunction with invaluable input from customers.

In addition to developing buildingblock IP, Xilinx is moving toward sets of products intended to provide proof of concept, and in some cases, reference quality designs that can be adopted directly into customer solutions. Examples in the digital communications arena are in the 3GPP and W-CDMA standards in radio-shelf and base-band implementations. New areas of rapidly growing interest are the WiMAX standards and Picocell architectures. Similar solutions are included in each of the other market-focused roadmaps.

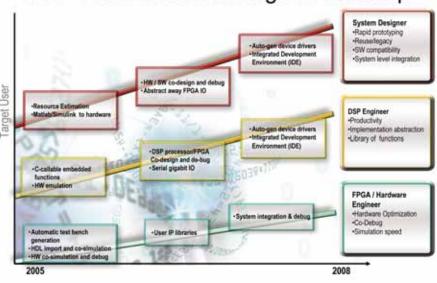

### Tools

The Tools and Methodologies Roadmap shown in Figure 5 illustrates our desire to address the designer community in three major tiers: traditional Xilinx hardware (FPGA) designers, DSP development engineers, and system designers. The strategy is built on the Xilinx ISE<sup>TM</sup> software tools suite, but incorporates System Generator for DSP, our embedded development tool suites, and other third-party offerings. If you haven't reviewed this area recently, you will be quite surprised to see the advances in capability and performance that have been introduced and are coming over the next few releases.

## **Devices**

The Spartan<sup>TM</sup> and Virtex<sup>TM</sup> FPGA families have continued to evolve and include specific functions that optimize performance and power for specific application areas. The multipliers, DSP48, and embedded processors are examples of content directly aimed at the DSP field. The Virtex-4 generation identified subfamilies that allow focused concentrations of features for cost-optimized delivery. In the roadmap for future devices, you will continue to see this focus played out with additional specialized circuits and building blocks committed to silicon.

## Conclusion

The DSP Roadmaps are not intended to be a one-way communication. In presenting our vision of the future, we expect to initiate and share in a dialog with others. We intend to engender discussion and commentary. This is a healthy process of discovery that ultimately leads to better products from Xilinx that help you develop and deliver better products to your customers. We look forward to this dialog and learning between Xilinx and the DSP world.

For more information about our new products and DSP Roadmaps, visit DSP Central at www.xilinx.com/dsp. •

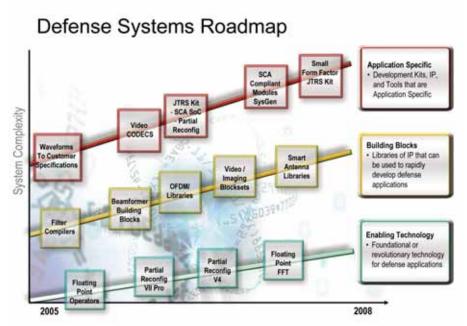

Figure 4 - Defense Systems DSP Roadmap

## DSP Tools & Methodologies Roadmap

Figure 5 – DSP Tools and Methodolgies Roadmap

## FPGA-Based MPEG-4 Codec

Using FPGAs to implement complex video codecs goes beyond ASIC prototyping.

by Paul Schumacher Senior Staff Research Engineer Xilinx, Inc. paul.schumacher@xilinx.com

Wilson Chung

Senior Staff Video and Imaging Engineer

Xilinx, Inc.

wilson.chung@xilinx.com

Have you ever wanted to include state-of-the-art video compression in your FPGA design but found it too complex an undertaking? You no longer need to be a video expert to include video compression in your system. Newly released MPEG-4 encoder/decoder cores from Xilinx can help solve your video compression needs.

Video and multimedia systems are becoming increasingly complex, and the availability of low-cost, reliable IP cores for your system is crucial to getting your product to market. In particular, video compression algorithms and standards have become extremely complicated circuits that can take a long time to design and are quite often bottlenecks in getting a system tested and shipped. These MPEG-4 simple profile encoder/decoder cores may just do the trick for your next multimedia system.

## **Applications**

MPEG-4 Part 2 is a recent international video coding standard in a series of such standards: H.261, MPEG-1, MPEG-2, and H.263. It was approved by ISO/IEC as International Standard 14 496-2 (MPEG-4 Part 2) in December 1999. The MPEG-4 Part 2 video codec provides an excellent basis for a number of multimedia applications. The standard provides a set of profiles and levels to allow for a plethora of different application requirements, such as frame size and use of error-resilience tools. Examples of these applications include

broadcasting, video editing, teleconferencing, security/surveillance, and consumer electronics applications.

The video coding algorithm used in MPEG-4 Part 2 is an evolution from previous coding standards. The frame data is divided into 16 x 16 macroblocks containing six 8 x 8 blocks for YCbCr 4:2:0 formatted data. Motion estimation with half-pixel resolution is used to efficiently code predicted blocks from the previous frame, while the discrete cosine transform (DCT) provides the residual processing to create a more detailed view of the current frame. Simple profile provides 12 bits of resolution for DCT coefficients with 8 bits per sample for the sampled and reconstructed frame data. Coding efficiency of the MPEG-4 simple profile is better than the previous generation in MPEG-2 across a range of coding bit rates.

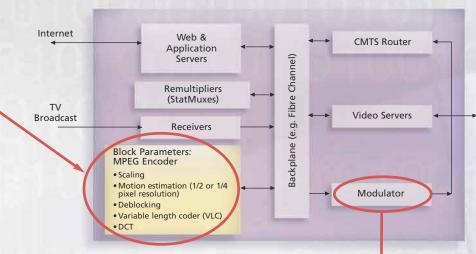

A typical multimedia system can use MPEG-4 as the video compression component within a larger system. An example of this is an end-to-end video conferencing sys-

tem delivering compressed bitstreams between two or more participants. Designations for these sources can modify system requirements, where a key speaker or presenter for a conference may require higher resolution video as well as audio. This type of system can be expanded to video surveillance and security applications, where a display station user may decide to keep a mosaic of all video cameras or focus in on a single camera view for detailed real-time analysis. These applications require that the stream selection is performed at the receiver and is capable of handling real-time viewing specifications.

An FPGA provides an excellent programmable concurrent processing platform that allows for support of varying system requirements while meeting the needs of system throughput. The Xilinx® MPEG-4 decoder core can be built with a scalable, multi-stream interface customized for your application and system requirements, while both the MPEG-4 encoder and decoder are also capable of servicing a user-specified maximum frame size.

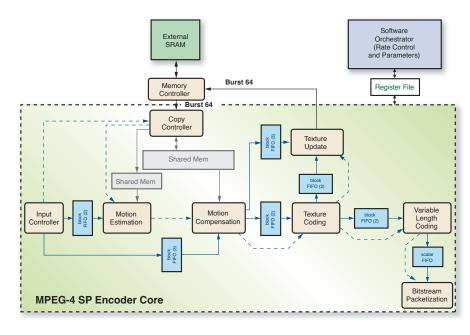

Figure 1 – Block diagram of MPEG-4 Part 2 simple profile encoder core

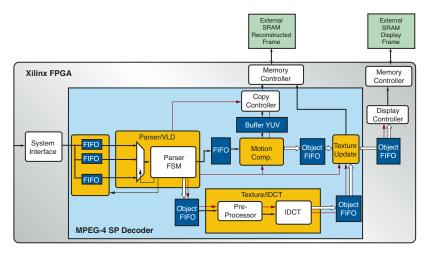

Figure 2 – Block diagram of MPEG-4 Part 2 simple profile decoder core

## Architecture

Figures 1 and 2 illustrate the block diagrams for the MPEG-4 simple profile encoder and decoder cores, respectively. Hardware-based, pipelined architectures were used for these implementations, with a host interface provided on the encoder for software-controlled rate control. With an included memory controller, the raw, captured sequence for the encoder and the reconstructed frames for the decoder are stored in an off-chip memory for fast, low-latency access to the pixel data. A simple FIFO interface is provided for communicating the compressed bitstreams, with the decoder custom-built for a user-specified number of bitstreams. A system interface is also included to allow for maximum controllability and observability.

To create scalable multi-stream designs that can meet the needs of different applications, the package provided with the core contains a number of user-specified, compile-time parameters that allow you to customize the encoder and decoder. To create a resource-efficient design, you can also set the maximum supported frame width and height. The compiled design would then include enough memory and registers to support any frame dimensions less than or equal to these two parameters. Other parameters give you complete control over the scalability of the final design and craft a system built exclusively for your application.

Tables 1 and 2 list the FPGA resources for the encoder and decoder cores based on different parameter settings for maximum supported frame size, as well as the number of input bitstreams for the decoder. All of the encoder designs in Table 1 utilize 16 embedded XtremeDSP<sup>TM</sup> slices, while the decoders in Table 2 utilize 32 embedded XtremeDSP slices. These designs target Virtex<sup>TM</sup>-4 parts, which contain a number of 18 Kb block SelectRAM<sup>TM</sup> memories as well as embedded XtremeDSP slices. Other compatible FPGA families include Virtex-II, Virtex-II Pro, and Spartan<sup>TM</sup>-3 devices.

Note that the decoder design can automatically instantiate the number of input FIFOs and supporting multiplexing/demultiplexing circuitry based on the number of bitstreams to support. The MPEG-4 encoder is capable of a throughput of approximately 48,000 macroblocks per second, providing

enough horsepower to exceed the throughput specifications of simple profile at level 5. Meanwhile, the MPEG-4 decoder design can sustain a throughput of approximately 168,000 macroblocks per second, providing adequate throughput to decode two streams of progressive SDTV (720 x 480 at 60 fps) or 14 streams of CIF resolution. This decoder throughput is more than four times the required throughput for simple profile at level 5.

## **Conclusion**

MPEG-4 simple profile encoder and decoder cores have been designed with unique, scalable, multi-stream capabilities to suit your specific system needs. A number of different applications can take advantage of these cores in a multimedia system, including video conferencing, security, and surveillance, as well as any exciting new consumer application that you have yet to show the world.

High-throughput, pipelined architectures were used for these video designs with enough customizable parameters to create a resource-efficient design exclusive to your application. For more information, visit www.xilinx.com/dsp.

The authors would like to acknowledge contributions from Robert Turney, Nick Fedele, Adrian Chirila-Rus, Mark Paluszkiewicz, and Kees Vissers at Xilinx, as well as members at IMEC.

| Resources Parameters Frame Size | Block RAMs | FPGA Slices | Minimum Clock Rate (MHz) |

|---------------------------------|------------|-------------|--------------------------|

| QCIF @ 15 fps                   | 16         | 8,051       | 3.2                      |

| CIF @ 30 fps                    | 21         | 8,309       | 25.6                     |

| 4CIF @ 30 fps                   | 30         | 9,000       | 100.7                    |

Table 1 – Scalable MPEG-4 Part 2 simple profile encoder core resources

| Parameters Resources |         | Block RAMs  | FPGA Slices  | Minimum Clock Rate (MHz)    |  |

|----------------------|---------|-------------|--------------|-----------------------------|--|

| Frame Size           | Streams | DIOCK KAMIS | TI OA SIICOS | Millimoni Clock Rule (Milz) |  |

| QCIF @ 15 fps        | 1       | 10          | 4,332        | 0.8                         |  |

|                      | 8       | 17          | 5,014        | 6.6                         |  |

| CIF @ 30 fps         | 1       | 16          | 4,558        | 6.6                         |  |

|                      | 8       | 23          | 5,305        | 52.8                        |  |

| 4CIF @ 30 fps        | 1       | 26          | 5,004        | 26.4                        |  |

|                      | 8       | 33          | 5,764        | 211.2 *                     |  |

<sup>\*</sup> Note: Eight streams of 4CIF resolution currently require two instantiations of the decoders.

Table 2 – Scalable, multi-stream MPEG-4 Part 2 simple profile decoder core resources

by Hong-Swee Lim

Senior Manager, DSP Product and Solutions Marketing

Xilinx, Inc.

hong-swee.lim@xilinx.com

Advances in media encoding schemes are enabling a broad array of applications, including digital video recorders (DVRs), network surveillance cameras, medical imaging, digital broadcasting, and streaming set-top boxes. The promise of streaming media presents a series of implementation challenges, especially when processing complex compression algorithms such as MPEG-4 and MPEG-compressed video transcoding. Given the high computational horsepower required for encoding or decoding such complex algorithms, achieving optimal balance of power, performance, and cost is a significant challenge for streaming media devices.

By using FPGAs, you can differentiate your standard-compliant systems from your competitor's products and achieve the optimal balance for your application. With the MPEG-4 compression scheme, for example, it is possible to offload the IDCT (inverse discrete cosine transform)

portion of the algorithm from an MPEG processor to an FPGA to increase the processing bandwidth. IDCT (and DCT at the encoder) can be implemented extremely efficiently using FPGAs, and optimized IP cores are readily available to include in MPEG-based designs.

By integrating various IP cores together with the IDCT core, you can develop a low-cost, single-chip solution that increases processing bandwidth and gives higher quality images than your competitor's ASSP-based solution.

To help you accelerate your system design, Xilinx offers the Video Starter Kit (VSK) 4VSX35. The VSK is an all-digital platform for real-time video/image acquisition, processing, and display. It integrates the power of hardware-accelerated processing as well as an embedded PowerPC<sup>TM</sup> core for the transmission of high-resolution digital video over lower bandwidths, or for processing network protocol stack and control functions.

## Xilinx Video Starter Kit 4VSX35

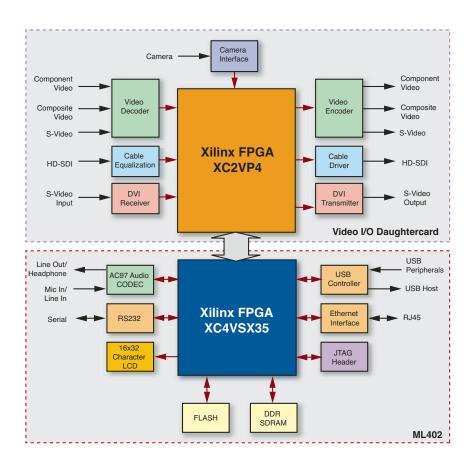

The Xilinx® VSK 4VSX35 allows you to jump-start your high-performance audio, video, and imaging processing designs. At

the heart of the VSK are two highly programmable Xilinx FPGAs (XC2VP4 and XC4VSX35), video encoder, video decoder, AC97 CODEC, and a wide range of video interfaces.

Figure 1 illustrates the VSK's primary components, peripherals, and available I/O.

The VSK comprises three major hardware components: a Xilinx ML402-SX35 board; 752 x 480-pixel RGB progressive scan CMOS image-sensor camera with a frame rate as high as 60 frames per second (fps); and video I/O daughtercard (VIODC). The VIODC is connected to the ML402-SX35 board through the Xilinx Generic Interface (XGI), while the CMOS camera is connected to the VIODC through the serial LVDS interface.

The video encoder is a high-speed, video digital-to-analog converter. It has three separate 10-bit-wide input ports that accept data in high- or standard-definition video formats. It also controls the insertion of appropriate synchronization signals; external horizontal, vertical, and blanking signals; or EAV/SAV timing codes for all standards.

The video decoder is a high-quality, single-chip, multi-format video decoder that

automatically detects and converts PAL, NTSC, and SECAM standards in the form of composite, S-Video, and component video into a digital ITU-R BT.656 format. The advanced and highly flexible digital output interface enables performance video decoding and conversion in line-locked clock-based systems. This makes the VSK ideally suited for a broad range of applications with diverse video characteristics, including broadcast sources, security and surveillance cameras, and professional video systems. Figure 2 shows a block diagram of the Video Starter Kit.

With the video encoder, video decoder, DVI receiver, DVI transmitter, and camera supporting a two-wire serial I<sup>2</sup>C-compatible interface, all of these devices can be controlled through an I<sup>2</sup>C master core located either in the XC4VSX35 or XC2VP4 device.

The flexibility of the VSK architecture makes it suitable as a development platform for a variety of multimedia, video, and imaging applications, which include:

- Medical imaging

- Home media gateways

- Multi-channel digital video recorders

- IP TV set-top boxes

- Video-on-demand servers

- Digital TV

- Digital camera and camcorders

- A/V broadcasts

- Network surveillance cameras

## System Generator for DSP v8.1

Converting image processing algorithms to FPGA implementations can be challenging, as the algorithms may be proven in software but not directly linked to the actual implementation. Additionally, it can be difficult to subjectively verify the implementation.

Xilinx System Generator for DSP allows for high-level mathematical verification and converts the heart of the algorithm into ready-to-use HDL, which bridges the gap from the algorithm developer to the FPGA engineer. Using System Generator and the VSK to develop and implement image-processing algorithms allows for a thoroughly verified and easily executed design. The high-level block diagram allows for easy communication between team members, resulting in less time spent crossing skill

Figure 1 - Video Starter Kit 4VSX35

boundaries when determining implementation trade-offs.

To accelerate video/imaging system development, Xilinx has developed new System Generator blocks specifically for the VSK, including:

- VIODC interface block

- Multi-port DDR memory controller block

- System-level blocks

With these pre-tested blocks, you can easily build your video/imaging system by just dragging and dropping the blocks within System Generator to construct your system, saving precious time from coding these essential interfacing blocks in HDL.

To be able to handle the enormous video data stream

11

Figure 2 - Block diagram of Video Starter Kit 4VSX35

## Video Starter Kit 4VSX35 **CMOS** MPEG-4 NTSC/PAL Video Monitor CODEC IP Camera Encoder **Processor Core** Application Audio Ethernet Processing IP RJ45 TCP/IP Stack PHY **RTOS** AC97 Custom IP MIC Hard Disk CODEC Flash SDRAM

Figure 3 - Network surveillance camera

from the VSK to the PC, another innovative high-speed hardware co-simulation through an Ethernet interface was introduced in System Generator for DSP 8.1. This interface allows high throughput with low latency, which proved to be extremely useful when building video/imaging systems in the System Generator environment.

## **Network Surveillance Camera Application**

FPGAs have historically been found in high-end professional broadcast systems and medical imaging equipment. Today FPGAs are also finding their way into high-volume products such as digital video recorders and network surveillance cameras because of their flexibility in handling a broad range of media formats such as MPEG-2, MPEG-4, H.264, and Windows Media. Their extremely highperformance DSP horsepower also makes FPGAs suitable for other challenging video and audio tasks.

Typically, a network surveillance camera product comprises three parts: a camera to convert the real-world image into a video stream; a video decoder for streams compressed into H.264, MPEG-2, or another format; and a video/image proces-

sor for de-interlacing, scaling, and noise reduction before packeting the digitized video for transmission over the Internet.

FPGAs can have many areas of responsibility within surveillance cameras, as shown in Figure 3. Bridging between standard chipsets as "glue logic" has always been a strong application of FPGAs, but many more image-processing tasks (such as color-space conversion), IDE (Integrated Drive Electronics) interface, and support for network interfaces (such as IEEE 1394) are now also commonly implemented in low-cost programmable devices.

With high-performance DSP capability inside a network surveillance camera, you can digitize and encode the video stream to be sent over any computer network. You can use a standard Web browser to view live, full-motion video from anywhere on a computer network, including over the Internet. Installation is simplified by using existing LAN wiring or wireless LAN. Features such as intelligent video, e-mail notification, FTP uploads, and local hard-disk storage provide enhanced differentiation and superior capability over analog systems.

The hard-processor core is an IBM

PowerPC 405 immersed in a Xilinx Virtex<sup>TM</sup>-II Pro<sup>TM</sup> FPGA, delivering 600 DMIPS at 400 MHz running MontaVista Linux or Wind River Systems's VxWorks real-time operating system (RTOS), as well as a network protocol stack to implement these features.

Xilinx also offers the MicroBlaze<sup>TM</sup> 32-bit RISC processor core, delivering up to 138 DMIPS at 150 MHz and 166 DMIPS at 180 MHz when used in the Virtex-II Pro and Virtex-4 devices, respectively.

## **Conclusion**

Bandwidth is precious; to make the most of it, compression schemes have steadily improved – and new algorithms push the envelope even further. As such, system-processing rates have increased over time, and real-time image processing is an ideal way to meet these requirements while removing memory overhead.

At the same time, Moore's Law has resulted in low-cost programmable logic devices, such as the new FPGAs, that provide the same functionality and performance previously found only in expensive professional broadcast products.

FPGAs provide both professional and consumer digital broadcast OEMs with real-time image processing capabilities that address the system requirements of new and emerging video applications. Compared to other technologies, FPGAs offer an unrivalled flexibility that enables you to get your products to market quickly. Remote field upgradeability means that systems can be shipped now and features, upgrades, or design fixes added later.

The VSK has been architected to reduce implementation risks, time to market, and development costs. By providing hardware and MPEG-4 IP in a pre-tested and integrated platform, you can concentrate on implementing the application-specific video and imaging functionality that is most relevant to your particular product.

For more information, visit www. xilinx.com/products/design\_resources/dsp\_central/grouping/index.htm.

# Encoding High-Resolution Ogg/Theora Video with Reconfigurable FPGAs

Once the traditional application area of custom ASICs, modern FPGAs can now handle high-performance video encoding.

by Andrey Filippov President Elphel, Inc. andrey@elphel.com

Much of the Spring 2003 issue of the *Xcell Journal* in which my article about Spartan<sup>TM</sup>-IIE-based Elphel Model 313 cameras appeared ("How to Use Free Software in FPGA Embedded Designs") was dedicated to the Xilinx® Spartan-3 FPGA. I immediately started to think about using these devices in our new generation of Elphel network cameras, but it wasn't until last year that I was finally able to start working with them.

One of the factors that slowed my company's adoption of this new technology was the fact that at first I could not find appropriate software that could handle the devices selected, as it is essential that our end users can modify our products without expensive software development tools. When I visited the Xilinx website in Summer 2004 and found that the current version of the free downloadable WebPACK<sup>TM</sup> software could handle the XC3S1000 – the largest device available in a small FT256 package – I knew it was the right time to switch to the Spartan-3 device.

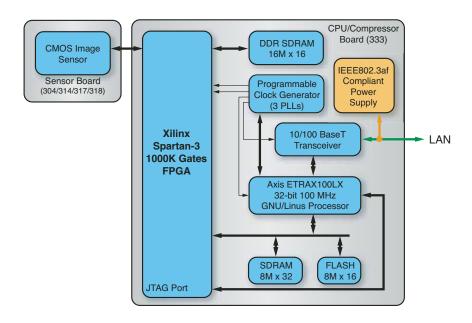

Figure 1 – Camera system block diagram

## The Camera Hardware

The new Model 333 camera (Figure 1) uses the same Linux-optimized CPU (ETRAX100LX by Axis Communications) as the earlier Model 313, but with increased system memory – 32 MB of SDRAM and 16 MB of Flash. The second major upgrade is the use of 32 MB of DDR SDRAM as a dedicated frame buffer that works in tandem with the FPGA, supplementing its processing power with high capacity and I/O bandwidth.

The Spartan-3 DDR I/O functionality made it possible to increase the memory bandwidth without increasing board size – the complete system still fits on a 1.5 x 3.5-inch four-layer board (see Figure 2). The actual board area is even smaller, as the new one is designed to fit the sealed RJ45 connectors for outdoor applications.

For the camera circuit design, the goals include combining high computational performance with small size (that also simplifies preserving high-speed signal integrity on the PCB) and providing the flexibility for the reconfigurable FPGA on the system level. For the latter, I decided to split the camera circuitry into two boards: one main board and a second containing just a sensor with minimal related components. On the main board the FPGA I/O pins go directly to the inter-board connector, so it is possi-

ble to change the pin functions (including polarity) to match the particular sensor boards. A similar solution allowed the earlier Model 313 camera to support different types of sensors (most became available after the board design). It even works in our 11-megapixel Model 323 cameras without any PCB modifications.

## Selecting the Video Encoding Technique

After the prototype camera was ready, it took just a couple of weeks to modify the code developed for the Spartan-IIE-based

connected directly to the processor I/O pins, so I could not use the software that comes with Xilinx configuration hardware. The JTAG instruction register is six bits wide, not five as it was in the Spartan-IIE devices with which I was familiar. After some trial and error, I figured that out and found that the same code could run at 125 MHz (instead of 90 MHz in the previous model) and used just 36% (not 98% as before) of available slices – plenty of room for more challenging tasks.

Of course, I had some challenging tasks in mind, as motion JPEG is not a really good option for high-resolution/high-frame-rate cameras because the amount of data to be transferred or stored is quite huge. It is a waste of network bandwidth or hard disk space when recording such video streams, as fixed-view cameras in most cases have very little difference between consecutive frames. Something like MPEG-2 could make a difference; that was the standard I was planning to implement in the camera.

But as soon as I got some books on MPEG-2 and started combing through online resources, I found another fundamental difference between MPEG and JPEG – not just that it can use the similarity between consecutive frames. Contrary to JPEG, MPEG-2 requires you to pay licensing fees for using the encoders based on this standard. The fee is small compared

Figure 2 – Camera system board

camera and to implement motion JPEG compression. Half of that time was spent trying to figure out how to configure the new FPGA with the generated bitstream. In the camera, JTAG pins of the device are

to the cost of the hardware, but it still could be a hassle and does not provide freedom for implementation.

It did not take long to find a perfect alternative – Theora, based on the VP3

codec developed by On2 Technologies (www.on2.com) and released as open-source software for royalty-free use and modifications (see www.theora.org/svn.html).

Theora is an advanced video codec that competes with MPEG-4 and other similar low-bit-rate video compression schemes. It is now supported by the Xiph.org Foundation along with Ogg, the transport layer used with Theora to deliver the video content. The bitstream format is stable enough and supported by multiple players running on different operating systems. Like JPEG and MPEG, it uses a two-dimensional 8 x 8 DCT.

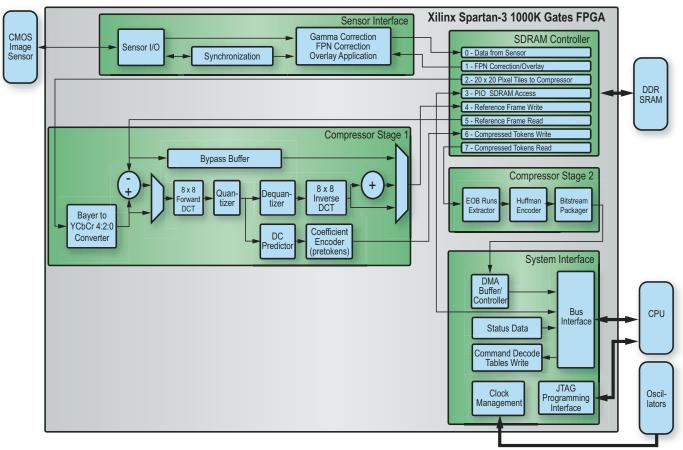

## **FPGA Implementation**

The code for the Elphel Model 333 camera FPGA is written in Verilog HDL (Figure 3). It is designed around the 8-channel SDRAM controller that uses the Spartan-3 DDR capabilities. The structure of the memory accesses and specially organized

data mapping both serve the same goal: optimizing memory bandwidth that otherwise would be a system bottleneck.

The rest of the code that currently uses two-thirds of the general FPGA resources (slices) and 20 of 24 block RAM modules includes video compression modules, a sensor, and system interfaces.

A detailed description of the camera code is available, together with the source code, at Sourceforge (https://sourceforge.net/projects/elphel).

## **Conclusion**

High-performance reconfigurable FPGAs made it possible to build a fast high-resolution low-bit-rate network camera capable of running 30 fps at a resolution of 1280 x 1024 pixels (12 fps at a resolution of 2048 x 1536). Many of the new features of the Spartan-3 devices proved to be very useful in this design: embedded multipliers for DSP functions, advanced digital clock

management, DDR I/O functions, an increased number of global clock networks for the DDR SDRAM controller, and large block RAM modules for the various tables and buffers in the camera.

The free video encoder (Theora) and completely open implementation of the camera (all software and Verilog code is provided under the GNU General Public License) makes the second most important function of Elphel products possible. You can use these cameras not only as finished products but also as universal development platforms – demonstrating the power and flexibility of the Spartan-3 family. It is possible to add your own code, rerun the tools (both for the FPGA code and the C-language camera software), and immediately try the new camera with advanced image processing implemented.

For more information, visit www.elphel.com, https://sourceforge.net/projects/elphel/, and www.theora.org.

15

Figure 3 - Block diagram of the FPGA code

# Implementing DSP Algorithms Using Spartan-3 FPGAs

This article presents two case studies of FPGA implementations for commonly used image processing algorithms — feature extraction and digital image warping.

Saul Saggin Undergraduate Student Università di Verona, Italy saul.saggin@students.univr.it

Giovanni Tommasi Undergraduate Student Università di Verona, Italy *aiovanni.tommasi@students.univr.it*

Matteo Busti Graduate Student Università di Verona, Italy matteo.busti@students.univr.it

Computer vision is a branch of artificial intelligence that focuses on equipping computers with the functions typical of human vision. In this discipline, feature tracking is one of the most important pre-processing tasks for several applications, including structure from motion, image registration, and camera motion retrieval. The feature extraction phase is critical because of its computationally intensive nature.

Digital image warping is a branch of image processing that deals with techniques of geometric spatial transformations. Warping images is an important stage in many applications of image analysis, as well as some common applications of computer vision, such as view synthesis, image mosaicing, and video stabilization in a real-time system.

In this article, we'll present an FPGA implementation of these algorithms.

## **Feature Extraction Theory**

In many computer vision tasks we are interested in finding significant feature points – or more exactly, the corners. These points are important because if we measure the displacement between features in a sequence of images seen by the camera, we can recover information both on the structure of the environment and on the motion of the viewer.

Figure 1 shows a set of feature points extracted from an image captured by a camera. Corner points usually show a significant change of the gradient values along the two directions (x and y). These points are of interest because they can be

uniquely matched and tracked over a sequence of images, whereas a point along an edge can be matched with any number of other points on the edge in a second image.

## The Feature Extraction Algorithm

The algorithm employed to select good features is inspired by Tomasi and Kanade's method, with the Benedetti and Perona approximation, considering the eigenvalues  $\alpha$  and  $\beta$  of the image gradient covariance matrix. The gradient covariance matrix is given by:

$$H = \begin{pmatrix} I_x^2 & I_x I_y \\ I_x I_y & I_x^2 \end{pmatrix}$$

where  $I_x$  and  $I_y$  denote the image gradients in the x and y directions.

Hence we can classify the structure around each pixel observing the eigenvalues of H:

No structure  $: \alpha \approx \beta \approx 0$ Edge  $: \alpha \approx 0, \beta >> 0$ Corner  $: \alpha >> 0, \beta >> 0$

Figure 1 – Feature points extracted from an image captured by a camera

Using the Benedetti and Perona approximation, we can choose the corners without computing the eigenvalues.

We have realized an algorithm that, compared to the original method, doesn't require any floating-point operations. Although this algorithm can be implemented either in hardware or software, by implementing it in FPGA technology we can achieve real-time performance.

## Input:

- 8-bit gray-level image of known size (up to 512 x 512 pixels)

- The expected number of feature points (wf)

## Output:

- List of selected features (FL). The type of the output is a 3 x N matrix whose:

- First row contains the degrees of confidence for each feature in the list

- Second row contains the x-coordinates of the feature points

- Third row contains the y-coordinates of the feature points

## Semantic of the Algorithm

In order to determine if a pixel (i, j) is a feature point (corner), we followed Tomasi and Kanade's method.

First, we calculate the gradient of the image. Hence the  $2 \times 2$  symmetric matrix  $G = [a \ b; \ b \ c]$  is computed, whose entries derive from the gradient values in a patch around the pixel (i, j).

If the minimum eigenvalue of G is greater than a threshold, then the pixel (i, j)

is a corner point. The minimum eigenvalue is computed using an approximation to avoid the square root operation that is expensive for hardware implementations.

The corner detection algorithm could be summarized as follows:

The image gradient is computed by mean of convolution of the input image with a predefined mask. The size and the values of this mask depend on the image resolution. A typical size of the mask is 7 x 7.

• For each pixel (i, j) loop:

$$a_{i,j} = \sum_{k}^{N} (I_x^k)^2$$

$$b_{i,j} = \sum_{k}^{N} I_{x}^{k} I_{y}^{k}$$

$$c_{i,j} = \sum_{k}^{N} (I_{y}^{k})^{2}$$

where N is the number of pixels in the patch and  $I_x^k$  and  $I_y^k$  are the components of the gradient at pixel k inside the patch.

•

$$P_{i,j} = (a-t)(c-t) - b^2$$

where t is a fixed integer parameter.

- If  $(P_{i,j} > 0)$  and  $(a_{i,j} > t)$ , then we retain pixels (i,j)

- Discard any pixel that is not a local maximum of P<sub>i,j</sub>

- End loop

- Sort, in decreasing order, the feature list *FL* based on the degree of confidence values and take only the first *wf* items.

## **Implementation**

With its high-speed embedded multipliers, the Xilinx® Spartan<sup>TM</sup>-3 architecture meets the cost/performance characteristics required by many computer vision systems that could take advantage of this algorithm.

The implementation is divided into four fundamental tasks:

1. Data acquisition. Take in two gradient values along the x and y axis and

- compute for each pixel three coefficients used by the characteristic polynomial. To store and read the gradient values, we use a buffer (implemented using a Spartan-3 block RAM).

- Calculation of the characteristic polynomial value. This value is important to sort the features related to the specific pixel. We implemented the multiplications used for the characteristic polynomial calculus employing the embedded multipliers on Spartan-3 devices.

- Feature sorting. We store computed feature values in block RAM and sort them step by step by using successive comparisons.

- 4. Enforce minimum distance. This is done to keep a minimum distance between features; otherwise we get clusters of features heaped around the most important ones. This is implemented using block RAMs, building a non-detect area around each most important feature where other features will not be selected.

## **Spartan-3 Theoretical Performance**

The algorithm is developed for gray-level images at different resolutions, up to 512 x 512 at 100 frames per second.

The resources estimated by Xilinx System Generator are:

- 1,576 slices

- 15 block RAMs

- 224 LUTs

- 11 embedded multipliers

The embedded multipliers and extensive memory resources of the Spartan-3 fabric allow for an efficient logic implementation.

## **Applications of Feature Extraction**

Feature extraction is used in the front end for any system employed to solve practical control problems, such as autonomous navigation and systems that could rely on vision to make decisions and provide control. Typical applications include active video surveillance, robotic arms motion,

measurement of points and distances, and autonomous guided vehicles.

## **Image Warping Theory**

Digital image warping deals with techniques of geometric spatial transformations.

The pixels in an image are spatially represented by a couple of Cartesian coordinates (x, y). To apply a geometric spatial transformation to the image, it is convenient to switch to homogeneous coordinates, which allow us to express the transformation by a single matrix operation. Usually this is done by adding a third coordinate with value 1 (x, y, 1).

In general, such transformation is represented by a non-singular 3 x 3 matrix H and applied through a matrix-vector multiplication to the pixel homogeneous coordinates:

served. Six parameters are required to define an affine transformation.

## Image Warping Algorithms

There are two common ways to warp an image:

- Forward mapping

- Backward mapping

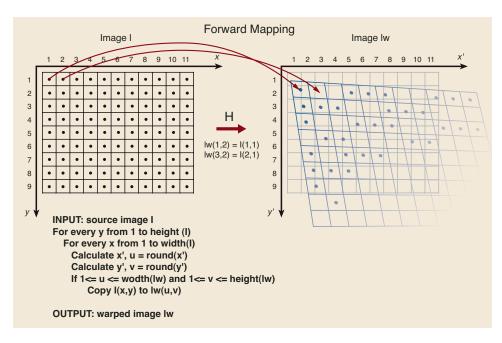

Using forward mapping, the source image is scanned line by line and the pixels are copied to the resulting image, in the position given by the result of the linear system shown in equation (2). This technique is subject to several problems, the most important being the presence of holes in the final image in the case of significant modification of the image (such as rotation or a scaling by a factor greater than 1) (Figure 2).

The backward mapping approach gives

$$\begin{bmatrix} H_{1,1} & H_{1,2} & H_{1,3} \\ H_{2,1} & H_{2,2} & H_{2,3} \\ H_{3,1} & H_{3,2} & H_{3,3} \end{bmatrix} \bullet \begin{bmatrix} x \\ y \\ 1 \end{bmatrix} = \begin{bmatrix} H_{1,1}x + H_{1,2}y + H_{1,3} \\ H_{2,1}x + H_{2,2}y + H_{2,3} \\ H_{3,1}x + H_{3,2}y + H_{3,3} \end{bmatrix} = \begin{bmatrix} x' \\ y' \\ w' \end{bmatrix} = \begin{bmatrix} x' \\ w' \\ w' \end{bmatrix} \Longrightarrow (x'/w', y'/w')$$

(1)

The matrix H, called homography or collineation, is defined up to a scale factor (it has 8 degrees of freedom). The transformation is linear in projective (or homogeneous) coordinates, but non-linear in Cartesian coordinates.

The formula implies that to obtain Cartesian coordinates of the resulting pixel we have to perform a division, an operation quite onerous in terms of time and area consumption on an FPGA. For this reason, we considered a class of spatial transformations called "affine transformations" that is a particular specialization of homography. This allows us to avoid the division and obtain good observational results:

better results. Using the inverse transformation A-1, we scan the final image pixel by pixel and transform the coordinates. The result is a pair of non-integer coordinates in the source image. Using a bilinear interpolation of the four pixel values identified in the source image, we can find a value for the final image pixel (see Figure 3).

This technique avoids the problem of holes in the final image, so we adopted it as our solution for the hardware implementation.

## **Implementation**

Software implementations of this algorithm are well-known and widely used in applica-

$$\begin{bmatrix} A_{1,1} & A_{1,2} & A_{1,3} \\ A_{2,1} & A_{2,2} & A_{2,3} \\ 0 & 0 & 1 \end{bmatrix} \bullet \begin{bmatrix} x \\ y \\ 1 \end{bmatrix} = \begin{bmatrix} A_{1,1}x + A_{1,2}y + A_{1,3} \\ A_{2,1}x + A_{2,2}y + A_{2,3} \\ 1 \end{bmatrix} = \begin{bmatrix} x' \\ y' \\ 1 \end{bmatrix} \Longrightarrow (x', y') \quad (2)$$

Affine transformations include several planar transformation classes as rotation, translation, scaling, and all possible combinations of these. We can summarize the affine transformation as every planar transformation where the parallelism is pre-

tions where a personal computer or workstation is required. A hardware implementation requires further work to achieve efficiency constraints on an FPGA.

Essentially, the process can be divided in two parts: transformation and interpo-

lation. We implemented the first as a matrix-vector multiplication (2), with four multipliers and four adders. The second is an approximation of the real result of the interpolation: we weighted the four pixel values approximating the results of the transformation with two bits after the binary point. Instead of performing the calculations given by the formula, we used a LUT to obtain the pixel final value, since we divided possible results of the interpolation into a set of discrete values.

## **Spartan-3 Theoretical Performance**

We designed the algorithm using System Generator for DSP, targeting a Spartan-3 device. We generated the HDL code and synthesized it with ISE<sup>TM</sup> design software, obtaining a resource utilization of:

- 744 slices (1,107 LUTs)

- 164 SRL16

- 4 embedded multipliers

The design can process up to 46 fps (frames per second) with 512 x 512 images. Theoretical results show a boundary of 360+fps in a Spartan-3-based system.

## **Applications of Image Warping**

Image warping is typically used in many common computer vision applications, such as view synthesis, video stabilization, and image mosaicing.

Image mosaicing deals with the composition of sequence (or collection) of images after aligning all of them respective to a common reference frame. These geometrical transformations can be seen as simple relations between coordinate systems.

By applying the appropriate transformations through a warping operation and merging the overlapping regions of a warped image, we can construct a single panoramic image covering the entire visible area of the scene. Image mosaicing provides a powerful way to create detailed three-dimensional models and scenes for virtual reality scenarios based on real imagery. It is employed in flight simulators, interactive multi-player games, and medical image systems to construct true scenic panoramas or limited virtual environments.

Figure 2 – Forward mapping with a scaling factor greater than one

Figure 3 – Backward mapping with a scaling factor greater than one

## Conclusion

The challenge is to design efficient, effective, and reliable vision modules with the highest possible reliability.

Ultimodule, a Xilinx XPERTS partner, and the VIPS Laboratory at the Università di Verona have defined a foundation platform for computer vision using Ultimodule's system-on-module family. The platform provides a stereovision system for real-time extraction of three-dimensional data and a real-time image-processing engine implementing most of the algorithms required when an application relies on vision to make decisions and provide control.

The platform supports applications that require high performance and robust vision analysis, both in qualitative and computational terms (real-time), including active video surveillance, robotic arm motion and control, autonomous vehicle navigation, test and measurement, and hazard detection. The platform provides modules with all required system control logic, memory, and processing hardware, together with the application software. Interconnecting modules allow fast development of a complex architecture.

The platform leverages Xilinx Spartan-3 devices, which are an optimal choice for image processing IP cores because of their flexibility, high performance, and DSP-oriented targeting. The Spartan-3 family provides a valid, programmable alternative to ASICs. This characteristic, coupled with its low cost structure, adds considerable value when time to market is crucial.

For more information about feature extraction, you can e-mail the authors at paolo.giacon@students.univr.it or saul. saggin@students.univr.it. For more information about image warping, you can e-mail matteo.busti@students.univr.it or giovanni. tommasi@students.univr.it.

We are grateful for the support from our advisor, Professor Murino, in the Vision, Image Processing, and Sound (VIPS) Laboratory in the Dipartimento di Informatica at the Università di Verona, and contributions from Marco Monguzzi, Roberto Marzotto, and Alessandro Negrente.

19

# Using FPGAs in Wireless Base Station Designs

Wireless base station design trends benefit from Virtex-4 device features.

by David Gamba

Senior Manager, Strategic Solutions Marketing

Xilinx, Inc.

david.gamba@xilinx.com

Wireless infrastructure revenue continues to experience phenomenal growth, increasing from approximately \$27 billion in 2003 to an estimated \$35 billion in 2004. Industry analysts are predicting that 2004 will be the peak revenue year, as forecasts show the revenue figure dropping back to \$27 billion in 2005, eventually settling in to the \$10-\$15 billion range by the end of the decade. This revenue decline is driven both by lower prices as well as a drop in base station deployments, from nearly 500,000 stations in 2004 to less than 200,000 in 2010.

As the industry transitions from a highgrowth phase to a more mature state, cost pressures will increasingly mount in all facets of the infrastructure, including the wireless base station. Next-generation base station deployments must conquer the challenge of continually reducing cost (as measured by cost per channel) while adding functionality to support new services, protocols, and changing subscriber usage patterns. To begin addressing this challenge, wireless base station designs are shifting from ASIC technology to more readily available off-the-shelf components such as FPGAs. This shift is driven both by declining annual base station unit volumes as well as FPGA technology improvements that increase processing power and enable a much lower cost per channel.

The migration to FPGAs is not just an attempt to reduce costs and create a common platform to achieve commoditization – it is also being driven by time-to-market pressures, along with the need to make in-

more manageable, avoiding some of the multi-million dollar inventory obsolescence issues that base station manufacturers have faced with ASIC solutions fabricated to support the 3G launch.

## Standardizing the Wireless Base Station

Another significant step taken by the wireless industry is the launch of industry organizations focused on standardizing the non-differentiated features inside a base station. The most notable development for Xilinx is the migration to a standardized high-speed serial interconnect solution

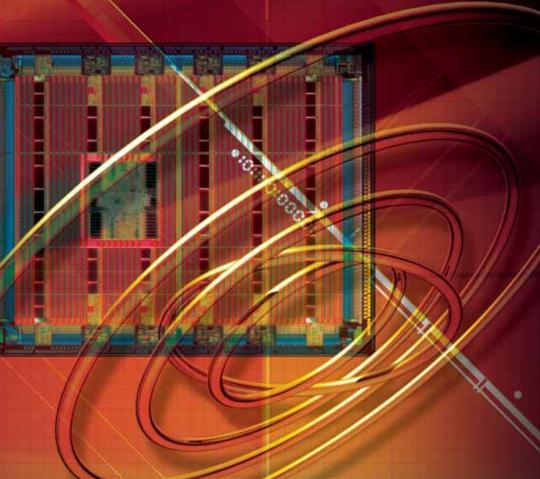

Figure 1 – Wireless base station module block diagram

field upgrades of base station deployments. This shift away from ASICs has enabled significant new design opportunities for Xilinx<sup>®</sup> Virtex-4<sup>TM</sup> devices to fill the void.

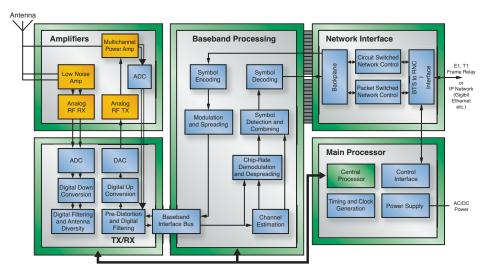

## **Wireless Base Station Module Building Blocks**

Inside a wireless base station are fairly distinct module blocks performing different functions, such as radio, baseband processing, transport network interfacing, and control (Figure 1). Traditional base station designs used ASICs – along with DSPs and other discrete components – to implement these various architectural features and functions.

This design approach is rapidly giving way to more cost-effective and flexible designs that use FPGAs. With lower costs and increased flexibility, product delivery is accelerated and inventory control is much

between the different base station module blocks, such as the Open Base Station Architecture Initiative (OBSAI) Reference Point 3 (RP3) and Common Public Radio Interface (CPRI) interconnects for baseband and radio module connectivity.

Many leading base station manufacturers are members of these organizations and are rapidly preparing to adopt one of these two standard interconnect solutions in their upcoming design implementations. Xilinx is fully prepared to support these standards, and has both OBSAI and CPRI IP solutions and reference designs available for implementing in Virtex-II Pro<sup>TM</sup>, Virtex-II Pro X, and Virtex-4 FX FPGA devices, using the integrated RocketIO<sup>TM</sup> multi-gigabit tranceivers (MGTs) in association with the logic building blocks.

## **Extending Current Design Lifecycles**

Standardization is the first step towards the commoditization of base station design and will eventually lead to a phasing out of ASICs from wireless base stations. In the interim, companies are inserting discrete devices next to their current ASICs to support new functionality that cannot be added in a timely or cost-effective manner to the current design.

For instance, the Third Generation Partnership Project (3GPP), which is a collaboration agreement between several telecommunications bodies, is actively creating additional standards for the wireless industry. 3GPP has added a high-speed downlink packet access (HSDPA) feature as a new Universal Mobile Telecommunications System (UMTS) requirement in its latest baseband processing specification, Release 5, for Wideband Code Division Multiple Access (W-CDMA).

ASICs in current base stations do not support this new variant for UMTS. This creates a hole in the service offerings for UMTS, which forecasters are predicting will represent approximately 80% of the wireless traffic in the next few years. This deficiency must be addressed before future field deployments, and it can be – without exceeding the system power budget – by using a Virtex-4 LX device next to the ASIC, implementing HSDPA using the available Xilinx HSDPA IP offering.

## **Next-Generation Base Station Designs**

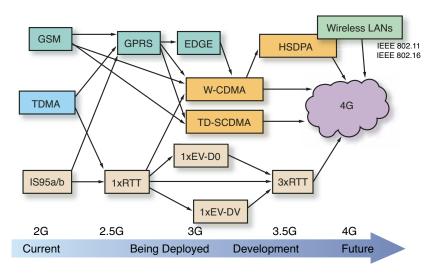

But adding external devices to patch design holes created by existing ASIC designs limitations is purely a stopgap solution. Future base station designs must be able to quickly adapt to changes in subscriber traffic patterns, as well as support the upcoming convergence of new services and emerging cellular technologies such as W-CDMA, TD-SCDMA, EDGE, 1xEV-DO, and WiMAX.

As shown in Figure 2, the amount of cellular technologies is expected to continue to proliferate, leading base stations down the path of having to support many more technologies. Current issues such as

Figure 2 – Mobile technology roadmap

multi-user detection and antenna selection will be augmented by new technical challenges, such as channel provisioning and base station tuning, that will need to be resolved appropriately to reduce a service provider's customer turnover. The fundamental expectation to receive the same high-quality wireless service wherever a customer roams must be completely addressed.

These customer expectations would benefit from substantial flexibility in the base station. Fortunately, many of the baseband processing functions and radio module functions are well suited for implementation in Virtex-4 devices, taking advantage of the integrated XtremeDSP<sup>TM</sup> slices in the product architecture.

For instance, quite a few baseband processing tasks – such as call initiation and set-up and multi-path signal detection and monitoring – are heavily based on mathematical algorithms. You can very efficiently implement these algorithms by using the integrated multiplier capabilities available in Virtex-4 devices, along with the readily available intellectual property components such as the Random Access Channel (RACH), Searcher, and 3G Turbo Convolutional Codecs (3GTCC) that Xilinx has imple-

Xilinx Baseband Intellectual Property Offerings IP Offering Application Increases downlink data transmission rate to a peak of 14.4 Mbps **HSDPA** RACH Receiver path preamble detection (specified by W-CDMA) Multi-path delay estimate for each subscriber Searcher 3G TCC Forward error correction Xilinx Radio Intellectual Property Offerings IP Offering Application DPD Signal conditioning to enable use of lower cost RF power amplifiers CFR Signal amplitude conditioning to enable increased RF power amplifier efficiency DUC Baseband signal modulation for digital-to-analog converter input Receiver signal modulation for analog-to-digital converter input DDC

Table 1 – Xilinx baseband and radio IP offerings

mented as reference designs to demonstrate these capabilities.

The integrated DSP capability in the Virtex-4 SX device enables a very low power implementation of these functions. Radio functions can be expanded by using a Virtex-4 SX device to enable more channel support.

Several enabling pieces of intellectual property targeted at radio functions, such as digital pre-distortion (DPD), crest factor reduction (CFR), and digital up/down conversion (DUC/DDC), are supported by the Virtex-4 SX device. Not only does this help increase in the number of channels supported in a base station, but it also helps reduce the cost per channel. Table 1 gives an overview of the different capabilities offered by Xilinx baseband and radio module IP offerings.

## System Generator for DSP Development Tool

Xilinx complements its Virtex-4 product offerings with the System Generator for DSP tool. This is a complete integrated DSP design environment that simplifies the development, debug, and verification of high-performance DSP designs targeting wireless base stations. This tool also helps designers interface with complementary general-purpose and DSP processors used in wireless base station designs.

System Generator for DSP provides high-level abstractions that are automatically compiled into Virtex-4 devices at the push of a button, with no loss in performance over designs implemented in lower-level languages such as VHDL. System Generator is part of the XtremeDSP solution, which combines state-of-the-art FPGAs, design tools, intellectual property cores, and design and education services.

## **Conclusion**

To learn more about the key markets and end applications of Xilinx wireless solutions, visit www.xilinx.com/esp/, or e-mail 3g@xilinx.com. For more details about Virtex-4 FPGAs, visit www.xilinx.com/virtex4/. And for more details on System Generator for DSP or other pieces of the Xilinx DSP solution, visit www.xilinx.com/dsp/.

DaVinci, Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1140A0 © 2005 TI

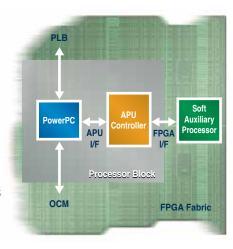

## Accelerated System Performance with APU-Enhanced Processing

The Auxiliary Processor Unit (APU) controller is a key embedded processing feature in the Virtex-4 FX family.

by Ahmad Ansari Senior Staff Systems Architect Xilinx, Inc. ahmad.ansari@xilinx.com

Peter Ryser Manager, Systems Engineering Xilinx, Inc. peter.ryser@xilinx.com

Dan Isaacs

Director, APD Embedded Marketing

Xilinx, Inc.

dan isaacs@xilinx.com

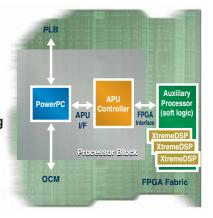

The APU controller provides a flexible high-bandwidth interface between the reconfigurable logic in the FPGA fabric and the pipeline of the integrated IBM<sup>TM</sup> PowerPC<sup>TM</sup> 405 CPU. Fabric co-processor modules (FCM) implemented in the FPGA fabric are connected to the embedded PowerPC processor through the APU controller interface to enable user-defined configurable hardware accelerators. These hardware accelerator functions operate as extensions to the PowerPC 405, thereby offloading the CPU from demanding computational tasks.

## **APU Instructions**

The APU controller allows you to extend the native PowerPC 405 instruction set with custom instructions that are executed by the soft

FCM; the primary capabilities are shown in Figure 1. This provides a more efficient integration between an application-specific function and the processor pipeline than is possible using a memory-mapped coprocessor and shared bus implementation.

The instructions supported by the APU are classified into three main categories:

- User-defined instructions (UDI)

- PowerPC floating-point instructions

- APU load/store instructions

The UDIs are programmed into the controller either dynamically through the PowerPC 405 device control register (DCR) or statically when the FPGA is configured through its bitstream. The APU controller allows you to optimize your system architecture by decoding instructions either internally or in the FCM.

The floating-point unit (FPU) is an example of an FCM. The PowerPC floating-point instruction set is decoded in the APU controller, whereas the computational functionality is implemented in the FPGA fabric. To support FPUs with different complexities, the APU controller allows you to select subgroups of the PowerPC floating-point instructions. These instructions are executed in the FCM while other subgroups of instructions are either computed through software FPU

emulation or ignored completely. This finetuning optimizes FPGA resources while accelerating the most critical calculations with dedicated logic.

The APU controller also decodes high-performance load and store instructions between the processor data cache or system memory and the FPGA fabric. A single instruction transfers up to 16 bytes of data – four times greater than a load or store instruction for one of the general purpose registers (GPR) in the processor itself. Thus, this capability creates a low-latency and high-bandwidth data path to and from the FCM.

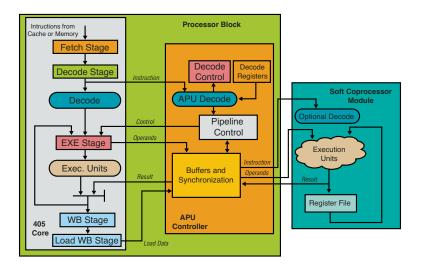

## **APU Controller Operation**

Figure 2 identifies the key modules of the APU controller and the 405 CPU in relation to the FCM soft coprocessor module implemented in FPGA logic. To explain the operation of the APU controller and the processor interactions related to the execution units in soft logic, we can trace the step-by-step sequence of events that occur when an instruction is fetched from cache or memory.

Once the instruction reaches the decode stage, it is simultaneously presented to both the CPU and APU decode blocks. If the instruction is detected as a CPU instruction, the CPU will continue to execute the instruction as it would normally. Otherwise, within the same cycle, the CPU

## Extends PPC 405 Instruction Set

- Floating Point Support (with soft auxiliary processor)

- User-Defined Instructions

## • Offloads CPU-Intensive Operations

- Matrix Calculations

- Video Processina

- Floating-Point Mathematics

- 3D Data Processing

## • Direct Interface to HW Accelerators

- High Bandwidth

- Low Latency

Figure 1 – APU expanded processing capabilities

Figure 2 – APU controller processing operative block diagram

will look for a response from the APU controller. If the APU controller recognizes the instruction, it will provide the necessary information back to the CPU.

If the APU controller does not respond within that same cycle, an invalid instruction exception will be generated by the CPU. If the instruction is a valid and recognized instruction, the necessary operands are fetched from the processor and passed to the FCM for processing.

Because the PowerPC processor and the FCM reside in two separate clock domains, synchronization modules of the APU controller manage the clock frequency difference. This allows the FCM to operate at a slower frequency than the processor. In this instance, the APU controller would receive the resultant data from the coprocessor and

at the proper execution time send the data back to the processor. The APU controller knows in advance, based on instruction type, if or when it will get the result.

## Autonomous and Non-Autonomous Instructions

Two major categories of instructions exist: autonomous and non-autonomous. For autonomous instructions, the CPU continues issuing instructions and does not stall while the FCM is operating on an instruction. This overlap of execution allows you to achieve high performance through techniques such as software pipelining.

On the other hand, during the synchronized execution, the CPU pipeline stalls while the FCM is operating on an instruction. This feature allows you to

implement synchronization semantics to pace the software execution with the hardware FCM latency.

Non-autonomous instruction types are further divided into blocking and non-blocking. If blocking, asynchronous exceptions or interrupts are blocked until the FCM instruction completes. Otherwise, if non-blocking, the exception or interrupt is taken and the FCM is flushed.

## Software Description

Software engineers can access the FCM from within assembler or C code. On one side, Xilinx has enabled the GCC compiler (which is contained in the Embedded Development Kit) to generate code that uses an FCM floating-point unit to calculate floating-point operations. Furthermore, assembler mnemonics are available for UDIs and the pre-defined load/store instructions, enabling you to place hardware-accelerated functions into the regular program flow. For the ultimate level of flexibility, you can define your own instructions designed specifically for the hardware functionality of the FCM.

You can easily use the pre-defined load/store instructions through high-level C macros. For example, in an application where the FCM is used to convert pixel data into the frequency domain, 8 pixels of 16 bits are transferred from main memory to an FCM register with a simple program:

unsigned short pixel\_row[8]; // 8 pixels, each pixel has a size of 16 bits

lqfcm(0, pixel\_row); // transfer a row of pixels to FCM register zero

The quadword load operation maintains cache coherency as the data is moved through the cache, if caching is enabled for the corresponding address space.

The FCM operation on the pixel data can start on an explicit command; for example, a UDI. However, for many applications the operation starts immediately after the FCM hardware detects the completion of the load instruction.

The latter approach has many advantages:

• Simple software – A load operation moves the data from the memory to

the FCM and starts the operation. A subsequent store instruction retrieves the result of the operation and stores it back to main memory.

- High data transfer rates Quadword load and store operations take just a few cycles to complete. A single operation moves 16 bytes within that timeframe.

- Low latency FCM load operations are simple to use. The processor completes the operation in a single cycle.

The principle of the RISC architecture uses a number of simple instructions on data stored in general-purpose registers (GPR) to compute complex operations. User-defined instructions fall into this category but take the concept a step further in that the system architect defines the complexity of the operation on data stored in GPRs and FCM registers (FCR). Again, from a software point of view, the engineer codes user-defined instructions through C macros. GCC recognizes mnemonics such as udi0fcm as a user-defined operation of the general form:

## udi0fcm<FCRT5/RT5>,<FCRA5/RA5/imm>, <FCRB5/RB5/imm>

The target of the operation is either a GPR or an FCR. The operands are either GPRs, FCRs, immediate values, or a combination. As you can see, the semantics are not defined by the instruction and depend on your intentions and the implementation in the FCM.

This code sequence demonstrates the use of a user-defined instruction as an example of a complex add operation:

```

struct complex {

int r, i;  // 32 bit integer for real

and imaginary parts

};

complex a, b, r;

Idfcm(0, &a);  // load complex number a

into FCM register 0

Idfcm(1, &b);  // load complex number b

into FCM register 1

udi0fcm(2, 1, 0); // udi0fcm computes r = a

+ b, where r is stored in FCM register 2

stdfcm(&r, 2);  // store complex result

from FCM register 2 to variable r

```

26

To increase the readability of the code, you can redefine the user-defined instruction with regular C preprocessor constructs. Instead of using the udi0fcm() macro, you can redefine it to a more comprehensible complex\_add() macro with #define complex\_add(r, a, b) udi0fcm(r, a, b) and change the listing to call complex\_add(2, 1, 0) instead of udi0fcm(2, 1, 0).

Therefore, system architects can partition their tasks into hardware- and software-executed pieces that are efficiently and precisely interfaced to one another through the use of the APU controller. This partitioning can be done statically during the initial system configuration or dynamically during the program execution. Using the direct processor/FPGA coupling presented by the APU controller and its high throughput interfaces, hardware/software synchronization is greatly simplified and performance significantly improved.

## **Accelerating System Performance**

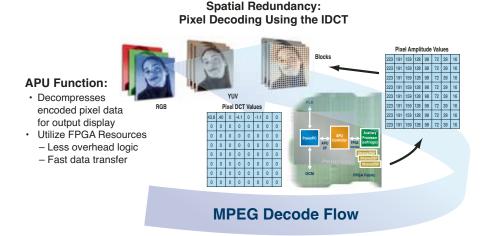

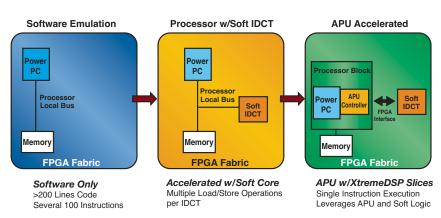

The following examples showcase key advantages the APU provides based on two different scenarios. The first scenario is essentially a benchmarking comparison of a finite impulse response (FIR) filter using a soft FPU core, implemented as an FCM attached directly to the APU controller (as compared to software emulation used to calculate the filter function). The second scenario implements a two-dimensional

inverse discrete cosine transform (2D-IDCT) typically used as one of the processing blocks in MPEG-2 video decompression, again compared to emulating the 2D-IDCT function in software.

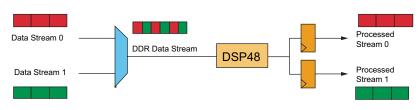

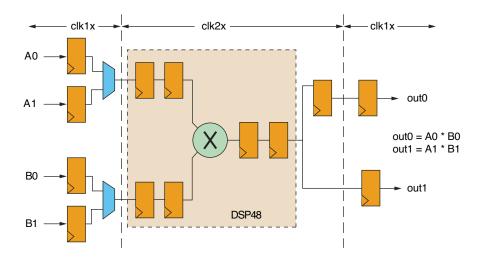

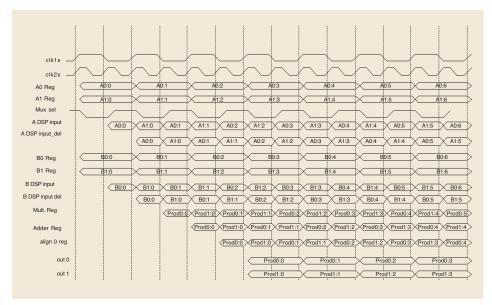

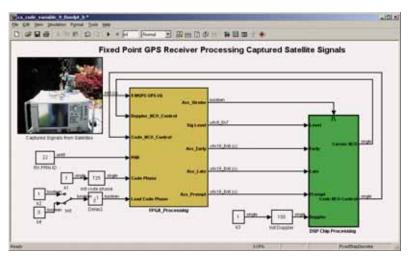

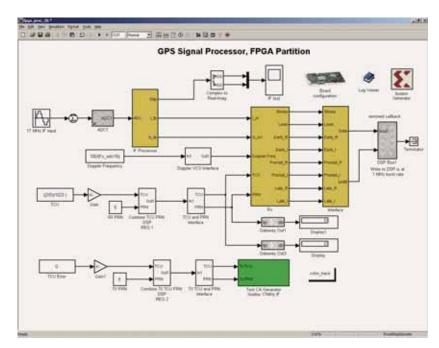

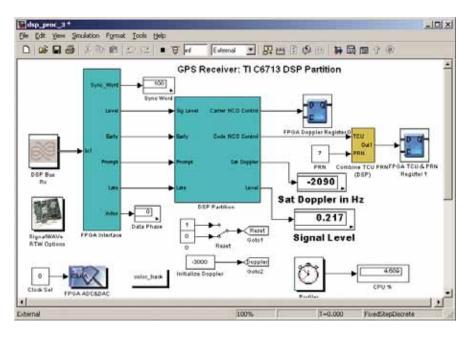

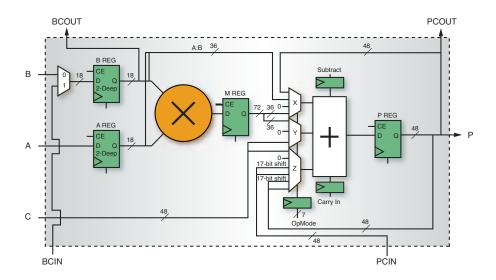

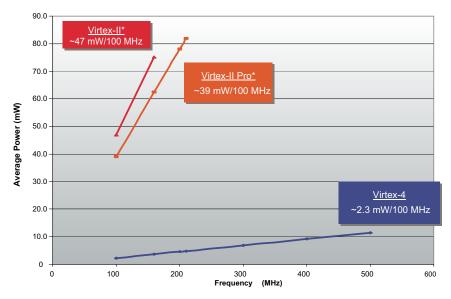

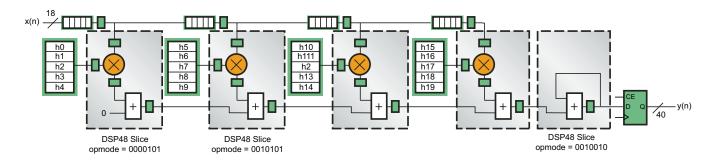

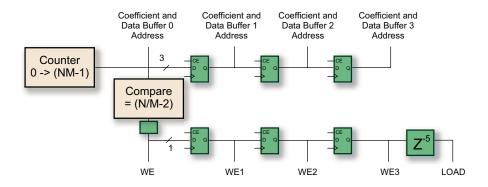

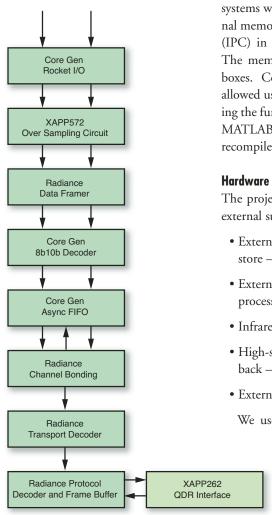

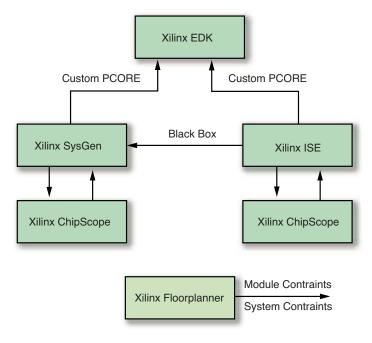

The two use cases are different in that the FPU implements a set of registers in the FPGA fabric upon which the FPU instructions operate. The 2D-IDCT only requires load and store operations, while the functionality of the operation on the data stream is fixed. In either case the operations are complex enough to justify offloading into the FPGA fabric.