# magazine Embedded

EMBEDDED SOLUTIONS FOR PROGRAMMABLE LOGIC DESIGNS

### Support Across The Board.

#### Xilinx Spring 2006 SpeedWay Series

- Xilinx MicroBlaze<sup>™</sup>

Development Workshop

- Xilinx PowerPC®

Development Workshop

- Xilinx Embedded Software Development Workshop

- Introduction to FPGA Design Workshop

- Creating a Low-Cost PCI Express Design Workshop

- Embedded Networking with Xilinx FPGAs Workshop

- Xilinx DSP Development Workshop

- Xilinx DSP for Video Workshop

- Improving Design Performance Workshop

### Accelerate Your Learning Curve on New Application Solutions

Avnet Electronics Marketing offers a series of technical, hands-on SpeedWay Design Workshops<sup>TM</sup> that will dramatically accelerate your learning curve on new application solutions, products and technologies like the Philips-Xilinx PCI Express two-chip solution. Our FAE presenters use detailed laboratory exercises and Avnet developed design kits to reinforce the key topics presented during the workshops, ensuring that when you leave the class you will be able to apply newly learned concepts to your current design.

- Every workshop features an Avnet developed design kit

- Workshops are systems and solutions focused

- Design alternatives and trade-offs for targeted applications are discussed

For more information about upcoming Xilinx SpeedWay workshops, visit:

www.em.avnet.com/xilinxspeedway

Enabling success from the center of technology™

1 800 332 8638 www.em.avnet.com

## **Endless Possibilities**

Welcome to our third edition of Xilinx *Embedded Magazine*. As we prepared this issue, the theme for this year's Embedded Systems Conference – "Five Days, One Location, Endless Possibilities" – resonated with the array of potential articles. Simply stated, we seemed to have endless possibilities for our embedded solutions to choose from and to share with you.

To capitalize on this theme, our ease-of-use initiative continues with Xilinx® Platform Studio and the Embedded Development Kit (EDK), as we recently released our latest version, 8.1i. This comes on the heels of EDN's recognition of our 32-bit MicroBlaze<sup>TM</sup> soft-processor core as one of the "Hot 100 Products of 2005." Taken together, the MicroBlaze core, the industry-standard

PowerPC<sup>TM</sup> core embedded in our Virtex<sup>TM</sup> family of FPGAs, and a growing list of IP and supported industry standards offer more options than ever to create, debug, and launch an embedded system for production.

The latest version of our kit serves one of the greatest appeals that the embedded solution holds for our FPGA customers – to create a "just-what-I-needed" processor subsystem that "just works." In so doing, our customers can concentrate on the added value that differentiates their products in their marketplace. Here again, "endless possibilities" resonates with unlimited design flexibility.

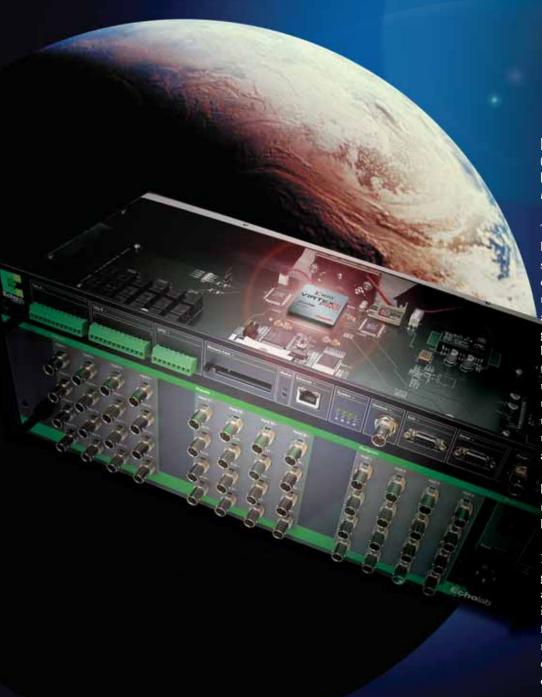

In this issue of *Embedded Magazine* we offer a collection of diverse articles unlocking the endless possibilities with Xilinx platforms. We welcome industry icon Jim Turley and his clever insight regarding shifts in the embedded industry with his article "Change Is Good." In addition, our partners Echolab, Impulse, PetaLogix, Poseidon, Teja, Avnet, and Nu Horizons highlight their latest innovations for our embedded platforms. Our own experts provide tutorials on the latest release of EDK 8.1, along with a background look at the newly launched Xilinx ESL Initiative.

Join us as we plumb the depths of these exciting new embedded solutions. I'm sure you'll find our third edition of *Embedded Magazine* informative and inspiring as we endeavor to help you unlock the power of Xilinx programmability. The advantages are enormous, the possibilities ... endless!

Mark Aaldering

Vice President

Embedded Processing

& IP Divisions

Time to market, developer and programmer productivity, choice in fabrication facilities and EDA retooling costs for smaller and smaller geometries are all putting tremendous strain on system development groups around the globe.

Enter IBM. Whether your design priorities are low power or high performance, or both, IBM's Power Architecture™ microprocessors and cores can help you accelerate innovation in your designs. Find out what the world's fastest supercomputer, Internet routers and switches, the Mars Rover, and the next generation game consoles all have in common. For more information visit ibm.com/power

#### CONTENTS

| Welcome  | 3 |

|----------|---|

| Contents | 5 |

#### ARTICLES

| New EDK 8.1 Simplifies Embedded Design                                     |

|----------------------------------------------------------------------------|

| Change Is Good                                                             |

| Implementing Floating-Point DSP                                            |

| ESL Tools for FPGAs.                                                       |

| Algorithmic Acceleration Through Automated Generation of FPGA Coprocessors |

| Generating Efficient Board Support Packages.                               |

| Bringing Floating-Point Math to the Masses                                 |

| Packet Subsystem on a Chip                                                 |

| Accelerating FFTs in Hardware Using a MicroBlaze Processor                 |

| Eliminating Data Corruption in Embedded Systems                            |

| Boost Your Processor-Based Performance with ESL Tools                      |

#### **CUSTOMER SUCCESS**

| WEBCASTS |  |

|----------|--|

Unveiling Nova......51

#### **BOARDS**

| Development Kits Accelerate | Embedded Design | <br>61 |

|-----------------------------|-----------------|--------|

#### **PRODUCTS**

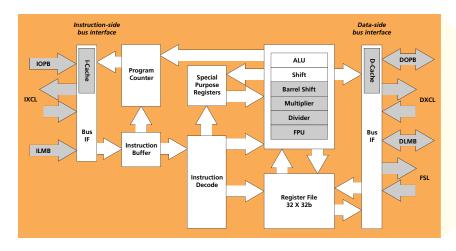

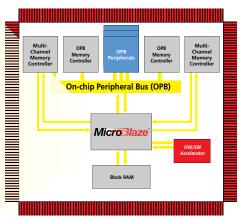

| MicroBlaze – The Low-Cost and Flexible Processing Solution |  | 6 | 4 |

|------------------------------------------------------------|--|---|---|

|------------------------------------------------------------|--|---|---|

# New EDK 8.1 Simplifies Embedded Design

Platform Studio enhancements streamline processor system development.

by Jay Gould

Product Marketing Manager,

Xilinx Embedded Solutions Marketing

Xilinx, Inc.

jay.gould@xilinx.com

After achieving an industry milestone, what's next? In 2005, the Xilinx® Platform Studio tool suite (XPS) included in the Embedded Development Kit (EDK) won the IEC's DesignVision Award for innovation in embedded design. The revolutionary approach of design wizards brought abstraction and automation to an otherwise manual and error-prone development process for embedded system creation.

The year 2006 brings a new version 8.1 update to the Platform Studio tool suite, with an emphasis on simplifying the development process and providing a more visible environment. The result is a shortened learning curve for new users and an even more complete and easier-to-use environment for existing designers.

### Xilinx has updated the main user interface of Platform Studio to provide an intuitive feel for both hardware and software engineers...

Just getting a complex design started can take a significant amount of time out of a critical schedule, so Xilinx started with a premise that the first steps to a working core design should be automated. The Xilinx Base System Builder design wizard within the Platform Studio tool suite provides a step-by-step interface to walk you through the critical first stages of a design. Design wizards are a great innovation because they can provide a quick path to a working core design even if you have minimal expertise. The "smarter" the install wizard is, the fewer issues occur, and the less experience you need to have.

Pre-configured hardware/software development kits are also extremely valuable for getting a design "off the napkin" and into a quick but stable state. Xilinx hardware/software development kits provide working hardware boards, hardware-aware tools, and pre-verified reference designs. The benefit here is that you can power up hardware, download a working design to a board, and start investigating a "working" core system in a very short period of time, skipping past the delays and complexities of debugging new hardware, new firmware, and new software all at the same time.

A majority of the embedded design cycle, before full system verification, is spent iterating on the core design, incrementally introducing new features, adding individual capabilities, and repeatedly debugging after each step. Because this is excessively tedious and time consuming, this stage should be as easy and streamlined as possible. Version 8.1 has a focus on making common (and repetitive) tasks simple and intuitive, benefiting both new and existing users.

#### All Users Benefit from V8.1

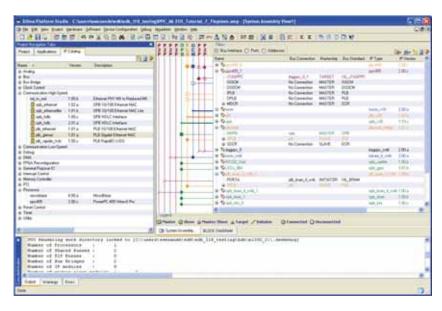

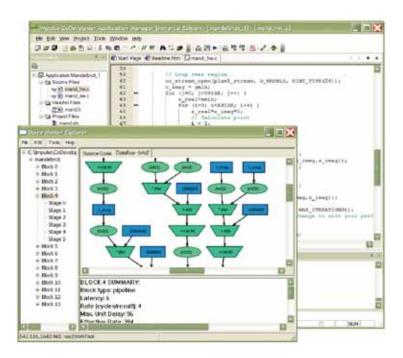

Xilinx has updated the main user interface of Platform Studio to provide an intuitive feel for both hardware and software engineers, making multiple views and customization easy for all. The integrated development environment (IDE) in Figure 1 displays a wide array of information, but also allows you to filter views and customize the toolbars. The left-hand pane provides an industry-standard "tab" method of displaying or hiding information panels on the design "Project," "Applications," or "IP Catalog." Just toggle on the tab of choice to display the contents of that pane.

The "Project" tab contains a variety of helpful information about the design, including specific Xilinx device selection and settings (for example, a specific Virtex<sup>TM</sup>-4 or Virtex-II Pro device with one or two PowerPC<sup>TM</sup> processor cores) and project file locations (hardware and software project descriptions as well as log and report files for steps like synthesis), as well as simulation setup details.

You can view software applications under the "Applications" tab, which provides access to all of the C source and header files that make up the embedded system design. This view also provides views of the compiler options and even the block RAM initialization process.

The "IP Catalog" tab contains in-depth information about the IP cores created, bought, or imported for the design. Xilinx provides several scores of processing IP cores in the Embedded Development Kit software bundle as well as some high-value cores for time-limited evaluations. You can research Xilinx processor IP at www. xilinx.com/ise/embedded/edk\_ip.htm.

The middle panel is the "Connectivity" view, and the adjacent panel to the right of that is the associated "System Assembly" view. The connectivity view gives a clear visual of the design busing structure and also provides a dynamic tool for creating new or editing existing connections. The color-coded view quickly makes it clear even to novice users - the specifics of the bus type and how it might relate to IP. For example, in this view, peripherals connected to the PLB (processor local bus) are presented in orange; OPB (on-chip peripheral bus) connections are green; and point-topoint connections with a processor core, in this case the PowerPC 405, are in purple. The panel "filter" buttons allow you to customize or simplify the connection views so that you can focus on specific bus elements without the distraction of other elements.

Platform Studio reduces the errors that a designer might make by maintaining correct connections by construction – that is,

Figure 1 - New 8.1 Platform Studio GUI

XPS will only display connection options for compatible bus types. This saves debug headaches with tools that allow incompatible connections.

The system assembly view (see Figure 2) more clearly displays an example of dynamic system construction using a "drag-and-drop connectivity instantiation." In the figure, the gray highlighted "opb\_uartlite" IP core is selected on the left panel from the IP Catalog and has been dragged and dropped into the right assembly window, creating a new OPB bus connection option automatically; just mouse-click to connect. The views on the right also provide helpful information such as IP types for perusing and IP version numbers for project version control. Now, at a glance, you can distinguish the system structure without reading reams of documentation.

However, if design documentation is what your project and team require, Platform Studio 8.1 has the powerful capability to generate full design-reference

material, including a full block diagram view of the system elements and their interconnections. This automatic generation of the docs saves valuable time (instead of creating the materials manually) and reduces errors by creating the materials directly from the design. This method keeps the docs and the design accurately in sync as well as displaying a clear high-level view of the entire project.

#### **New Enhancements Help Existing Users**

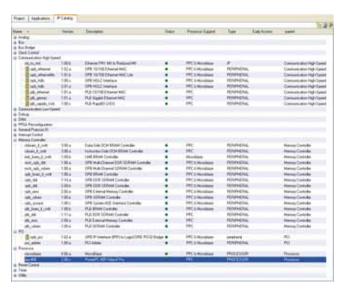

Current Platform Studio users will be pleased to see advances in the support of sophisticated software development, IP support, and the migration or upgrades of older designs. Figure 3 is an example of what the IP Catalog tab might look like for a design, including all IP cores categorically grouped on the left-hand side by logical names. The specific IP cores will display a version number for design control as well

Figure 2 – System assembly view

Figure 3 – XPS IP catalog

as a brief language description if the names are too brief for context. This view allows you to manage your old and current IP as well as future IP upgrades (more powerful versions of cores with more features but often faster and smaller in size).

Additional information is available as well, such as which processor cores the IP supports. Because Xilinx offers flexible support for both high-performance PowerPC hard and flexible MicroBlaze<sup>TM</sup> soft-processor cores, it is useful to know which IP cores are dedicated to one processor, the other, or both. In fact, a right mouse-click on the IP from the catalog yields quick access to the IP change history as well as complete PDF datasheets on the specifics. Software drivers for the peripherals have a similar platform settings view for clarity, including version control and embedded OS support.

When a new version of tools and IP becomes available, the upward design

migration ought to be as painless as possible. Nobody wants to reinvest design, debugging, and test time to move an older design to a newer set of tools or IP. However, there are often great advantages in new IP/tools that make it advantageous to upgrade. Platform Studio 8.1 has a migration capability (Figure 4) that steps you through a wizard to automate and accelerate the process.

XPS 8.1 can browse existing design projects, flag out-of-date projects and IP cores, and then walk you though the process of confirming automated updates to the new IP and project files. The migration wizard updates the project description files and summarizes the migration changes in document form. Minimizing labor-intensive steps means that you can take advantage of new advancements without as much manual re-entering or porting of designs.

Savvy software developers working on more sophisticated code applications will be happy with the enhancements to the

XPS Software Development Kit IDE, based on Eclipse. The XPS-SDK has an enhanced toolbar that more logically groups similar functions and buttons while still allowing user customization.

Figure 4 – XPS design migration

Version 8.1 introduces a more powerful C/C++ editor supporting code folding of functions, methods, classes, structures, and macros, as well as new compiler advancements. This new support provides the ability to specify linker scripts and customized compiler options for PowerPC and MicroBlaze processor cores, plus a C++ class creation wizard. Combine this powerful software environment with the innovative performance profiling views and unique XPS capability of integrated hardware/software debuggers, and 8.1 users will be creating better, more powerful embedded systems in less time than ever before.

#### Conclusion

The award-winning Platform Studio has already streamlined embedded system design. Automated design wizards and preconfigured hardware/software development kits help kick-start designs while reducing errors and tail-chasing.

Now that we have an industry-proven success in ramping-up the "getting started" process, it is time to improve the time-consuming and cyclical nature at the heart of the development process. Create – Debug – Edit – Repeat. Have you ever used a computer-aided tool where most of the steps were intuitive? Where you could guess what a button did before you read the manual or saw a screen in which the contents were all self-evident?

EDK/XPS version 8.1 focuses on ease-ofuse improvements across the board, including enhancements to the main user interface, the software development environment (including editing and compiling), the upgrading of IP, the migrating of old projects, documenting designs, viewing and editing bus-based systems, and much more.

By making common tasks simple and intuitive, we can make designing a little bit easier for experienced embedded engineers as well as those brand-new to designing with processors in programmable FPGA platforms. Use the extra time saved during the development process to innovate your own embedded products.

For more information about EDK version 8.1 and all of our embedded processing solutions, visit www.xilinx.com/edk.

### WHAT'S NEW

To complement our flagship publication *Xcell Journal*, we've recently launched three new technology magazines:

- *Embedded Magazine*, focusing on the use of embedded processors in Xilinx® programmable logic devices.

- *DSP Magazine*, focusing on the high-performance capabilities of our FPGA-based reconfigurable DSPs.

- *I/O Magazine*, focusing on the wide range of serial and parallel connectivity options available in Xilinx devices.

In addition to these new magazines, we've created a family of Solution Guides, designed to provide useful information on a wide range of hot topics such as Broadcast Engineering, Power Management, and Signal Integrity.

Others are planned throughout the year.

See all of the new publications on our website:

www.xilinx.com/xcell

9

March 2006 Embedded magazine

# Change Is Good

Hardware designers and software designers can't often agree, but there is a middle ground that both might enjoy.

by Jim Turley

Editor in Chief, Embedded Systems Design

CMP Media LLC

iim@iimturley.com

If you shout "microprocessor" in a crowded theatre, most people will think "Pentium." Intel's famous little chip has captured the public imagination to the point where many people think 90% of all the chips made come streaming out of Intel's factories.

Nothing could be further from the truth. The fact is, Pentium accounts for less than 2% of all of the microprocessors made and sold throughout the world. The lions' share – that other 98% – are processors embedded into everyday appliances, automobiles, cell phones, washers, dryers, DVD players, video games, and a million other "invisible computers" all around us. PCs are a statistically insignificant part of the larger world – and Pentium sales are a rounding error.

Take heart, embedded developers, for though you may toil in obscurity, your deeds are great, your creations mighty, and your number legion. With few exceptions, most engineers are embedded systems developers. We're the rule, not the exception.

#### **Processors As Simulators**

What is exceptional is the number of different ways we approach a problem. All PCs look pretty much the same, but there's no such thing as a typical embedded system. They're all different. We don't standardize on one operating system, one processor (or even processor family), or one power supply, package, or peripheral mix. Among 32-bit processors alone there are more than 100 different chips available from more than a dozen different suppliers, each one with happy customers designing systems around them. Hardly a homogenous group, are we?

There's even a school of thought that

microprocessors themselves are a mistake - a technical dead-end. The theory goes that microprocessors merely simulate physical functions (addition, subtraction, FFT analysis), rather than performing the function directly. Decoding and executing instructions, handling interrupts, and calculating branches is all just overhead. A close look at any modern processor chip would seem to bear this theory out: only about 15% of the chip's transistors do any actual work. The rest are dedicated to cracking opcodes, handling flag bits, routing buses, managing caches, and other effluvia necessary to make the hardware do what the software tells it to do.

The only reason processors were ever invented in the first place (so the thinking goes) is because they were more malleable

than "real" hardware. You could change your code over time – but you couldn't change your hardware.

But that isn't true any more.

Following this line of reasoning, the right approach is to do away with processors and software altogether and implement your functions directly in hardware. Forget that 85% of processor overhead logic and get right down to the nuts and bolts. Make every one of those little transistors work for a living. And hey, if you change your mind, you can change your hardware – if it's programmable.

#### The Malleable Engineer

So now we're faced with the proverbial (and overused) paradigm shift. We can toss out everything we know about programming, operating systems, software, real-time code, compilers, boot loaders, and bit-twiddling and go straight to hard-wired hardware implementations.

Or not.

Maybe we like programming. There's something about software design that appeals to the inner artist in us. It's a whole different way of thinking compared to hardware design, at least for a lot of engineers. Software is like poetry; hardware is

like architecture. There's plenty of bad poetry because anyone can do it, but you don't see people tossing up buildings just to see if they stand. Programming requires much less discipline and training than hardware engineering. That's why there are so many programmers in the world.

This is a good thing. Really. The easier it is to enter the engineering profession, the more (and better) engineers we're likely to have. And since hardware- and software-design mindsets are different, we get to draw from a bigger cross section of the populace. Variety is good.

More to the point, it's no longer an either/or decision. The two disciplines are not mutually exclusive; engineering is not a zero-sum game. We don't have to come down firmly on the side of hardware or software; we can straddle the middle ground as it suits us. When your hardware is programmable, you can choose to "program" it or "design" it using traditional circuitry methods. Take your pick. Let whimsy or convention be your guide.

Engineers, like most craftsmen, place great stock in their tools. A recent survey revealed that most developers choose their tools (compiler, logic analyzer, IDE) first and the "platform" they work on second. For example, they let their choice of compiler determine their choice of processor, not vice versa. The hardware – a microprocessor, generally – is treated as a canvas or work piece on which they ply their trade. This comes as a bit of a blow to some of the more traditional microprocessor makers, who'd always assumed that the world revolved around their instruction set.

The takeaway from this part of the survey was that keeping developers in their comfort zone is paramount. Engineers don't like to modify their skills or habits to accommodate someone else's hardware. Instead, the hardware should adapt to them. In the best case, the hardware should even adapt to a code jockey one day and a circuit snob the next. Different tools for different approaches, but with one goal in mind: to create a great design within time and budget (and power, and heat, and pinout, and cost, and performance) constraints.

There hasn't been anything to accommodate this flexibility until pretty recently. Hardware was hardware; code was code. But with "soft processors" in FPGAs living alongside seas of gates and coprocessors, we've got the ultimate canvas for creative developers. Whether it's VHDL or C++, these new chips can be customized in whatever way suits you. They're as flexible as any software program, and as fast and efficient as "real" hardware implementations. We may finally have achieved the best of both worlds.

11

# Implementing Floating-Point DSP

Using PicoBlaze processors for high-performance, power-efficient, floating-point DSP.

by Jiři Kadlec DSP Researcher UTIA Prague, Czech Republic kadlec@utia.cas.cz

Stephen P.G. Chappell

Director, Applications Engineering

Celoxica Ltd., Abington, UK

steve.chappell@celoxica.com

For developers using FPGAs for the implementation of floating-point DSP functions, one key challenge is how to decompose the computation algorithm into sequences of parallel hardware processes while efficiently managing data flow through the parallel pipelines of these processes.

In this article, we'll discuss our experiences exploring architectures with Xilinx® PicoBlaze<sup>TM</sup> controllers, and present a design strategy employing the ESL techniques of model-based and C-based design to demonstrate how you can rapidly integrate highly parameterizable DSP hardware primitives into power-efficient

high-performance implementations in Spartan  $^{\text{TM}}$  devices.

#### **Hardware Acceleration and Reuse**

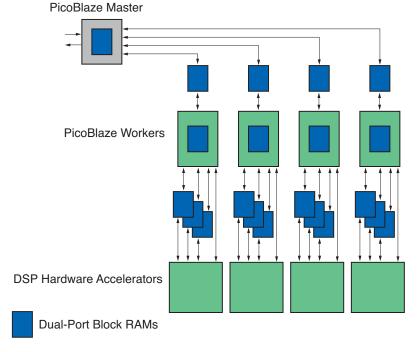

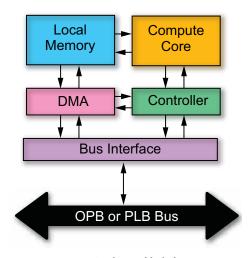

High-performance implementations of floating-point DSP algorithms in FPGAs require single-cycle parallel memory accesses and effective use of pipelined arithmetic operators. Many common DSP vector and matrix operations can be split into batch calculations fulfilling these requirements. Our architectures comprise Xilinx PicoBlaze worker processors, each with a dedicated DSP hardware accelerator (Figure 1). Each worker can do preparatory tasks for the next batch in parallel with its hardware accelerator. Once the DSP hardware accelerator finishes the computation, it issues an interrupt to the worker. The worker's job is to combine the accelerated parts of the computation into a complete DSP algorithm.

It is ideal if you limit implementations to the batch operations of each worker starting in a block RAM, performing a relatively simple sequence of pipelined operations at the maximum clock speed and returning the result(s) back to another block RAM. You can effectively map these primitives to hardware, including the complete autonomous data-flow control in hardware. You can also code the related dedicated generators of address counters and control signals in Handel-C, using several synchronized do-while loops. Simulink is effective for fast derivation of bit-exact models of the batch calculations in DSP hardware accelerators.

#### Floating-Point Processor on a Single FPGA

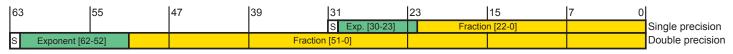

Let's consider an architecture for the evaluation of a  $1024 \times 1024$  vector product in 18m12 floating point. (In the format AmB, A is for the word length and B is for the number of bits in the mantissa, including the leading hidden bit representing 1.0.)

We implemented this architecture using five PicoBlaze processors on a single FPGA: one master and four simplified workers (Figure 1). The master is connected to the workers by I/O-mapped dualported block RAMs organized in 2,048 8bit words. The master maintains the real-time base with 1 µs resolution and provides RS232 user-interface functions. Each worker serves as a controller to a dedicated floating-point DSP hardware accelerator connected through three dual-ported block RAMs organized in 1,024 18-bit words. Two block RAMs hold source vectors and one holds results data. In this case, the workers perform one quarter of the computation each, namely a 256 x 256 vector product. The DSP hardware accelerators are implemented in hardware, from block RAM data source to block RAM data sink,

Figure 1 – PicoBlaze-based architecture for floating-point DSP. The DSP hardware accelerators are modeled and implemented using Celoxica DK.

| Part:<br>xc2v1000-4<br>xc3s1500L-4 |     | 18m12:<br>125 MHz<br>84 MHz |        |      | 32m24:<br>110 MHz<br>84 MHz |        |      | 64m53:<br>100 MHz<br>72 MHz |        |

|------------------------------------|-----|-----------------------------|--------|------|-----------------------------|--------|------|-----------------------------|--------|

| Pipelined:                         | FF  | LUT                         | Pipe   | FF   | LUT                         | Pipe   | FF   | LUT                         | Pipe   |

| ADD                                | 834 | 793                         | 5      | 1158 | 1290                        | 5      | 1686 | 2007                        | 5      |

| MULT                               | 639 | 488                         | 3      | 967  | 626                         | 4      | 2029 | 1256                        | 5      |

| F2FIXPT                            | 581 | 637                         | 4      | 649  | 744                         | 4      | 808  | 1053                        | 4      |

| FIXPT2F                            | 695 | 709                         | 6      | 792  | 787                         | 6      | 1008 | 946                         | 6      |

| Sequential:                        |     |                             | Cycles |      |                             | Cycles |      |                             | Cycles |

| DIV                                | 739 | 605                         | 17     | 987  | 772                         | 29     | 2119 | 1143                        | 58     |

| SQRT                               | 766 | 604                         | 16     | 1053 | 802                         | 28     | 1729 | 1303                        | 57     |

Table 1 – Used flip-flops, LUTs, pipeline/latency, and maximum clock for Celoxica floating-point modules in system implementations in the Celoxica RC200E (Virtex-II FPGA) and RC10 (Spartan-3L FPGA) boards. Modules are pipelined, with the exception of DIV and SQRT.

using one 18m12 multiplier (FP MUL) and one 18m12 adder (FP ADD).

#### Scalable, Short-Latency Floating-Point Modules

We used a newly released version of a scalable, short-latency pipelined floating-point library from Celoxica to build our DSP hardware accelerators. Table 1 considers some of the parameterizations of this FPGA vendorindependent library to the formats 18m12, 32m24, and 64m53. The library includes IEEE754 rounding, including the round to even. It provides bit-exact results to the Xilinx LogiCORETM floating-point operators (v2.0), with latency set to approximately one half. The resulting maximum system clock is compatible with PicoBlaze and MicroBlaze<sup>TM</sup> embedded processors.

#### Simulink and the DK Design Suite

Our design flow is based on the bit-exact modeling of Handel-C floating-point units in a Simulink framework, where the Handel-C is developed in the DK Design Suite combined simulation and synthesis environment. This enabled us to decompose a floating-point algorithm into a sequence of simple operations with rapid development and testing of different combinations.

#### Step 1: Model in Simulink

First, we built a model of the DSP hardware accelerator in Simulink (Figure 2). The data sources and sinks in this model will be the block RAMs shared with the PicoBlaze worker in the final implementation.

Because the FPGA floating-point operations are written in cycle-accurate and bit-exact Handel-C, we benefited from a single source for both implementation and simulation. For modeling, we exported the Handel-C functions to S-functions using Celoxica's DK Design Suite. We then incorporated these into a bit-exact Simulink model. In this fast functional simulation, we use delay blocks in Simulink to model pipeline stages (see the 5-stage pipeline of the FP ADD operator and related registers in Figure 2). We used separate Simulink subsystems to model the bit-exact operation of the final "pipeline flushing," or "wind-up opera-

13

tion." In this case, six partial sums have to be added by a single reused FP ADD module (Figure 3). The corresponding hardware computes the final sum of the partial sums by reconnecting the pipelined floating-point adder to different contexts for several final clock cycles.

#### Step 2: Cycle-Accurate Verification

Our next stage was to create test vectors using Simulink and feed these into a bit-exact and cycle-accurate simulation of the DSP hardware accelerator in the DK Design Suite's debugger. Once we confirmed identical results for both the DK and Simulink models, we compiled the Handel-C code to an EDIF netlist.

#### Step 3: Hardware Test

We took advantage of a layered design approach by using a single communication API for data I/O functions that applies to both simulation and implementation. This allowed us to veri-

fy the DSP hardware accelerator design on real FPGA hardware by "linking" with an appropriate board support library for implementation. We can optionally insert this hardware test back into the Simulink model for hardware-in-the-loop simulations. The test on FPGA hardware provides reliable area and clock figures.

#### Step 4: Create Reusable Module and Connect to Worker

Finally, we treated the verified block RAM-to-block RAM DSP hardware accelerator as a new module and integrated it into our main design by compiling the Handel-C to EDIF or RTL using the DK Design Suite. This reusable module is connected to the PicoBlaze network by wiring the ports of the block RAMs and the

Figure 2 – Simulink test bench for floating-point 18m12 vector product based on Handel-C bit-exact models

Figure 3 – Simulink subsystem based on Handel-C bit-exact models, including delay model of calculation wind-up at the end of the vector product batch

| Part:       | MHz | MFLOPs | mW   |

|-------------|-----|--------|------|

| xc2v1000-4  | 100 | 700    | 1360 |

| xc3s1500L-4 | 84  | 588    | 263  |

Table 2 – Results for 1024 x 1024 vector product in 18m12 floating point on the Celoxica RC200E (Virtex-II FPGA) and RC10 (Spartan-3L FPGA) boards

appropriate enable and controller interrupt signals. At this stage we tested the function of the DSP hardware accelerator under worker control using memory dump user support from the master.

#### Step 5: Develop Complete DSP Design

We next assembled the complete design of workers and master, moving to assembly pro-

gramming of individual PicoBlaze workers and their interactions.

#### **Performance Results**

Test results using the Celoxica RC200E (Virtex<sup>TM</sup>-II FPGA) and RC10 (Spartan<sup>TM</sup>-3L FPGA) boards are shown in Table 2. It is interesting to compare the power consumption of the PicoBlaze network architecture on Virtex-II devices (RC200E) with the identical design on the low-power 90 nm Spartan-3L device (RC10). The latter part gives a highly favorable floating-point performance-to-power ratio.

#### Conclusion

With minimal overhead, PicoBlaze workers add flexibility to floating-point DSP hardware accelerators by their ability to call and reuse software functions (even if in assembly language only). Our proposed architecture enables more flexible and generic floating-point algorithms without the additional increase of hardware complexity associated with hardware-only implementations due to irregularities and complex multiplexing of pipelined structures. PicoBlaze cores are compact, simple, and

therefore manageable, without designers needing to combine too many new skills.

The use of floating-point designs developed using the DK Design Suite in combination with a Simulink framework provides an effective design path that is relatively easy to debug and scalable to more complex designs.

Spartan-3L technology considerably reduces power consumption compared to Virtex-II devices. Considering the benefits in terms of performance/power/price, Spartan-3L FPGA implementations of floating-point DSP pipelines using networks of PicoBlaze processors are an interesting option.

You can find complete information on the design and technology discussed in this article at www.celoxica.com/xilinx.

# ESL Tools for FPGAs

Empowering software developers to design with programmable hardware.

by Milan Saini

Technical Marketing Manager

Xilinx, Inc.

milan.saini@xilinx.com

A fundamental change is taking place in the world of logic design. A new generation of design tools is empowering software developers to take their algorithmic expressions straight into hardware without having to learn traditional hardware design techniques.

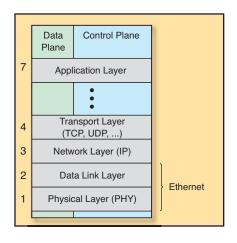

These tools and associated design methodologies are classified collectively as electronic system level (ESL) design, broadly referring to system design and verification methodologies that begin at a higher level of abstraction than the current mainstream register transfer level (RTL). ESL design languages are closer in syntax and semantics to the popular ANSI C than to hardware languages like Verilog and VHDL.

#### **How is ESL Relevant to FPGAs?**

ESL tools have been around for a while, and many perceive that these tools are predominantly focused on ASIC design flows. The reality, however, is that an increasing number of ESL tool providers are focusing on programmable logic; currently, several tools in the market support a system design flow specifically optimized for Xilinx® FPGAs. ESL flows are a natural evolution for FPGA design tools, allowing the flexibility of programmable hardware to be more easily accessed by a wider and more software-centric user base.

Consider a couple of scenarios in which ESL and FPGAs make a great combination:

- 1. Together, ESL tools and programmable hardware enable a desktop-based hardware development environment that fits into a software developer's workflow model. Tools can provide optimized support for specific FPGAbased reference boards, which software developers can use to start a project evaluation or a prototype. The availability of these boards and the corresponding reference applications written in higher level languages makes creating customized, hardwareaccelerated systems much faster and easier. In fact, software programmers are now able to use FPGA-based reference boards and tools in much the same way as microprocessor reference boards and tools.

- 2. With high-performance embedded processors now very common in FPGAs, software and hardware design components can fit into a single device. Starting from a software description of a system, you can implement individual design blocks in hardware or software depending on the applications' performance requirements. ESL tools add value by enabling intelligent partitioning and automated export of software functions into equivalent hardware functions.

ESL promotes the concept of "explorative design and optimization." Using ESL methodologies in combination with programmable hardware, it becomes possible to try a much larger number of possible application implementations, as well as rapidly experiment with dramatically different software/hardware partitioning strategies. This ability to experiment – to try new approaches and quickly analyze performance and size trade-offs – makes it possible for ESL/FPGA users to achieve higher overall performance in less time than it would take using traditional RTL methods.

Additionally, by working at a more abstract level, you can express your intent using fewer keystrokes and writing fewer lines of code. This typically means a much faster time to design completion, and less chance of making errors that require tedious, low-level debugging.

#### **ESL's Target Audience**

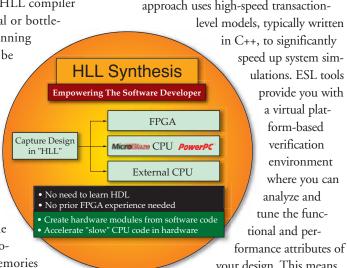

The main benefits of ESL flows for prospective FPGA users are their productivity and ease-of-use. By abstracting the implementation details involved in generating a hardware circuit, the tools are marketing their appeal to a software-centric user base (Figure 1). Working at a higher level of abstraction allows designers with skills in traditional software programming languages like C to more quickly explore their ideas in hardware. In most instances, you can implement an entire design in hardware without the assistance of an

15

March 2006 Embedded magazine

experienced hardware designer. Softwarecentric application and algorithm developers who have successfully applied the benefits of this methodology to FPGAs include systems engineers, scientists, mathematicians, and embedded and firmware developers.

The profile of applications suitable for ESL methodologies includes computationally intensive algorithms with extensive innerloop constructs. These applications can realize tremendous acceleration through the concurrent parallel execution possible in hardware. ESL tools have helped with successful project deployments in application domains such as audio/video/image processing, encryption, signal and packet processing, gene sequencing, bioinformatics, geophysics, and astrophysics.

#### **ESL Design Flows**

ESL tools that are relevant to FPGAs cover two main design flows:

1. High-level language (HLL) synthesis. HLL synthesis covers algorithmic or behavioral synthesis, which can produce hardware circuits from C or Clike software languages. Various partner solutions take different paths to converting a high-level design description into an FPGA implementation. How this is done goes to the root of the differences between the various ESL offerings.

You can use HLL synthesis for a variety of use cases, including:

• Module generation. In this mode of use, the HLL compiler can convert a functional block expressed in C (for example, as a C subroutine) into a corresponding hardware block. The generated hardware block is then assimilated in the overall hardware/software design. In this way, the HLL compiler generates a submodule of the overall design.

Module generation allows software engineers to participate in the overall system design by quickly generating, then integrating, algorithmic hardware components. Hardware engineers seek-

16

ing a fast way to prototype new, computation-oriented hardware blocks can also use module generation.

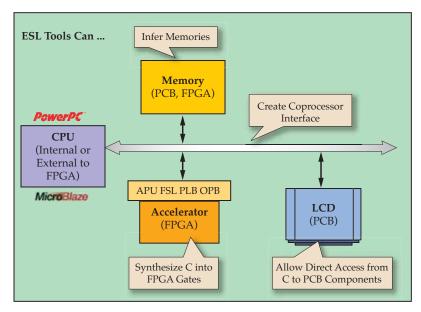

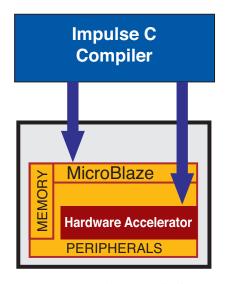

· Processor acceleration. In this mode of use, the HLL compiler allows time-critical or bottleneck functions running on a processor to be accelerated by enabling the creation of a custom accelerator block in the in "HLL" programmable fabric of the FPGA. In addition to creating the accelerator, the tools can also automatically infer memories and generate the required hardware-software interface circuitry, as well as the software device drivers that enable communication between the processor and the hardware accelerator block (Figure 2). When compared to code running on a CPU, FPGAaccelerated code can run orders of magnitude faster while consuming

significantly less power.

2. System modeling. System simulations using traditional RTL models can be very slow for large designs, or when processors are part of the complete design. A popular emerging ESL approach uses high-speed transaction-

> in C++, to significantly speed up system simulations. ESL tools provide you with a virtual platform-based verification environment where you can analyze and tune the functional and per-

your design. This means much earlier access to a virtual representation of the system, enabling greater design exploration and what-if analysis. You can

evaluate and refine performance issues such as latency, throughput, and bandwidth, as well as alternative software/hardware partitioning strategies. Once the design meets its performance objectives, it can be committed to implementation in silicon.

Figure 1 – Most of the ESL tools for FPGAs are targeted at a softwarecentric user base.

Figure 2 – ESL tools abstract the details associated with accelerating processor applications in the FPGA.

## ...today's ESL technologies are ready to deliver substantial practical value to a potentially large target audience.

#### The Challenges Faced by ESL Tool Providers

In relative terms, ESL tools for FPGAs are new to the market; customer adoption remains a key challenge. One of the biggest challenges faced by ESL tool providers is overcoming a general lack of awareness as to what is possible with ESL and FPGAs, what solutions and capabilities already exist, and the practical uses and benefits of the technology. Other challenges include user apprehension and concerns over the quality of results and learning curve associated with ESL adoption.

Although paradigm shifts such as those introduced by ESL will take time to become fully accepted within the existing FPGA user community, there is a need to tackle some of the key issues that currently prohibit adoption. This is particularly important because today's ESL technologies are ready to deliver substantial practical value to a potentially large target audience.

#### Xilinx ESL Initiative

Xilinx believes that ESL tools have the promise and potential to radically change the way hardware and software designers create, optimize, and verify complex electronic systems. To bring the full range of benefits of this emerging technology to its customers and to establish a common platform for ESL technologies that target FPGAs in particular, Xilinx has proactively formed a collaborative joint ESL Initiative with its ecosystem partners (Table 1).

The overall theme of the initiative is to accelerate the pace of ESL innovation for FPGAs and to bring the technology closer to the needs of the software-centric user base. As part of the initiative, there are two main areas of emphasis:

Engineering collaboration. Xilinx will work closely with its partners to continue to further increase the value of ESL product offerings. This will

- include working to improve the compiler quality of results and enhance tool interoperability and overall ease-of-use.

- 2. ESL awareness and evangelization. Xilinx will evangelize the value and benefits of ESL flows for FPGAs to current and prospective new customers. The program will seek to inform and educate users on the types of ESL solutions that currently exist and how the various offerings can provide better approaches to solving existing problems. The aim is to empower users to make informed decisions on the suitability and fit of various partner ESL offerings to meet their specific application needs. Greater awareness will lead to increased customer adoption, which in turn will contribute to a sustainable partner ESL for FPGAs ecosystem.

#### **Getting Started With ESL**

As a first step to building greater awareness on the various ESL for FPGA efforts, Xilinx has put together a comprehensive ESL website. The content covers the specific and unique aspects of each of the currently available partner ESL solutions and is designed to help you decide which, if any, of the available solutions are a good fit for your applications. To get started with your ESL orientation, visit www.xilinx.com/esl.

Additionally, Xilinx has also started a new ESL for FPGAs discussion forum at <a href="http://toolbox.xilinx.com/cgi-bin/forum">http://toolbox.xilinx.com/cgi-bin/forum</a>. Here, you can participate in a variety of discussions on topics related to ESL design for FPGAs.

#### **Conclusion**

ESL tools for FPGAs give you the power to explore your ideas with programmable hardware without needing to learn low-level details associated with hardware design. Today, you have the opportunity to select from a wide spectrum of innovative and productivity-enhancing solutions that have been specifically optimized for Xilinx FPGAs. With the formal launching of the ESL Initiative, Xilinx is thoroughly committed to working with its third-party ecosystem in bringing the best-in-class ESL tools to its current and potential future customers. Stay tuned for continuing updates and new developments.

17

| Partner        | FPGA Synthesis | Xilinx CPU Support | FPGA Computing Solution              |

|----------------|----------------|--------------------|--------------------------------------|

| Celoxica       | •              | •                  | Handel-C, SystemC to gates           |

| Impulse        | •              | •                  | Impulse C to gates                   |

| Poseidon       | •              | •                  | HW/SW partitioning, acceleration     |

| Critical Blue  | •              |                    | Co-processor synthesis               |

| Теја           |                | •                  | C to multi-core processing           |

| Mitrion        | •              |                    | Adaptable parallel processor in FPGA |

| System Crafter | •              |                    | SystemC to gates                     |

| Bluespec       | •              |                    | SystemVerilog-based synthesis to RTL |

| Nallatech      | •              | •                  | High-performance computing           |

Table 1 – Xilinx ESL partners take different approaches from high-level languages to FPGA implementation.

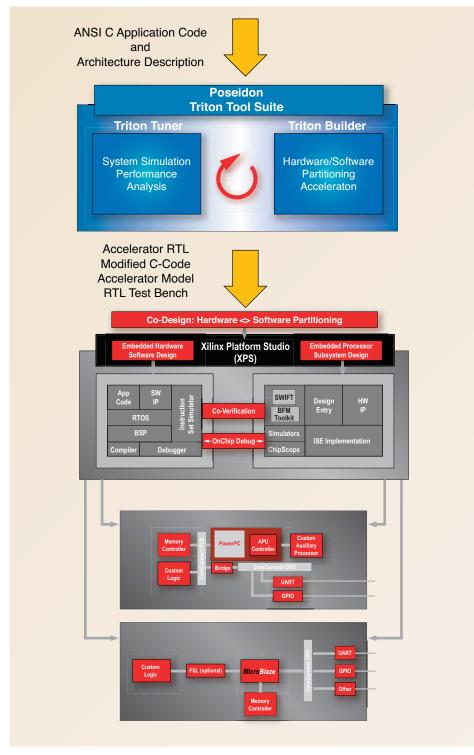

# Algorithmic Acceleration Through Automated Generation of FPGA Coprocessors

C-to-FPGA design methods allow rapid creation of hardware-accelerated embedded systems.

by Glenn Steiner

Sr. Engineering Manager, Advanced Products Division Xilinx, Inc.

alenn.steiner@xilinx.com

#### Kunal Shenov

Design Engineer, Advanced Products Division Xilinx, Inc. kunal.shenoy@xilinx.com

#### Dan Isaacs

Director of Embedded Processing, Advanced Products Division Xilinx, Inc. dan.isaacs@xilinx.com

#### David Pellerin

Chief Technology Officer Impulse Accelerated Technologies david.pellerin@impulsec.com

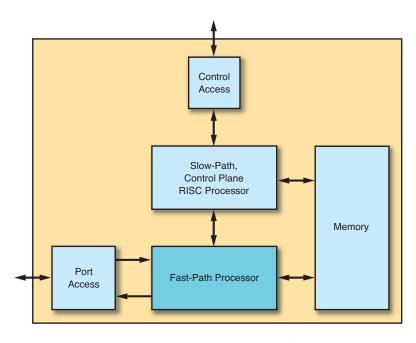

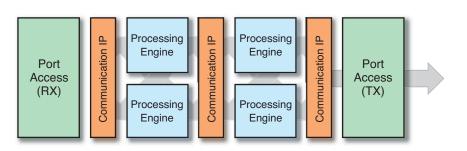

Today's designers are constrained by space, power, and cost, and they simply cannot afford to implement embedded designs with gigahertz-class computers. Fortunately, in embedded systems, the greatest computational requirements are frequently determined by a relatively small number of algorithms. These algorithms, identified through profiling techniques, can be rapidly

converted into hardware coprocessors using design automation tools. The coprocessors can then be efficiently interfaced to the offloaded processor, yielding "gigahertz-class" performance.

In this article, we'll explore code acceleration and techniques for code conversion to hardware coprocessors. We will also demonstrate the process for making trade-off decisions with benchmark data through an actual image-rendering case study involving an auxiliary processor unit (APU)-based technique. The design uses an immersed PowerPC<sup>TM</sup> implemented in a platform FPGA.

#### The Value of a Coprocessor

A coprocessor is a processing element that is used alongside a primary processing unit to offload computations normally performed by the primary processing unit. Typically, the coprocessor function implemented in hardware replaces several software instructions. Code acceleration is thus achieved by both reducing multiple code instructions to a single instruction as well as the direct implementation of the instruction in hardware.

The most frequently used coprocessor is the floating-point unit (FPU), the only common coprocessor that is tightly coupled to the CPU. There are no general-purpose libraries of coprocessors. Even if there were, it is still difficult to readily couple a coprocessor to a CPU, such as a Pentium 4.

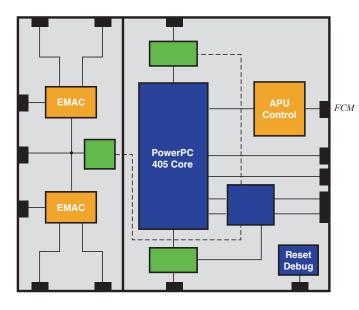

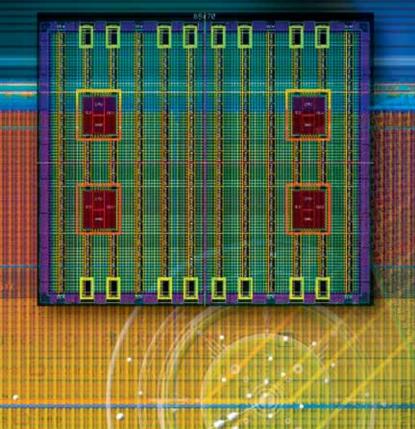

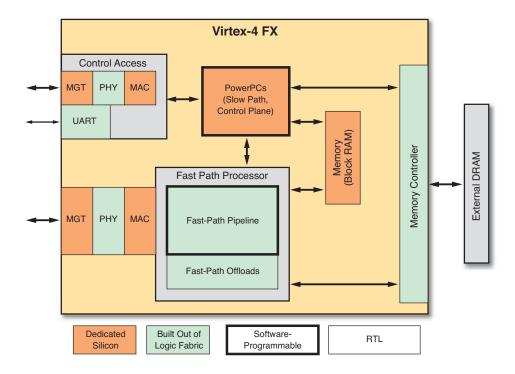

As shown in Figure 1, the Xilinx® Virtex<sup>TM</sup>-4 FX FPGA has one or two PowerPCs, each with an APU interface. By embedding a processor within an FPGA, you now have the opportunity to implement complete processing systems of your own design within a single chip.

The integrated PowerPC with APU interface enables a tightly coupled coprocessor that can be implemented within the FPGA. Frequency requirements and pin number limits make an external coprocessor less capable. Thus, you can now create application-specific coprocessors attached directly to the PowerPC, providing significant software acceleration. Because FPGAs are reprogrammable, you can rapidly develop and test CPU-attached coprocessor solutions.

#### **Coprocessor Connection Models**

Coprocessors are available in three basic forms: CPU bus connected, I/O connected, and instruction-pipeline connected. Mixed variants also exist.

#### **CPU Bus Connection**

Processor bus-connected accelerators require the CPU to move data and send commands through a bus. Typically, a single data transaction can require many

processor cycles. Data transactions can be hindered by bus arbitration and the necessity for the bus to be clocked at a fraction of the processor clock speed. A busconnected accelerator can include a direct memory access (DMA) engine. At the cost of additional logic, the DMA engine allows a coprocessor to operate on blocks of data located on bus-connected memory, independent of the CPU.

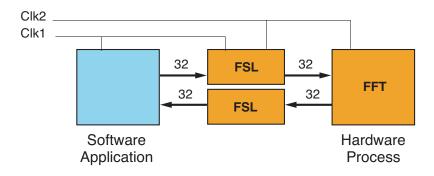

#### I/O Connection

I/O-connected accelerators are attached directly to a dedicated I/O port. Data and control are typically provided through GET or PUT functions.

Lacking arbitration, reduced control complexity, and fewer attached devices, these interfaces are typically clocked faster than a processor bus. A good example of such an interface is the Xilinx Fast Simplex Link (FSL). The FSL is a simple FIFO interface that can be attached to either the Xilinx MicroBlaze<sup>TM</sup> soft-core processor or a Virtex-4 FX PowerPC. Data movement through the FSL has lower latency and a higher data rate than data movement through a processor bus interface.

#### **Instruction Pipeline Connection**

Instruction-pipeline connected accelerators attach directly to the computing core of a CPU. Being coupled to the instruction pipeline, instructions not recognized by the CPU can be executed by the coprocessor. Operands, results, and status are passed

directly to and from the data execution pipeline. A single operation can result in two operands being processed, with both a result and status being returned.

As a directly connected interface, the instruction-pipeline connected accelerators can be clocked faster than a processor bus. The Xilinx implementation for this type of coprocessor connection model through the APU interface demonstrates a 10x clock cycle reduction in the control and movement

Figure 1 – Virtex-4 FX processor with APU interface and EMAC blocks

of data for a typical double-operand instruction. The APU controller is also connected to the data-cache controller and can perform data load/store operations through it. Thus, the APU interface is capable of moving hundreds of millions of bytes per second, approaching DMA speeds.

Either I/O-connected accelerators or instruction-pipeline-connected accelerators can be combined with bus-connected accelerators. At the cost of additional logic, you can create an accelerator that receives commands and returns status through a fast, low-latency interface while operating on blocks of data located in bus-connected memory.

The C-to-HDL tool set described in this article is capable of implementing bus-connected and I/O-connected accelerators. It is also capable of implementing an accelerator connected to the APU interface of the

PowerPC. Although the APU connection is instruction-pipeline-based, the C-to-HDL tool set implements an I/O pipeline interface with a resulting behavior more typical of an I/O-connected accelerator.

#### FPGA/PowerPC/APU Interface

FPGAs allow hardware designers to implement a complete computing system with processor, decode logic, peripherals, and coprocessors all on one chip. An FPGA can

contain a few thousand to hundreds of thousands of logic cells. A processor can be implemented from the logic cells, as in the Xilinx PicoBlaze<sup>TM</sup> or MicroBlaze processors, or it can be one or more hard logic elements, as in the Virtex-4 FX PowerPC. The high number of logic cells enables you to implement dataprocessing elements that work with the processor system and are controlled or monitored by the processor.

FPGAs, being reprogrammable elements, allow you to program parts and test them at any stage during the design process. If you find a design flaw, you can immediately reprogram a part. FPGAs also allow you to implement hardware computing

functions that were previously cost-prohibitive. The tight coupling of a CPU pipeline to FPGA logic, as in the Virtex-4 FX PowerPC, enables you to create high-performance software accelerators.

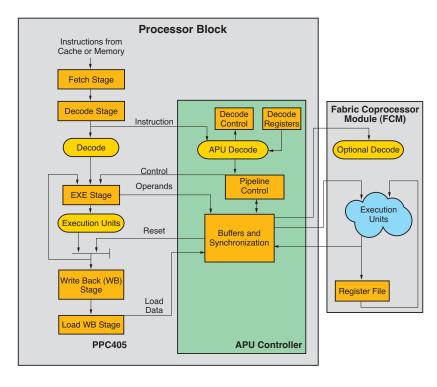

Figure 2 is a block diagram showing the PowerPC, integrated APU controller, and an attached coprocessor. Instructions from cache or memory are simultaneously presented to the CPU decoder and the APU controller. If the CPU recognizes the instruction, it is executed. If not, the APU controller or the user-created coprocessor has the opportunity to acknowledge the instruction and execute it. Optionally, one or two operands can be passed to the coprocessor and a result or status can be returned. The APU interface also supports the ability to transfer a data element with a single instruction. The data element ranges

19

March 2006 Embedded magazine

Figure 2 - PowerPC, integrated APU controller, and coprocessor

in size from one byte to four 32-bit words.

One or more coprocessors can be attached to the APU interface through a fabric coprocessor bus (FCB). Coprocessors attached to the bus range from off-the-shelf cores, such as an FPU, to user-created coprocessors. A coprocessor can connect to the FCB for control and status operations and to a processor

| Implementation                            | Performance |

|-------------------------------------------|-------------|

| Software Implementation                   | 2 MFLOPS    |

| FPU Connected to Processor Bus            | 16 MFLOPS   |

| FPU Connected to APU<br>Interface via FCB | 60 MFLOPS   |

Table 1 – Non-accelerated vs. accelerated floating-point performance

bus, enabling direct access to memory data blocks and DMA data passing. A simplified connection scheme, such as the FSL, can also be used between the FCB and coprocessor, enabling FIFO data and control communication at the cost of some performance.

To demonstrate the performance advantage of an instruction-pipeline-con-

20

nected accelerator, we first implemented a design with a processor bus-connected FPU and then with an APU/FCB-connected FPU. Table 1 summarizes the performance for a finite impulse response (FIR) filter for each case.

As noted in the table, an FPU connected to an instruction pipeline accelerates software floating-point operations by 30x, and the APU interface provides a nearly 4x improvement over a bus-connected FPU.

#### Converting C Code to HDL

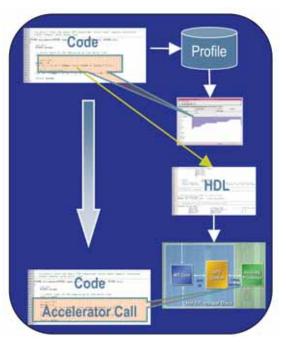

Converting C code to an HDL accelerator with a C-to-HDL tool is an efficient method for creating hardware coprocessors. Figure 3 and the steps below summarize the C-to-HDL conversion process:

1. Implement the application or algorithm using standard C tools. Develop a software test bench for baseline performance and correctness (host or desktop simulations). Use a profiler (such as gprof) to begin identifying critical functions.

- Determine if floating-to-fixed point conversion is appropriate. Use libraries or macros to aid in this conversion. Use a baseline test bench to analyze performance and accuracy. Use the profiler to reevaluate critical functions.

- Using a C-to-HDL tool, such as Impulse C, iterate on each of the critical functions to:

- Partition the algorithm into parallel processes

- Create hardware/software process interfaces (streams, shared memories, signals)

- Automatically optimize and parallelize the critical code sections (such as inner code loops)

- Test and verify the resulting parallel algorithm using desktop simulation, cycle-accurate C simulation, and actual in-system testing.

- 4. Using the C-to-HDL tool, convert the critical code segment to an HDL coprocessor.

- 5. Attach the coprocessor to the APU interface for final testing.

Figure 3 – C-to-HDL design flow

### Impulse C is designed for dataflow-oriented applications, but it is also flexible enough to support alternate programming models...

#### Impulse: C-to-HDL Tool

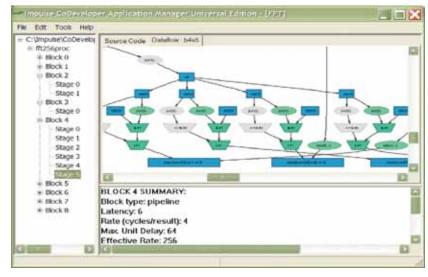

Impulse C, shown in Figure 4, enables embedded system designers to create highly parallel, FPGA-accelerated applications by using C-compatible library functions in combination with the Impulse

some applications, it makes more sense to move data between the embedded processor and the FPGA through block memory reads and writes; in other cases, a streaming communication channel might provide higher performance. The ability to

Figure 4 – Impulse C

CoDeveloper C-to-hardware compiler. Impulse C simplifies the design of mixed hardware/software applications through the use of well-defined data communication, message passing, and synchronization mechanisms. Impulse C provides automated optimization of C code (such as loop pipelining, unrolling, and operator scheduling) and interactive tools, allowing you to analyze cycle-by-cycle hardware behavior.

Impulse C is designed for dataflow-oriented applications, but it is also flexible enough to support alternate programming models, including the use of shared memory. This is important because different FPGA-based applications have different performance and data requirements. In

quickly model, compile, and evaluate alternate algorithm approaches is an important part of achieving the best possible results for a given application.

To this end, the Impulse C library comprises minimal extensions to the C language in the form of new data types and predefined function calls. Using Impulse C function calls, you can define multiple, parallel program segments (called processes) and describe their interconnections using streams, signals, and other mechanisms. The Impulse C compiler translates and optimizes these C-language processes into either:

• Lower-level HDL that can be synthesized to FPGAs, or

Standard C (with associated library calls) that can be compiled onto supported microprocessors through the use of widely available C cross-compilers

The complete CoDeveloper development environment includes desktop simulation libraries compatible with standard C compilers and debuggers, including Microsoft Visual Studio and GCC/GDB. Using these libraries, Impulse C programmers are able to compile and execute their applications for algorithm verification and debugging purposes. C programmers are also able to examine parallel processes, analyze data movement, and resolve process-to-process communication problems using the CoDeveloper Application Monitor.

The output of an Impulse C application, when compiled, is a set of hardware and software source files that are ready for importing into FPGA synthesis tools. These files include:

- Automatically generated HDL files representing the compiled hardware process.

- Automatically generated HDL files representing the stream, signal, and memory components needed to connect hardware processes to a system bus.

- Automatically generated software components (including a run-time library) establishing the software side of any hardware/software stream connections.

- Additional files, including script files, for importing the generated application into the target FPGA place and route environment.

The result of this compilation process is a complete application, including the required hardware/software interfaces, ready for implementation on an FPGA-based programmable platform.

21

March 2006 Embedded magazine

#### **Design Example**

The Mandelbrot image shown in Figure 5, a classic example of fractal geometry, is widely used in the scientific and engineering communities to simulate chaotic events such as weather. Fractals are also

(hardware to software) into streams; and the addition of compiler directives to optimize the generated hardware. We subsequently used the CoDeveloper tool set to create the Pcore coprocessor that was imported into Xilinx Platform Studio (XPS). Using XPS,

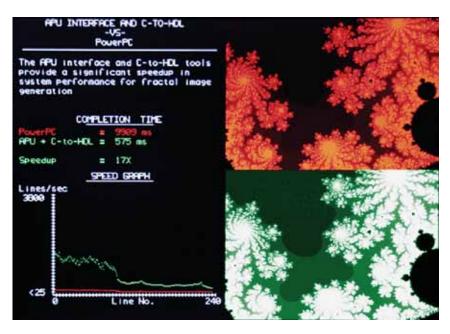

Figure 5 - Mandelbrot image and code acceleration

used to generate textures and imaging in video-rendering applications. Mandelbrot images are described as self-similar; on magnifying a portion of the image, another image similar to the whole is obtained.

The Mandelbrot image is an ideal candidate for hardware/software co-design because it has a single computation-intensive function. Making this critical function faster by moving it to the hardware domain significantly increases the speed of the whole system. The Mandelbrot application also lends itself nicely to clear divisions between hardware and software processes, making it easy to implement using C-to-HDL tools.

We used the CoDeveloper tool set as the C-to-HDL tool set for this design example. We modified a software-only Mandelbrot C program to make it compatible with the C-to-HDL tools. Our changes included division of the software project into distinct processes (independent units of sequential execution); conversion of function interfaces

we attached the PC to the PowerPC APU controller interface and tested the system.

Xilinx application note XAPP901 (www.xilinx.com/bvdocs/appnotes/xapp901.p df) provides a full description of the design along with design files for downloading. User Guide UG096 (www.xilinx.com/bvdocs/userguides/ug096.pdf) provides a step-by-step tutorial in implementing the design example.

#### **Performance Improvement Examples**

We measured performance improvements for the Mandelbrot image texturing problem, an image filtering application, and triple DES encryption. Table 2 documents the performance improvements, demonstrating acceleration ranging from 11x to 34x that of software.

#### Conclusion

Constrained by power, space, and cost, you might need to make a non-ideal processor choice. Frequently, it is a choice where the processor is of lower performance than desired. When the software code does not run fast enough, a coprocessor code accelerator becomes an attractive solution. You can hand-craft an accelerator in HDL or use a C-to-HDL tool to automatically convert the C code to HDL.

Using a C-to-HDL tool such as Impulse C enables quick and easy accelerator generation. Virtex-4 FX FPGAs, with one or two embedded PowerPCs, enable tight coupling of the processor instruction pipeline to software accelerators. As demonstrated in this article, critical software routines can be accelerated from 10x to more than 30x, enabling a 300 MHz PowerPC to provide performance equaling or exceeding that of a high-performance multi-gigahertz processor. The above examples were generated in just a few days each, demonstrating the rapid design, implementation, and testing possible with a C-to-HDL flow. •

| Application                             | PowerPC Only<br>(300 MHz) | PowerPC + Coprocessor<br>(300/50 MHz) | Acceleration |

|-----------------------------------------|---------------------------|---------------------------------------|--------------|

| Image Texturing<br>(Mandelbrot/Fractal) | 21 sec                    | 1.2 sec                               | 17x          |

| Image Filter<br>(Edge Detection)        | 0.14 sec                  | 0.012 sec                             | 11x          |

| Encryption<br>(Triple DES)              | 2.3 sec                   | 0.067 sec                             | 34x          |

Table 2 – Algorithm acceleration through coprocessor accelerators

# High VELOCITY LEARNING

Nu Horizons Electronics Corp. is proud to present our newest education and training program - XpressTrack - which offers engineers the opportunity to participate in technical seminars conducted around the country by experts focused on the latest technologies from Xilinx. This program provides higher velocity learning to help minimize start-up time to quickly begin your design process utilizing the latest development tools, software and products from both Nu Horizons and Xilinx.

For a complete list of course offerings, or to register for a seminar near you, please visit:

www.nuhorizons.com/xpresstrack

#### Courses Available

- Optimizing MicroBlaze Soft Processor Systems

- 3 hour class

- Covers building a complete customized MicroBlaze soft processor system

- Video/Imaging Algorithms in FPGAs

- 3 hour class

- Verify designs onto actual hardware using Ethernetbased hardware-in-the-loop co-simulation

- Introduction to Embedded

PowerPC and Co-Processor Code

Accelerators

- 3 hour class

- Covers how to build a high performance embedded PowerPC system

- Introduction to Programming FPGAs with ANSI C

- 4 hour class

- Covers an introduction to C for FPGAs

- Fundamentals of FPGA

- 1 day class

- Covers ISE 8.1 features

- ISE Design Entry

- 1 day class

- Covers XST, ECS, StateCAD and ISE simulator

- Fundamentals of CPLD Design

- 1 day class

- Covers CPLD basics and interpreting reports for optimum performance

- Design Techniques for Low Cost

- 1 day class

- Covers developing low cost products particularly in high volume markets

- VHDL for Design Engineers

- 1 day class

- CoversVHDL language and implementation for FPGAs & CPLDs

### Generating Efficient Board Support Packages by Rick Moleres Manager of Software IP

The Xilinx Platform Studio toolset enables quick and easy BSP generation for Virtex FPGAs with immersed PowerPC processors. rick.moleres@xilinx.com

Milan Saini Technical Marketing Manager Xilinx, Inc. milan.saini@xilinx.com

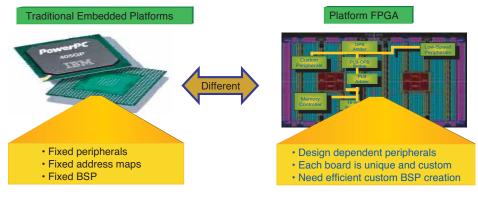

Platform FPGAs with embedded processors offer you unprecedented levels of flexibility, integration, and performance. It is now possible to develop extremely sophisticated and highly customized embedded systems inside a single programmable logic device.

With silicon capabilities advancing, the challenge centers on keeping design methods efficient and productive. In embedded systems development, one of the key activities is the development of the board support package (BSP). The BSP allows an embedded software application to successfully initialize and communicate with the hardware resources connected to the processor. Typical BSP components include boot code, device driver code, and initialization code.

Creating a BSP can be a lengthy and tedious process that must be incurred every time the microprocessor complex (processor plus associated peripherals) changes. With FPGAs, fast design iterations combined with the inherent flexibility of the platform can make the task of managing the BSP even more challenging (Figure 1). This situation clearly underscores the need for and importance of providing an efficient process for managing BSPs.

In this article, we'll describe an innovative solution from Xilinx that simplifies the creation and management of RTOS BSPs. We chose the WindRiver VxWorks flow to illustrate the concept; however, the underlying technology is generic and equally applicable to all other OS solutions that support Xilinx® processors.

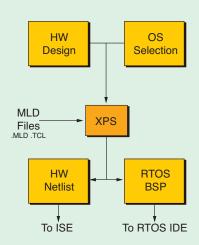

Figure 1 – Platform FPGA flexibility requires the software BSP generation process to be efficient.

#### Xilinx Design Flow and Software BSP Generation

Designing for a Xilinx processor involves a hardware platform assembly flow and an embedded software development flow. Both of these flows are managed within the Xilinx Platform Studio (XPS) tool, which is part of the Xilinx Embedded Development Kit (EDK).

You would typically begin a design by assembling and configuring the processor and its connected components in XPS. Once the hardware platform has been defined, you can then configure the software parameters of the system. A key feature of Platform Studio is its ability to produce a BSP that is customized based on your selection and configuration of processor, peripherals, and embedded OS. As the system evolves through iterative changes to the hardware design, the BSP evolves with the platform.

An automatically generated BSP enables embedded system designers to:

- Automatically create a BSP that completely matches the hardware design

- Eliminate BSP design bugs by using pre-certified components

- Increase designer productivity by jump-starting application software development

#### Creating BSPs for WindRiver VxWorks

Platform Studio can generate a customized Tornado 2.0.x (VxWorks 5.4) or Tornado 2.2.x (VxWorks 5.5) BSP for the PowerPC<sup>TM</sup> 405 processor and its periph-

Figure 2 – Setting the embedded OS selection

Figure 3 – Configuring the OS-specific parameters

Figure 4 – Generated BSP directory structure

erals in Xilinx Virtex<sup>TM</sup>-II Pro and Virtex-4 FPGAs. The generated BSP contains all of the necessary support software for a system, including boot code, device drivers, and VxWorks initialization.

Once a hardware system with the PowerPC 405 processor is defined in Platform Studio, you need only follow these three steps to generate a BSP for VxWorks:

- 1. Use the Software Settings dialog box (see Figure 2) to select the OS you plan to use for the system. Platform Studio users can select vxworks5\_4 or vxworks5\_5 as their target operating system.

- 2. Once you have selected the OS, you can go to the Library/OS Parameters tab, as shown in Figure 3, to tailor the Tornado BSP to the custom hardware. You have the option of selecting any UART device in the system as the standard I/O device (stdin and stdout). This results in the device being used as the VxWorks console device.

You can also choose which peripherals are connected peripherals, or which devices will be tightly integrated into the VxWorks OS. For example, the Xilinx 10/100 Ethernet MAC can be integrated into the VxWorks Enhanced Network Driver (END) interface. Alternately, the Ethernet device need not be connected to the END interface and can instead be accessed directly from the VxWorks application.

3. Generate the Tornado BSP by selecting the Tools > Generate Libraries and BSP menu option. The resulting BSP resembles a traditional Tornado BSP and is located in the Platform Studio project directory under ppc405\_0/bsp\_ppc405\_0 (see Figure 4).

Note that ppc405\_0 refers to the instance name of the PowerPC 405 processor in the hardware design. Platform Studio users can specify a different instance name, in which case the subdirectory names for the BSP will match the processor instance name.

25

March 2006 Embedded magazine

The Tornado BSP is completely self-contained and transportable to other directory locations, such as the standard Tornado installation directory for BSPs at target/config.

#### **Customized BSP Details**

The XPS-generated BSP for VxWorks resembles most other Tornado BSPs except for the placement of Xilinx device driver code. Off-the-shelf device driver code distributed with Tornado typically resides in the target/src/drv directory in the Tornado distribution directory. Device driver code for a BSP that is automatically generated by Platform Studio resides in the BSP directory itself.

Figure 5 - Tornado 2.x Project: VxWorks tab

This minor deviation is due to the dynamic nature of FPGA-based embedded systems. Because an FPGA-based embedded system can be reprogrammed with new or changed IP, the device driver configuration can change, calling for a more dynamic placement of device driver source files. The directory tree for the automatically generated BSP is shown in Figure 4. The Xilinx device drivers are placed in the ppc405\_0\_drv\_csp/xsrc subdirectory of the BSP.

26

## The Tornado BSP created by Platform Studio has a makefile that you can modify at the command line if you would rather use the diab compiler instead of the gnu compiler.

Xilinx device drivers are implemented in C and are distributed among several source files, unlike traditional VxWorks drivers, which typically consist of single C header and implementation files. In addition, there is an OS-independent implementation and an optional OS-dependent implementation for device drivers.

The OS-independent part of the driver is designed for use with any OS or any processor. It provides an application program interface (API) that abstracts the func-

Figure 6 - Tornado 2.x Project: Files tab

tionality of the underlying hardware. The OS-dependent part of the driver adapts the driver for use with an OS such as VxWorks. Examples are Serial IO drivers for serial ports and END drivers for Ethernet controllers. Only drivers that can be tightly integrated into a standard OS interface require an OS-dependent driver.

Xilinx driver source files are included in the build of a VxWorks image in the same way that other BSP files are included in the build. For every driver, a file exists named ppc405\_0\_drv\_<driver\_version>.c in the BSP directory. This file includes the driver source files (\*.c) for the given device and is automatically compiled by the BSP makefile.

This process is analogous to how VxWorks' sysLib.c includes source for Wind River-supplied drivers. The reason why Xilinx driver files are not simply included in sysLib.c like the rest of the drivers is because of namespace conflicts and maintainability issues. If all Xilinx driver files are part of a single compilation unit, static functions and data are no longer private. This places restrictions on the device drivers and would negate their OS independence.

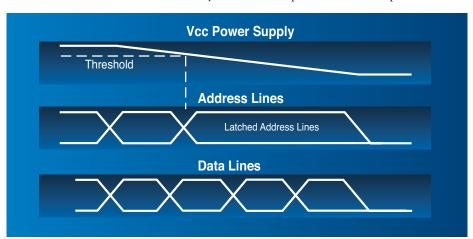

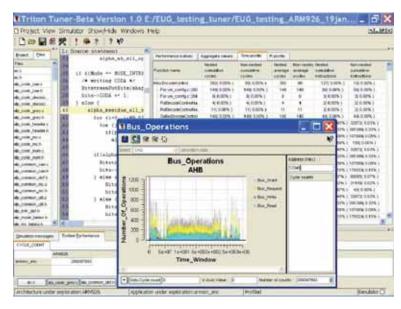

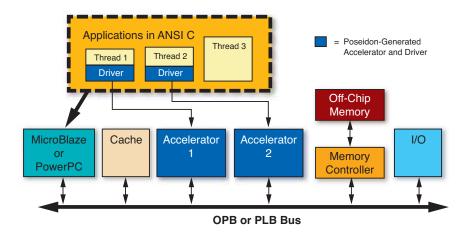

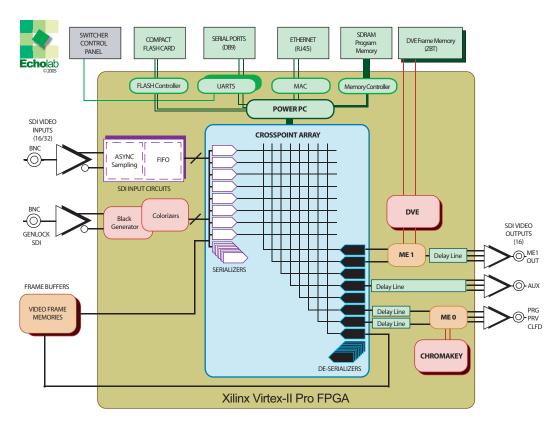

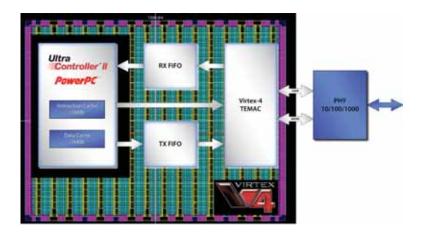

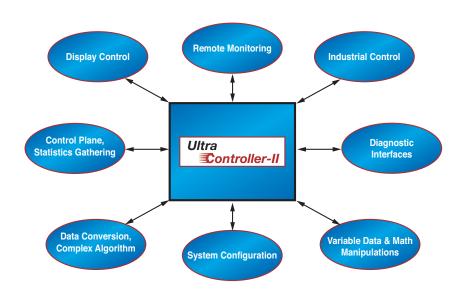

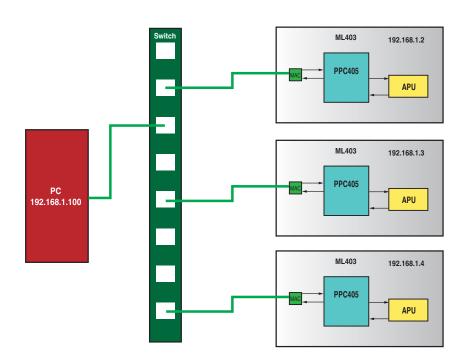

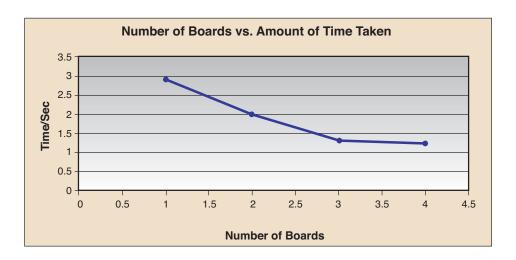

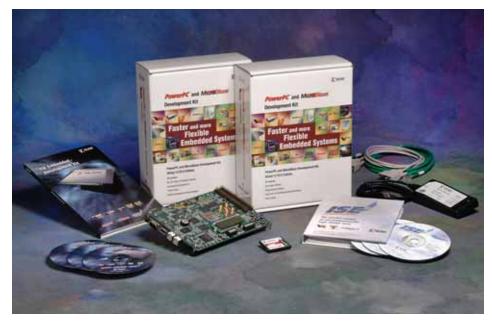

#### Integration with the Tornado IDE