### THE QUARTERLY JOURNAL FOR PROGRAMMABLE LOGIC USERS

Issue 32 **Second Quarter** 1999

### **NEW TECHNOLOGY**

The Design Software Revolution

> **ECTIVE HDL** Verification

**NEWS BRIEFS Real 64/66 PCI Solution** Virtex 8051 Core

**IEW PRODUCTS XC9500XV CPLD Family**

### TION

**Frequency Counter** Serial Communication Link

### **COVER STORY**

Silin Kongh Technology Three articles discuss the history of Xilinx and the programmable logic industry.

## FROM THE EDITOR

EDITOR Carlis Collins editor@xilinx.com 408-879-4519

### SENIOR DESIGNER

Jack Farage

#### **BOARD OF ADVISORS**

Dave Stieg Dave Galli Mike Seither Peter Alfke

### PUBLICATION SERVICES

Ruddle Creative 111 N. Market St., Suite 715 San Jose, CA 95113 Tel: 408-297-3000 or 1-800-7RUDDLE Web: www.ruddle.com

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3450 Tel: 408-559-7778 Fax: 408-879-4780 ©1999 Xilinx Inc. All rights reserved.

XCell is published quarterly. XILINX and the Xilinx logo are registered trademarks of Xilinx, Inc. Spartan, Virtex, Alliance Series, Foundation Series, AllianceCORE, LogiCORE, WebLINX, SelectRAM, SelectRAM+, LogiBLOX, FastFLASH, Silicon Xpresso, ChipScope, JBits, and all XC-prefix products are trademarks, and The Programmable Logic Company is a service mark of Xilinx, Inc. Other brand or product names are trademarks or registered trademarks of their respective owners.

The articles, information, and other materials included in this issue are provided soley for the convenience of our readers. Xilinx makes no warranties, express, implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against Xilinx for any loss, damage, or expense caused thereby.

### **Putting Things in Perspective**

Xilinx invented the FPGA just 15 years ago. Since then, programmable logic devices and development tools have changed dramatically. Today, using our million-gate, high-performance, system-level devices, you can create unique designs that were never possible before, get them to market sooner, and keep them in the market longer; your "window of innovation" is practically unlimited.

efore programmable logic, your window of innovation closed when your specification went to engineering because design changes were costly, often delaying product introduction. After FPGAs arrived, you could continue to add features right up to the time your design went to manufacturing, without causing delays or adding

costs. Today, with our new Virtex<sup>™</sup> FPGA family and our Internet Reconfigurable Logic<sup>™</sup> capability, you can continue to innovate, adding new capabilities even after your designs are in the field (including features you haven't even thought of yet). A lot has changed in the last 15 years.

In addition to lower costs, unprecedented device density, and higher performance, there

are a number of key factors that make today's programmable logic a key element in the life and profitability of new systems. For example, you can use a fast-growing assortment of intellectual property (cores) to quickly and inexpensively create the most complex and risky parts of your design. You can use a wide array of the most advanced timesaving development tools to enter, simulate, and debug your designs. Plus, along with Internet Reconfigurable Logic, there are a number of striking advances in the application of FPGAs that allow you to upgrade, test, and maintain your FPGA-based designs remotely, adding features and fixing bugs at your customers' locations, anywhere in the world, via the Internet—imagine the possibilities. In the past, custom ASICs were used for high volume, cost sensitive designs. FPGAs were just too expensive and they did not have the raw performance or logic density to make them compelling in many applications. Plus, the FPGA development tools were often difficult to learn and they lacked the high-level features found in ASIC development

In addition to lower costs, unprecedented device density, and higher performance, there are a number of key factors that make today's programmable logic a key element in the life and profitability of new systems.

systems. Now however, all that has changed.

FPGAs now compete very well, on price, performance, and ease of use against custom ASICs and even against many standard off-the-shelf devices. For example, using FPGAs, you can create DSP designs that far outperform any standard

DSP device, or create fully-compliant 64-bit/66-MHz PCI designs that cost less and outperform any standard PCI device. Plus, FPGAs offer you the key advantage of profitability: you can get your product to market sooner and keep it in the market longer than with any other method—period.

High performance, high density, cutting-edge innovation, ease-of-use, unique new applications, faster time-to-market, longer time-in-market, peace of mind-that's what you get from today's systemlevel FPGAs and development tools from Xilinx.

This issue of *Xcell* is intended to show you how far the programmable logic industry has progressed. I wonder what the next 15 years will bring... **£**:

## ARTICLES

## **COVER STORY**

A lot in the PLD industry has changed since Xilinx was founded in 1984. Three stories review the history of Xilinx and PLDs.

### NEW TECHNOLOGY New FPGA technologies have drive

New FPGA technologies have driven the demands on design software, yielding a new generation of synthesis, simulation, place and route and other tools for PLD designers.

## PERSPECTIVE

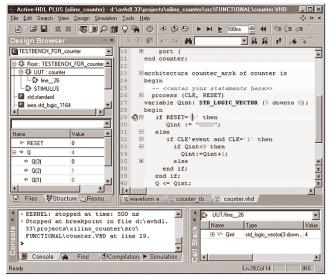

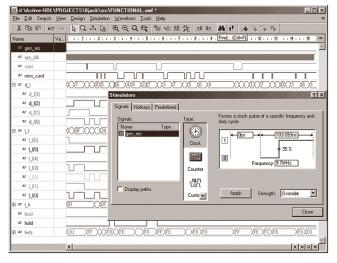

The new generation of HDL verification tools handle larger design files, while requiring less time for the simulation process.

### **NEWS BRIEF**

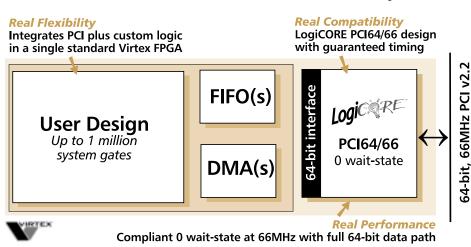

Our new PCI cores, called the Real 64/66 PCI solution, meet the demand for uncompromising compliance, flexibility and performance.

### **NEW PRODUCTS**

The XC9500XV family of high-perforance 2.5V CPLDs provide power savings of up to 75% over today's 5V CPLDs, at a lower cost.

### Inside This Issue:

| 15 Years of Innovation 4                            |

|-----------------------------------------------------|

| The Evolution of PLDs 5                             |

| Times Have Changed9                                 |

| Silicon Xpresso: Internet<br>Reconfigurable Logic10 |

| Internet Appliances13                               |

| FPGA Synthesis14                                    |

| Design Software Revolution 16                       |

| Concept HDL 19                                      |

| VeriBest's Vision21                                 |

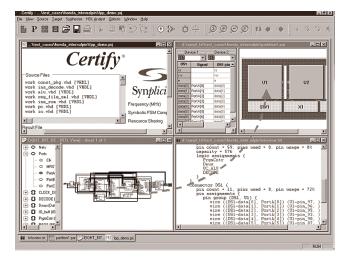

| Prototyping with Certify24                          |

| HDL Verification27                                  |

| Converting FPGAs to ASICs 30                        |

| Relative Location Constraints 31                    |

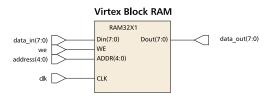

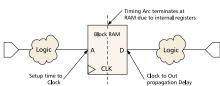

| Inferring Virtex Block RAM 34                       |

| Third-Party Virtex Cores                            |

| Success Story: SmartTouch 36                        |

| 8051 Core for Virtex                                |

| 32-Bit Ethernet Switch                              |

| SpartanXL and Video Apps 39                         |

| Success Story: Wildstar 40                          |

| Real 64/66 PCI 41                                   |

| Success Story: 3D Graphics 43                       |

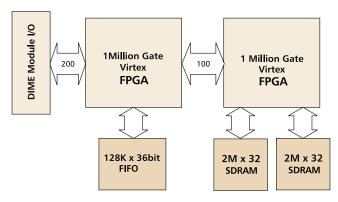

| Single DIME Module44                                |

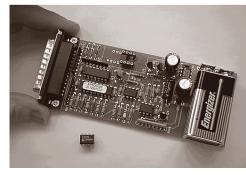

| Low-Cost PROM Programmer 45                         |

| XC9500XV CPLDs                                      |

| 400MHz Frequency Counter 47                         |

| Serial FPGA Com Link 50                             |

| Save Register Content During<br>Power-Down52        |

| Determining Clock Skew                              |

| FPGA IP Center 55                                   |

| Column: HDL Advisor                                 |

| Verilog Training58                                  |

| Trade Show Programs 59                              |

| Device Selection 60                                 |

| Software Selection62                                |

For A FREE Subscription To The Xcell Journal

### E-mail your request to: literature@xilinx.com

Please be sure to include: ——

- 1. Your Full Name and Mailing Address

- 2. Your Title

- 3. The Name of Your Company

- 4. Your E-mail Address

- 5. Is This a New Subscription or

- a Subscription Renewal?

## **15 Years** of Innovation

by Wim Roelandts, CEO, Xilinx

> Xilinx invented the FPGA just 15 years ago. Since that time, we have seen dramatic advances in device performance and density, while prices have steadily declined. These breakthroughs, combined with matching advances in our development tools, intellectual property, and support technologies, have created a revolution in logic design.

ur first FPGA, the XC2064, was shipped in 1985; it offered 800 gates, sold for \$55, and was produced on a 2.0µ process. We have been shipping that device for 15 years and today it sells for just \$5. Our latest generation of FPGAs, the Virtex family, is produced with a leading 0.22µ fabrication process, and offers

advanced system-level features with densities over one million gates. Virtex FPGAs, along with our new Internet Reconfigurable Logic (IRL) technologies, are creating new design possibilities that no one could have dreamed of back in 1985.

Our use of the most advanced process technology is a key element of our aggressive development plan. For example, in 1997 our  $0.35\mu$  XC4000XL family went from concept to production in less that a year, the fastest product development effort in our history. With the XC4000XL family, Xilinx became the first company in the industry to ship a complete new line of ten 3.3V FPGAs. Our XC4085XL, the largest member of that family, provides up to 180,000 system gates.

By the end of 1997, we began shipping our XC4000XV family, the industry's first 0.25µ FPGAs, offering densities of up to 500,000 system gates. In 1998 we began shipping our Spartan family, the lowest cost FPGAs, ever. Today we are shipping million-gate, 0.22µ Virtex devices, and we have 0.18µ devices, operating at gigahertz speeds in our laboratories. This rapid pace of product development demonstrates our commitment to innovation, backed by the highest research and development budget of any company in our industry.

Xilinx is unquestionably the technology leader in producing the most innovative programmable logic devices. However, it takes much more than devices to capture the minds and imaginations of today's engineers. That's why we continue to push the boundaries of technology in the key areas that make programmable logic compelling and useful. We now have the most productive tools, with the shortest compile times in the industry, and we are continuously expanding our list of intellectual property (cores), so you can go from concept to full production faster and with less effort than ever before. In addition, we are creating new enabling technologies such as Internet Reconfigurable Logic that allow you to develop and test your designs remotely; you can now add features or fix bugs at your customers' locations, anywhere in the world, over the Internet. This not only extends the life of your product, it also creates exciting new possibilities for products such as Internet-based "appliances."

Our goal is to bridge the gap between your imagination and the physical world. We do this by making it as easy as possible for you to create the most advanced systems, get them to market sooner, and keep them in the market longer. Soon we will offer two-million gate devices, team-based development tools, and many more ways to use programmable logic in new and unique applications.

The future is close and arrives very quickly these days. **£**

### **Major Xilinx Milestones**

- 1984 Xilinx is founded by Bernie Vonderschmitt, Jim Barnett, and Ross Freeman.

- 1985 Introduced the XC2000 series, our first family of field programmable gate arrays (FPGA).

- 1987 Introduced XC3000 series, our second family of FPGAs.

- 1988 Established a subsidiary in Japan.

- 1989 More than one million FPGA devices sold.

- 1990 Initial public offering.

- 1991 Introduced XC4000 series, third family of FPGAs.

- 1992 Expanded into market for complex programmable logic devices (CPLDs).

- 1993 Established a subsidiary in Hong Kong.

- 1995 Ranked world's 10<sup>th</sup> largest ASIC supplier; Xilinx Ireland facility opens.

- 1996 Ranked world's 8<sup>th</sup> largest ASIC supplier; Wim Roelandts joins as CEO.

- 1997 World's  $1^{st}$  0.35 and 0.25 $\mu$  FPGAs.

- 1998 Introduced Spartan and Virtex FPGAs, unveiled Internet Reconfigurable Logic.

- 1999 Xilinx celebrates 15<sup>th</sup> anniversary; introduced XC9500XV, 1<sup>st</sup> 2.5V CPLD family.

## EVOLUTION of Programmable Logic Design Technology

A historical perspective on the evolution of Xilinx development systems and design methods.

by Craig Willert, High Volume Solutions, Software Market Manager, Xilinx, cnw@xilinx.com

ith the introduction of the first programmable LCA (Logic Cell Array) in 1985, Xilinx changed the course of electronic design. This innovative new technology allowed engineers to design a single chip that performed the equivalent function of a typical printed circuit board. While this creative use of silicon has been heralded as a breakthrough technology that created a new industry, many insiders will tell you that it was the methodical delivery of innovations in the development systems tools that has enabled so many engineers to take advantage of programmable logic.

### **Development System Timeline:**

| Year | Key Features                                                                                                                                                                                                                 | Associated<br>Design Flow                                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1984 | Xilinx Design Editor                                                                                                                                                                                                         | Physical Design Editor/<br>PIP Poking                                                                                                 |

| 1986 | XNF2LCA1.0, APR1.0,<br>XACTOR 2                                                                                                                                                                                              | Schematic based design,<br>automatic logical to physical<br>design translation, automatic<br>place and route, in-circuit<br>debugging |

| 1988 | XNFBA                                                                                                                                                                                                                        |                                                                                                                                       |

| 1990 | XMAKE, Guided Design,                                                                                                                                                                                                        | Automatic Design Implementa-<br>tion, Map-then-Merge, XDM                                                                             |

| 1992 | Unified Libraries, XBLOX,<br>Hard Macros                                                                                                                                                                                     | XACT 5 – Batch<br>XACT 6 – Windows (DM/FE)                                                                                            |

| 1994 | XACT Performance, RPMs,<br>DM/FE, Floorplanner                                                                                                                                                                               |                                                                                                                                       |

| 1995 | Foundation Series introduction,<br>Software Localization (Japanese)                                                                                                                                                          |                                                                                                                                       |

| 1996 | MAP, PAR, MPPR, Implementation<br>Engine, EDIF, VHDL, and Verilog<br>standards, LogiBlox, PCI LogiCore,<br>ITA, JTAG, FPGA Express, Core<br>Generator, Constraints Editor,<br>Floorplanner (reintroduced),<br>Foundation UPM |                                                                                                                                       |

When Xilinx introduced its first Logic Cell Array in 1985, the Electronic Design Automation (EDA) industry was focused on delivering schematic capture and gate-level simulation tools to simplify the process of logic design. Although it was considered important to provide an easy to use design solution, the first priority of Xilinx was to enable its customers to gain

access to the full complexity of its programmable logic devices. Xilinx first developed a physical design tool – XACT 1.0. This tool, which later became known as XDE (Xilinx Device Editor), gave designers the ability to view, edit, and highlight all of the logic and routing resources within a device. Furthermore, XDE featured advanced "high-

...the first priority of Xilinx was to enable its customers to gain access to the full complexity of its programmable logic devices.

level" design capabilities such as Boolean expression, Karnaugh Map, and truth table design (graphically crosscoupled, no less).

The use of XDE ushered in the era of a design methodology that may be characterized as "PIP-poking" (Physical Interconnect Point). XDE's introduction was also responsible for the development of a new breed of designers – "Xilinx experts," who not only were unique in their understanding of the Xilinx design methodology, but also in their detailed understanding of Xilinx programmable logic devices.

Continued on the following page

As the use of programmable logic devices became popular, and it became clear that the Programmable Logic business was viable, Xilinx turned its attention towards improving the LCA design methodology so that designers could take better advantage of the time-to-market benefits that programmable logic offers. To tackle this problem, Xilinx developed a set of design tools that would handle the translation of a design from its logical form (represented as a schematic) to the physical structures that exist within the Logic Cell Array. This spurred the creation of the "PIN2LCA, XNF2LCA, and APR programs.

### PIN2LCA

The first qualified "front-to-back" design environment for Xilinx logic devices was created to work with Futurenet, a leading schematic capture tool at the time. Through the first "EDA Alliance," Xilinx and Futurenet were able to create an automatic logical netlist (logic gates and registers) to physical netlist (configured CLBs and IOBs) translation tool (PIN2LCA). By allowing an engineer to focus on designing their required circuitry using schematic capture rather than the Xilinx Design Editor, the use of programmable logic became a viable design methodology for many more designers.

### Xilinx Netlist Format and XNF2LCA

In addition to working with Futurenet to develop a proprietary design flow, Xilinx recognized the need to work with other EDA companies. The Xilinx Netlist Format (XNF) was introduced in order to provide a standard for transferring a design database from any schematic package to the Xilinx design environment. Of course, to leverage this netlist standard, Xilinx had to develop the netlist translation program XNF2LCA, completing the transformation of a design from the logical database to the physical (LCA) database.

Through the publishing of this standard, and the creation of the XNF2LCA program, Xilinx ensured that any EDA company that could create XNF files would be in a position to offer advanced design methods for Xilinx devices.

##

With the introduction of the XC3000 family, the density and complexity of the Xilinx programmable logic devices increased dramatically. Recognizing the associated growth in complexity of the programmable logic design methodology, Xilinx introduced a number of innovations to help ease the computing burden. The innovations included Automatic Place and Route, Map-then-Merge, XBLOX, Guided Design methodologies, and the XMAKE program.

### Automatic Place and Route

To complete the automation of the layout of Xilinx logic devices, Xilinx developed the industry's first Automatic Place and Route (APR) program. APR 1.0 simplified the programmable logic design process by relieving the engineer of the time consuming tasks of identifying which CLBs within a LCA would contain the design's logic, and interconnecting them to other CLBs and IOBs. With the delivery of this program, the Xilinx design process went from being manual and interactive to being automated and batch oriented.

### Map-then-Merge

Acknowledging the limitations of the performance of the typical engineer's computing platform, Xilinx patented a modular design method which is known as the Mapthen-Merge approach. Taking clues from the source design's hierarchy, the Map-then-Merge approach divides the technology mapping task into smaller units, thus increasing the algorithmic throughput, and improving the processing time for designing complex programmable With the introduction of the XC3000 family, the density and complexity of the Xilinx programmable logic devices increased dramatically.

logic circuits. Furthermore, by separating the XNFMAP program from the XNFMERGE program, designers could discover the cause of any design errors more easily.

### **XBLOX**

In an era where design reuse, and the inclusion of 3<sup>rd</sup> party Intellectual Property (IP or Cores) is at an all time high, it is interesting to review the XBLOX design tool that Xilinx offered its customers so long ago. In what was one of the industry's first high-level design methodologies, Xilinx patented an innovative mechanism for performing parameterized design using schematic capture. XBLOX allowed engineers to create a design with "n-width" buses, which could be specified in a single location within the schematic. The bus width parameter would then be propagated through the design, based on the designer's specifications. The propagation (or forward annoation) of the bus width parameter simplified the process of modifying a design's functionality by localizing this type of change to one design element.

XBLOX also included the ability to specify area or speed optimization of its functions on a "core-by-core" basis. The

In the era of schematic design and batch mode processing, Xilinx offered both interactive-based (GUI) processing and command line access to the algorithms that were required to layout Xilinx FPGAs.

XBLOX compiler was rerun at the time of layout, whenever design iteration called for a modification in the XBLOX specification or target device.

### **Guided Design**

Attempting to accelerate the process of iterating on a design, Xilinx accelerated the place and route process by delivering the Guided Design capability. Guided Design allows an engineer to leverage the results from an earlier place and route run in the layout of his next version of an FPGA. While not effective in all design flows, this initial guided design technology proved to be very effective in accelerating the placement and routing of most FPGA design's when only small (iterative in nature) changes were required to a schematic.

### XMAKE

In the era of schematic design and batch mode processing, Xilinx offered both interactive-based (GUI) processing and command line access to the algorithms that were required to layout Xilinx FPGAs. However, unless a designer was sitting in front of a design flow chart, the sequence of commands was not always easy to remember. To further simplify the programmable logic design process, Xilinx introduced the XMAKE program. XMAKE was designed to perform date stamp analysis, and to automatically run any out of date step in the design flow.

With the mainstream use of Programmable Logic Devices came a growing hunger for performance and efficiency in the use of silicon. To help its customers take advantage of the density and performance of Xilinx Logic devices, Xilinx introduced a set of tools that allowed an engineer to provide more information about a design to the layout tools. Armed with the new information provided by TimeSpecs, Relationally Placed Macros (RPM), and the Floorplanner, the layout tools were more prepared to focus on the true design requirements.

### **XACT Performance**

Prior to the introduction of XACT Performance and TimeSpecs, skilled programmable logic designers manually placed and routed a design, or played tricks with a signal's "net criticality" in order to improve a circuit's performance. XACT Performance changed all of this by allowing design engineers to specify the circuit's performance criteria using Timespecs. Given this new information, the XACT Performance place and route tools were able to algorithmically evaluate the suitability of various layouts. While this processing required more CPU time, batch mode processing freed the designer to attend to the other requirements of his job, thus improving design time and time to market.

### Floorplanner

Xilinx introduced another revolutionary capability to the programmable logic design market with the release of the XACT Floorplanner. The Floorplanner enabled a designer to impart his expert knowledge of the design as guidance to the

layout process, thus simplifying the increasingly complex problem of logic placement. Advanced programmable logic designers found that by "seeding" the placement of a small portion of a design, they could improve circuit performance by up to 25%, and cut place and route run times in half. Furthermore, the Floorplanner proved to be an excellent tool for analyzing a design's logic and routing density, providing insight into the suitability of a design for future enhancements.

###

With the introduction of powerful Pentium processors, and the Windows operating systems, the use of personal computers as engineering workstations became common. To foster the adoption of its operating system, Microsoft established standards for GUIs that would enable first time users of an application to feel comfortable in learning to use any new product which was designed using these standards.

With ambitions of expanding the market for programmable logic, Xilinx developed a GUI for the XACT implementation tools that adhered to MFC standards. In addition to creating a GUI which simplified the means by which the tools were run (Xilinx Flow Engine), Xilinx also added a variety of design management capabilities to this tool set, simplifying the process of managing a design's source and object files (Xilinx Design Manager).

Xilinx acquired the advanced FPGA implementation technology and resources of NeoCAD to more rapidly deliver state of the art support for a growing number of devices. The result of merging the technology and resources of these two companies

has been the creation of a powerful, fast, timing-driven set of implementation tools for both CPLDs and FPGAs. Some key software milestones that have occurred

directly as a result of the acquisition:

- The first release of software support for new Xilinx architectures and devices in advance of sample silicon.

- The development of the first FPGA that has been optimized for fast and efficient layout, by customers using pushbutton design flows.

- The creation of the industry's best standards-based interface for working with 3<sup>rd</sup> party EDA providers, including EDIF, VHDL, Vital, Verilog, and SDF.

- The development of advanced performance driven algorithms that now run ten times faster than previous releases of XACT and NeoCAD Foundry implementation tools.

- The first localization of programmable logic tools for the Japanese market.

##

Shortly after Xilinx and NeoCAD joined forces, Xilinx introduced its new suite of tools for the design of programmable logic devices — the Foundation Series.<sup>™</sup> The Foundation Series software included all of the basic necessities required of

an easy-to-use design package, plus some capabilities that only the most advanced EDA companies were offering. The product was so well received that within the first two years, Xilinx had shipped over 10,000 seats.

To improve the Foundation Series quality of results, Xilinx signed an OEM agreement with Synopsys, Inc. for the inclusion of its FPGA Express<sup>™</sup> FPGA Express strengthened the Foundation Series by enabling engineers to design with VHDL, Verilog, or a mixture of the two languages — a trend that has become more popular as device densities have skyrocketed, causing more people to turn to design reuse methodologies.

### —1997— The Xilinx CORE Generator™

As a result of the close working relationships with its foundries and the inherent advantages of using programmable logic as a process leader, Xilinx devices leapt to the forefront of process technology. The immediate benefit of this process leadership role to Xilinx and its customers was rapid advancements in device densities and performance. These benefits positioned Xilinx as a viable alternative for the heart of many state of the art electronic systems. As such, developers of emerging standards began turning to Xilinx as a potential provider of qualified solutions. This in turn spurred the creation of the Xilinx LogiCore and Alliance Core programs. Rather than merely being a conduit for marketing qualified VHDL and Verilog designs, Xilinx core programs focussed on developing a flexible, parameterized core delivery capability, where hard, soft, and firm cores are all made available to customers through a tightly integrated design interface - the Xilinx CORE Generator.

### Conclusion

Xilinx has made key advancements in both device and software technologies, and our programmable logic solutions will continue to lead the industry for years to come.  $\mathbf{x}$

### PERSPECTIVE

HOW

by Paul Gigliotti, Xilinx Applications Engineer, Xilinx, giglio@xilinx.com

n 1986, not long after slide rules went out of style, one of my first assignments as an engineer was to design an ASIC for an industrial controller. The design was entered into schematics using an 8086-based PC. Simulation was accomplished using a hardware accelerator that could run just over 100 test vectors a second. We only had one hardware accelerator, with two ASIC designs going on at the time. Because my project had lower priority, I had to work nights to guarantee access to the accelerator. Otherwise, I had to use the PC-based simulator, capable of about two to three vectors per second. If I had not worked nights, I might still be simulating that design. 15

mes

My first ASIC design used approximately 2,000 gates, ran at 10 MHz, and had 20 TTL level I/Os. NRE for the chip was around \$15,000 and the chip price was about \$15.00. The design took six to eight hours to place and route on a PDP-11 mainframe computer. At that time FPGAs had been available for about a year and using two XC2018s would have offered a \$130 solution to the problem. However, FPGAs were too new, and too expensive to be a viable contender for this design. Besides, who was this company Xilinx, and would they be around in 10 years, at the end of this product's life cycle?

About five years later, I designed a video acceleration card and used a Xilinx XC3090 to perform a pixel mixing algorithm. By this time FPGAs were considered a proven commodity, and Xilinx was a "household word" in the engineering community. The design used approximately 7000 gates, ran at 25 MHz, and had 95 TTL level I/Os. The chip cost was about \$150. At that time, the Xilinx XACT software, running on a 33 megahertz 80386, could place the design in four to six hours. My compile times had dropped significantly, and I could do it on my desktop, instead of on a mainframe, and I was able to work daylight hours. This was real progress.

nto implemented in VHDL. As we talked, I targeted the design at the Virtex family, using the Foundation Express software. The design had nearly 150 I/Os, with 96 of them being GTLcompatible. I was able to fit the design into a 50,000 gate Virtex device, as we talked, and the design ran a over 100 mergahertz. Overall L placed and routed the

On a recent customer visit, an engineer gave me a design

Now it's 1999 and I've been a Xilinx employee for three years.

has changed<br/>for XilinxAover the past1515 years. The<br/>ASIC vendor15that I had<br/>used in my15first design16has disap-<br/>peared, tak-<br/>ing the ASIC17with it.17

Reminiscing about the "good old days.

compatible. I was able to fit the design into a 50,000 gate Virtex device, as we talked, and the design ran at over 100 megahertz. Overall, I placed and routed the design three times on my notebook computer, during our 2 hour meeting. It's amazing how the world has changed for

It's amazing how the world has changed for Xilinx over the past 15 years. The ASIC vendor that I had used in my first design has disappeared, taking the ASIC with it. On the other hand, the Xilinx XC2018 was in full production until about two months ago. I've gone from using a room full of computers to place and route a 2000 gate ASIC to using a 10 pound notebook computer to place and route a 50,000 gate Xilinx FPGA. Design speeds have jumped from a few megahertz to over 100 MHz. Compile times have been drastically reduced from a work day to a coffee break. In 1985, a 64bit shift register would consume an entire XC2064,

today it would fit in a single Virtex CLB.

Of course, technology keeps marching on. We already have two-million gate devices on the drawing board, and in our laboratories, we have devices running at gigahertz speeds. Our development software is continually being improved, both with our in-house development and with tools and technologies from our EDA partners. And, we continue to create new enabling technologies such as our Silicon Xpresso software that allows you to modify and test your FPGA designs, at your customers' locations, anywhere in the world, over the Internet.

There's no end in sight to the possibilities offered by programmable logic.  $\boldsymbol{\xi}$

Here's how Xilinx is using the Web to provide 21st century tools and applications.

by Wallace Westfeldt, Product Manager for Internet Reconfigurable Logic, Xilinx, wallace@xilinx.com

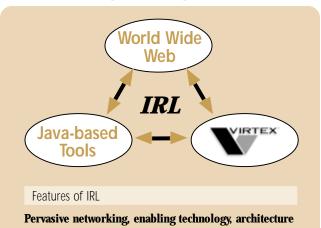

ast September, we announced our Silicon Xpresso initiative to create interactive Web-based tools and services that leverage the power of the Web for speedier design development. Then, in October, we announced our award winning Internet Reconfigurable Logic (IRL) applications, which enable you to upgrade digital products over any network. This article provides a summary and status of both Silicon Xpresso and IRL.

### Silicon Xpresso

Silicon Xpresso is a suite of Internet-enabled tools that leverage the Internet and the Web to make you more productive. These tools include WebFitter, all the Internet-enabled software releases since 1.5i (which connect to support.xilinx.com), and Internet Team Design.

### WebFITTER

WebFITTER is a free, Web-based CPLD fitter that runs on Xilinx in-house secure servers. It includes all of the features contained in the latest Xilinx development software, currently version 1.5i of our Alliance Series<sup>®</sup> and Foundation Series<sup>®</sup> tools. By simply submitting your CPLD designs via the Internet, Xilinx can quickly and efficiently "fit" your design into any XC9000 series CPLD device.

WebFITTER is fast, it's easy to use, it requires almost no learning curve, and it is always up to date with our latest enhancements. Therefore, it allows you to evaluate your CPLD designs in Xilinx XC9000 series devices with very little effort. You can easily make informed decisions and choose the best CPLD for your particular needs. With WebFITTER you can focus your creativity where it produces the best results — on your front-end design — leaving the back-end fitting and software management to us. It costs you nothing to use WebFITTER, the reports, or the device programming files that we create for you.

### support.xilinx.com

Starting with release 1.5i in October 1998, Xilinx software releases are "Internet-enabled." Simply by clicking on the help menu of the Alliance Series Design Manager or the Foundation Series Project Manager you have immediate access to support.xilinx.com, our designer-centric website.

On support.xilinx.com you can quickly find the answers you need from our Answers<sup>™</sup> database containing over 3000 records. You can easily construct online searches of this database or search all available application notes, expert journals, data sheets, on-line manuals, and articles from our Xcell Journal. To help you quickly finish your design, support.xilinx.com also provides:

- **Troubleshooting Tools** powerful search engines updated daily.

- Software Updates the latest files and service packs, for your convenience.

- Searchable Library volumes of reference materials harnessed through advanced search engines.

- Education Services just-in-time training, when you need it.

- On-line documentation software documentation for your convenience.

- **A "what's new" section** so that you can make sure you have the latest information.

Be sure to visit support.xilinx.com frequently and keep your design on track.

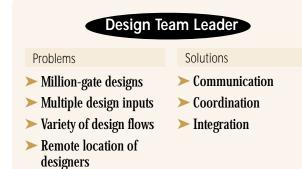

The solution to these challenges lies in efficient and asynchronous communication, an infrastructure for coordinating multiple inputs, and the ability to integrate a variety of design files.

### 21st Century Design Challenges

### Internet Team Design (ITD)

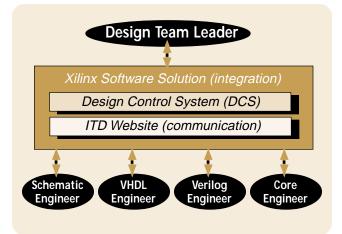

Coming this summer, with the 2.1i release of our Alliance Series and Foundation Series software, is a development option called Internet Team Design (ITD). ITD is designed to help today's hardware design teams deal with tomorrow's application challenges that include very large and complex designs, where each team member contributes to different aspects of the design and may frequently work from different flows, from a remote location. The solution to these challenges lies in efficient and asynchronous communication, an infrastructure for coordinating multiple inputs, and the ability to integrate a variety of design files.

The Internet, and its cousin a secure *Intra*net, combined with the Xilinx ITD development option, allows your team to work closely together regardless of location or design flow. Combining Java-based technology with powerful Xilinx implementation tools, ITD forms an HTML-based communications layer that allows you to communicate asynchronously and remotely with your project leader. Then, your inputs and project reports are maintained by an automated Design Control System which allows individual team members to

### 21st Century Design Solution

check-in their interactive designs simply by using their Web browser. And then finally, these designs are integrated into the application using the Xilinx Software Solution.

### Internet Reconfigurable Logic

Imagine having the ability to remotely upgrade, test, and repair your logic designs anywhere on earth, or above the earth (for a satellite application perhaps). This is not tomorrow's dream; this is today's reality. To facilitate and expand this reality, Xilinx has created a systems approach called Internet Reconfigurable Logic (IRL). IRL is the combination of pervasive networking, our enabling software technology, and our advanced programmable logic architecture to provide programmable logic systems that can be easily modified, upgraded, and tested after your systems have been deployed.

### Internet Reconfigurable Logic

IRL systems bring six key added values to a programmable logic application:

- 1. Shorter Time to Market by allowing earlier releases of your systems, that can be upgraded later.

- **2. Extended Time for Revenue** by allowing modification of your system, after the release.

- **3.** Lower costs by not requiring the retooling or redeployment of devices, particularly in remote or widespread locations.

- **4.** Lower costs by eliminating the most expensive stage of manufacturing-in-system test.

- **5. Expanded application opportunities** by leveraging personalized network applications.

- 6. Increased revenue by allowing you to charge for incremental system upgrades. The Internet usage business model is similar to the model used for cellular phones and cable TV.

### **NEW TECHNOLOGY – SOFTWARE**

### Spectrum of Reconfiguration

| ONCE IN A WHILE | PERIODIC    | FREQUENT | RUN-TIME            |

|-----------------|-------------|----------|---------------------|

| Field Upgrades  | Rapid Des   |          | Mobile Applications |

|                 | Data Proces | ssing    | Network Appliance   |

### **Reconfiguration Requirements**

When creating an IRL system, it's important to analyze your reconfiguration requirements. It may be that you only need to do in-system test before going online. Or, you may need to do incremental or periodic upgrades of the device either for maintenance or for selling added value. You may also want to do network reconfiguration because the system has remote or multiple deployment sites, as used in cellular phone base stations or orbiting satellites. The foremost consideration in all these examples is the frequency of reconfiguration.

The spectrum of reconfiguration spans a wide range of frequency and applications:

- **Field reconfiguration** is generally not time dependent, but it has the most pervasive application. It can be used for updates, bug fixes, and adding new functionality to your digital hardware.

- **Periodic reconfiguration** can be used for those applications where there is a regular change of supporting data, such as environmental monitoring systems, GPS, and so on.

- **Frequent reconfiguration** can be used to accelerate data processing for applications such as image processing.

- Runtime reconfiguration can be used where your application relies on changing variables such as detecting network protocols in a mobile application or interrupting operation with new functionality because a security or safety sensor has been triggered.

In many of these examples you need to reconfigure part of the FPGA while the rest of your logic remains the same. This is called "partial reconfigurability" which is provided by the Virtex architecture.

For field upgrades and even partial reconfigurations it is completely feasible to use standard development flows. On our IRL website (http://www.xilinx.com/products/software/sx/ sxpresso.html) you can access application notes that describe several methods for field upgrades and partial reconfiguration. For IRL systems that require either multiple device updates or rapid reconfiguration you might consider using portable Javabased tools such as the "Java API for Boundary Scan" or JBits. Check our IRL website for updates on these technologies.

In addition to the frequency of reconfiguration there are a number of other equally important items to consider such as:

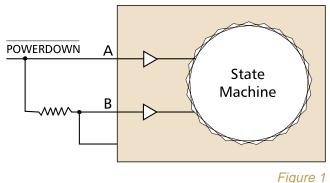

System Level Planning – Your system must be designed to allow in-system programming of the reconfigurable logic devices. The JTAG programming interface (available on all of the latest Xilinx FPGAs and CPLDs) is a good universal choice (see Java API for Boundary Scan), especially if you have multiple reconfigurable logic devices.

You also need to have some way of getting the new bits into your system. The new configuration could be provided manually and loaded through some external interface on the system. If the system is on a network or has other communication capability the new configuration could be loaded remotely.

• **Reconfigurable Logic Planning** – With planning, a circuit design implemented in reconfigurable logic can be changed and still fit in the same part, operate at the same speed, and require the same I/O. However, it does require planning at design time. There are some obvious general guidelines, such as reserving gate and flip-flop capacity for future expansion, and having some timing margin. Understanding and anticipating the kinds of changes that may be required in the future is key.

### Conclusion

Xilinx is dedicated to creating  $21^{st}$  Century design tools for  $21^{st}$  Century applications. We are the innovation leader, providing enormous opportunities for you, and helping you provide insanely great applications. *The revolution is brewing, have a cup on us.* **X**

Contributors: Alan Frost, Steve Guccione, Neil Jacobson, Steve Lass, Delon Levi, Scott Lewis, Frank Toth, Alica Tripp

## With the advent of ITAC test circuitry

With the advent of JTAG test circuitry, In-System Programming, and Internet Reconfigurable Logic, we are witnessing the dawn of the Internet Appliance era.

by Jesse Jenkins, CPLD Applications Manager, Xilinx, jesse@xilinx.com

As Xilinx celebrates its 15th anniversary, many new applications for programmable logic are emerging while traditional ways of designing and developing systems are quickly fading away. Many new systems are being designed to allow continuous hardware upgrade capability, over the Internet, giving them unique new capabilities and a longer life span. It's easy to envision "universal" systems that can easily change functions to become anything you can imagine.

### **Examples of Internet Appliances**

An Internet Appliance is any hardware device that relies upon either an Internet connection or upon access to Internet information files to achieve its functionality. The "Rocket eBook," "Rio," and "PalmPilot," and are good examples:

- The Rocket eBook is one of several hardware devices that display downloadable text. Packaged in a book size format, it's basically a retrieval, storage, and display device relying on dense, low power electronic memory.

- Rio is the musical version of Rocket Book. In a package the size of a telephone pager, you can pack MP3 audio files for playing CD quality sound with no moving parts, and therefore no skipping tracks. The key to its success is FLASH EPROM memory, very similar to that used in Xilinx FastFLASH XC9000 family CPLDs.

- The PalmPilot continues to be the leading Personal Digital Assistant (PDA), using access to Netscape and the Web to collect software and files and then use them when needed at some future time.

It's easy to imagine a single, FPGA-based device that can perform any of these functions, as well as functions that have not been thought of yet, easily adapting to entirely new applications, downloaded from the Web. The universal Internet Appliance is not only possible, it's inevitable.

are Limitless

**Important PLD Features**

Xilinx FPGAs and CPLDs are primed to play a key role in this market, and many are already used in a variety in Internet Appliances. The key attributes that make this possible, include:

- Low power for battery powered applications.

- Internet software support for Internet Reconfigurable Logic (IRL) applications.

- Reliable In-System Programming, with over 10K cycles guaranteed, for repeated updating.

- Physical connection download capability.

- JTAG test capability.

- Imagination what you bring to the party.

### Conclusion

With today's programmable logic devices and enabling technologies such as Internet Reconfigurable logic, the possibilities for unique new Internet appliances are limited only by your imagination. Now you can create universal products that allow you to continually implement new creative ideas, adding features and complete new functions, at your customer's location. **£**:

With today's programmable logic devices and enabling technologies such as Internet Reconfigurable logic, the possibilities for unique new Internet appliances are limited only by your imagination.

### **PERSPECTIVE – EDA SOFTWARE**

## FPGA SYNTHESIS

Where We've Been, Where We're Going

by Tom Hill, Silicon Vendor Relations Manager, Exemplar Logic, tom.hill@exemplar.com Exemplar Logic and Xilinx pioneered FPGA synthesis and have been working together for over a decade to advance and improve methodologies.

SIC synthesis experienced rapid growth in the EDA industry during the early to mid-'90s. However, it was the programmable logic industry, that pioneered chip design using logic synthesis. Pre-dating the introduction of the first commercial ASIC synthesis tools by ten years, PALASM and ABEL were being used to synthesize PAL devices. By the mid-'80s most board designs included a programmable logic device.

### **Our History**

Xilinx, founded in 1984, had a novel idea for a new ASIC device called a field programmable gate array (FPGA). Their architecture differed significantly from the PALs in two ways. First, it employed SRAM technology to achieve reprogrammability, which pushed gate counts far beyond PALs. Second, it offered multiple logic levels on a single device, making it more versatile and more similar to gate arrays than the two-level logic structures of PALs. This second reason spawned a relationship between Exemplar Logic and Xilinx in 1987 that would profoundly change both companies.

In 1985, Ewald Detjens, the founder of Exemplar Logic, was participating in a UC Berkley research project developing algorithms for multiple logic level, interactive synthesis (MIS). Several classmates, wishing to apply these concepts to gate arrays, went on to form the origins of one of today's largest EDA

Ewald, a person preferring the road less traveled, was looking for something different when he discovered Xilinx. companies. Ewald, a person preferring the road less traveled, was looking for something different when he discovered Xilinx.

In 1987 Xilinx introduced its first automated design environment called PPR. Prior to PPR, designers placed and routed their devices by hand using a system called XACT. PPR liberated them from this painstaking process by accepting netlists of cells and automatically performing place and route. For the first time, Xilinx devices could be designed using 3<sup>rd</sup> party design entry tools and schematic capture was quickly introduced into their design flow. While broadening their appeal to gate array designers currently using schematic capture, Xilinx was failing to effectively reach the market it really wanted: the person already using programmable logic, the PAL designer using PALASM and logic synthesis.

Working closely with some of the original software developers at Xilinx, Exemplar Logic introduced its first two products in 1988. Developed exclusively for Xilinx to target PAL designers, these products were called "PDS2XNF" and "XNFOPT." PDS2XNF converted PALASM files to XNF netlists of simple primitive gates and XNFOPT incorporated the MIS synthesis technology developed at UC Berkley, along with a new invention called LUT mapping, to efficiently optimize PALASM files directly into Xilinx Configurable Logic Blocks (CLBs). Exemplar Logic gave PAL designers easy access to Xilinx technology through logic synthesis and forever changed the face of the programmable logic industry.

From these humble beginnings PLD synthesis has grown to a \$50 million a year industry and provides the chief method for designing Xilinx FPGAs. While the tools and devices have grown in sophistication, the design methodology has remained relatively consistent. Today, a single designer can complete most designs using a non-interactive, top-down synthesis approach and "on-board" verification. But will this meet the needs of tomorrow's FPGA designer? The answer is "no." Today's FPGA design methodology needs to evolve to avoid the productivity gap now being experienced by the gate array and standard cell communities where silicon densities have outpaced the designers' ability to utilize them. The Virtex family represents a major advancement in programmable logic technology providing up to one million system gates of logic.

### **Our Future**

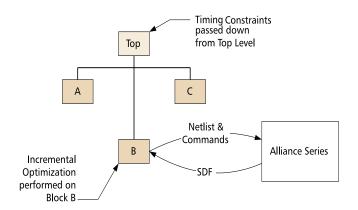

The Virtex family represents a major advancement in programmable logic technology providing up to one million system gates of logic. With this dramatic increase in gate counts, the advantages of preserving design hierarchy are too great to ignore. Initial place and route can be performed early in the design process providing valuable device utilization and performance information while changes, made during final debug, can be limited to a local sub-block, maintaining an efficient design iteration cycle. FPGA synthesis and implementation must become interactive and iterative on a block by block basis to continue to provide an efficient design methodology for FPGAs.

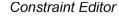

Leonardo Spectrum has been designed, not to hide design hierarchy, but rather to exploit its many advantages. A design hierarchy browser is an integral part of the user interface allowing you to easily access, manipulate, constrain, and swap hierarchical blocks. Incremental design is fully supported at the functional level allowing modules to be corrected at the RTL level, re-synthesized, and re-optimized while preserving all netlist information in the surrounding blocks. Incremental design is also supported at the synthesis level allowing constraints to be "tightened" on sub-blocks and re-optimized to correct timing or area problems discovered during place and route. Block-level design will provide the key to efficient interaction between the synthesis and place and route environments.

### Conclusion

Exemplar Logic and Xilinx pioneered FPGA synthesis and have been working together for over a decade to advance and improve methodologies. Together we are committed to developing new technologies, including improved interactive block-based FPGA design, making programmable logic design the industry's premier design methodology. **£**

Input Constraint

Infinite Drive

O Input Drive

Max Input Load:

Max Input Fanout:

Max Transition:

Rise:

Fall

Pin Location

Insert Buffers

Arrival Time

Input Ports:

INTERFACE

-⊡ load

- I reset

· 🗉 read

- 🗊 write

⊕ ⊕ I1 (priority\_encoder

⊕ ⊕ 15 (divide\_by\_n\_5)

Delete Constraints

⊕ - ⊕ 13 (thuf - 8)

⊕ -⊕ 14 (lfsr\_8)

- 🗊 clk

±-⊡ seed[24:0]

Hierarchy Browser

#### **Optimization Interface**

### **NEW TECHNOLOGY – SOFTWARE**

# FPGA Technology Drives Design Software

By looking at the changing use of FPGAs over time, we can understand the demands for a new generation of FPGA design software.

by Steve Bailey, HDL Solutions Manager, VeriBest Inc., sbailey@veribest.com

ver the last 15 years, Xilinx and the FPGA industry have evolved from providing FPGAs with densities of 100s of gates to devices with over one million system gates. Not only have system designs been adapted to exploit the capabilities of today's FPGAs in contexts not possible 15 years ago, designers have found the need to adopt new design methods and design software solutions that did not exist 15 years ago.

### 2500000-Gates 2000000 1500000 1000000 500000 0 966 998 666 984 986 988 066 992 994 997

### Soaring FPGA Device Complexity

Figure 1

### FPGA Usage Then and Now

Fifteen years ago, FPGAs were designed into systems primarily to reduce system component costs by consolidating boardlevel logic into fewer devices. A few hundred logic gates were replaced by a single FPGA that implemented the same functionality. Because the role of an FPGA was the consolidation of board-level logic into fewer components, FPGAs were designed by the board engineer.

The complexity of today's FPGAs, as shown in Figure 1, allows system architects to replace a broad range of ASICs with

FPGAs and further consolidate and integrate the system logic into fewer and fewer components. FPGAs provide you with unprecedented flexibility at attractive costs. The advantage of no non-recurring engineering (NRE) costs, easy design modification, and in-system re-programmability make FPGAs a very attractive alternatives to ASICs. In fact, Ron Collett<sup>1</sup> reports that the number of boards with at least one ASIC has declined to 22% from 45% since 1994. Clearly, FPGAs are replacing more ASICs with each new technology update. As FPGA design complexity increases and more ASICs are replaced by FPGAs, more and more FPGA design is performed by the traditional chip design teams and not by the board engineer.

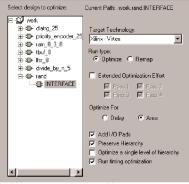

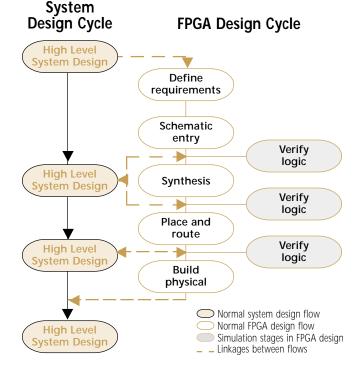

### FPGA Design Methodology Then and Now

When the board engineer was using FPGAs primarily to integrate and consolidate 100s of gates of board-level logic, he used his time-tested board design methodology anchored by schematic capture as shown in Figure 2. It was easy and straight forward to insert a new level of hierarchy into a schematic for the FPGA and push the portion of the board schematic, that was being consolidated into the FPGA, down into the new hierarchical block. The engineer had already done

manual logic minimization and captured the design at the boolean logic and macrocell level. The only additional tool needed was a fitter (or FPGA place and route tool) to map the logic design into the FPGA with correct routing. The fitter then generated a chip programming file. Verification often consisted of prototyping.

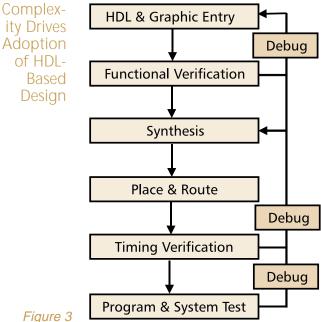

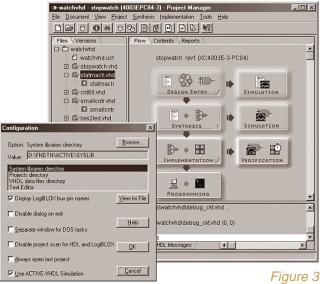

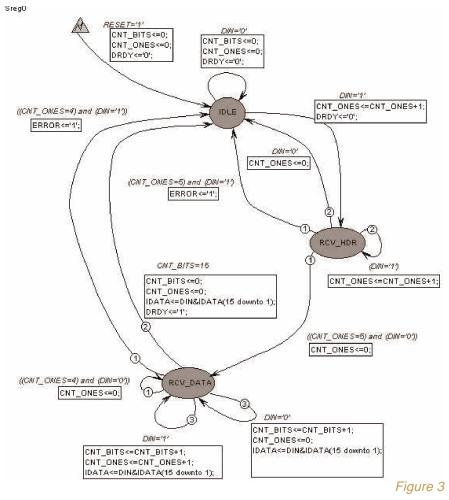

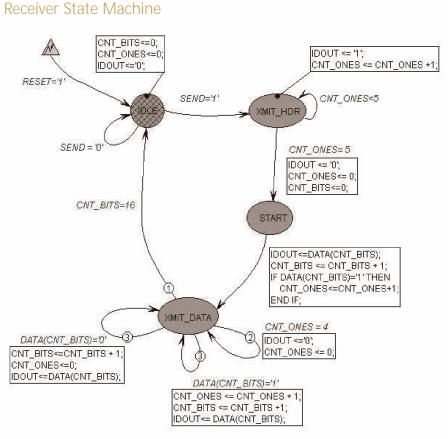

Fifteen years later, the thought of designing a million-gate FPGA using a schematic design methodology defies rational thought. Today's FPGA designers are adopting HDL-based design methods at astonishing rates. HDL-based design, as shown in Figure 3, increases your productivity by allowing you to work at higher levels of abstraction — the register-transfer level instead of the boolean logic (gate) level.

Central to HDL-based design and the increased size of FPGAs are two strategically important tools: simulation for design verification and synthesis for automatic implementation of the RTL design to the gate-level (FPGA place and route level). Bread-board prototyping falls apart as a practical design verification method due to the cost of debugging

functionality after layout. Simulation allows design problems to be discovered earlier when it is more cost-effective to fix them.

Schematics and block diagrams still have a role in FPGA design, but that role is limited to manual implementation of tightly constrained functional blocks or to help manage complexity by graphically partitioning the design into smaller blocks.

### FPGA Design Software Then and Now

Now that FPGA design is transitioning from the board engineer to the chip engineering design team, and design methodology is transitioning from schematic to HDL, FPGA design software must evolve to meet new needs.

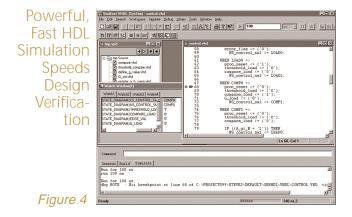

Today's FPGA designers require the power of ASIC design tools within the traditionally, tightly integrated FPGA design environment. Fast, high-capacity HDL simulation gives you the ability to functionally verify FPGA designs at the Register Transfer Level and verify the dynamic timing and functionality after implementation.

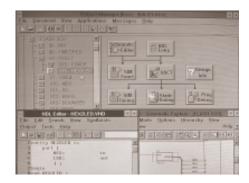

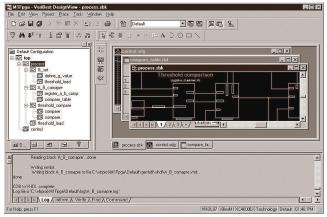

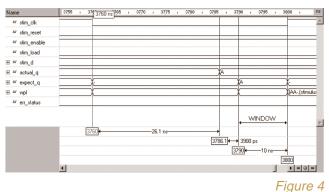

The size and functional complexity of today's FPGA designs require powerful simulators capable of handling the traditional needs of ASIC designers. VeriBest's<sup>TM</sup> HDL simulation products, shown in Figure 4, deliver technology-leading simulation speed and capacity, as well as powerful debugging capabilities, easily handling the largest of today's FPGA designs with fast verification and design debugging turnaround times.

Similarly, synthesis tools deliver productivity power by translating the design from the abstracted RTL to an architecturally optimized implementation. Synthesis tools must be able to handle the same language subset as their ASIC counterparts to facilitate re-targeting designs from ASICs to FPGAs. They must also provide ASIC-type quality of results for a variety of FPGA architectures. VeriBest's FPGA Desktop<sup>™</sup> is available with FPGA Express<sup>TM</sup> from the industry's leading ASIC synthesis provider, Synopsys<sup>®</sup>. FPGA Desktop also fully supports integration with Synplicity's<sup>®</sup> Synplify<sup>TM</sup> for Xilinx designers who find that Synplify better meets their needs.

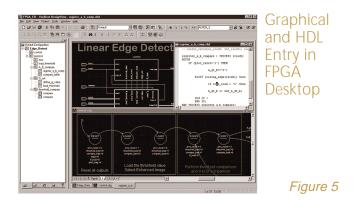

While FPGA design moves towards an HDL-dominated methodology, mixed schematic and HDL designs will be common for some time. Also, HDL editors are not always the best way to capture certain functional blocks. State diagrams are commonly employed to capture state machines. Similarly, many designers find flowcharts, truth tables, and state tables a more natural means to capture certain types of functionality. Finally, graphical design specification often results in design blocks that are more easily reused. Therefore, neither schematic-only nor HDL-only design capture environments are sufficient to support today's FPGA designs. That's why VeriBest's FPGA Desktop, shown in Figure 5, provides a rich set of design capture editors including

### **NEW TECHNOLOGY – SOFTWARE**

## REVOLUTION

schematic/block, HDL editor, state diagram, truth tables and state tables, flowcharts, and boolean equations.

Although today's FPGAs need powerful design software, you still require the productivity of the traditional FPGA design software solutions, but you need them extended to teams of designers; FPGAs still give you time-to-market advantages.

Powerful point tools address one dimension of your productivity and your ability to meet project and market schedules. Tool integration, design data, and flow management address the remaining dimensions. All of the tools within the FPGA Desktop environment are tightly integrated including third-party tools such as FPGA Express, Synplify, and the Xilinx Foundation Series place and route software. Design kits support each Xilinx device family providing additional productivity benefits. Tight integration provides you with a single environment to learn and master.

Design data and flow management are the catalysts for the productivity benefits of the integrated FPGA Desktop environment. FPGA Desktop not only understands the tools in the integrated flow, but it also manages the design data for you, whether you are working alone or as part of a team.

Data management is both user explicit, as with the automated management of the design block hierarchy and source files, and user implicit. FPGA Desktop implicitly manages the design data and flow by preparing each step in the design flow, such as creating the synthesis tool's project, configuring synthesis, and passing the synthesized netlist to the Xilinx Foundation Series software for place and route. By automating routine data management tasks, you are free to focus on the engineering specifics of executing each step in the design flow such as constraining synthesis or specifying block functionality.

Consistent with the need for a powerful design solution, FPGA Desktop passively manages the design flow by facilitating the transitions between steps in the flow. It does not constrain you by actively managing your activity within a proscribed flow.

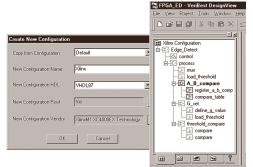

To explicitly enable teams of designers, FPGA Desktop allows the definition of multiple configurations for partitioning designs across multiple designers. You can also identify any block in the hierarchy as your design root for use as the focal point for each design step such as simulation and synthesis. Figure 6 shows the creation of a new design configuration with a focus on the portion of the design starting with the block A\_B\_Compare.

### Conclusion

As Xilinx continues to lead the industry it helped create 15 years ago by driving FPGA device size and capability forward, FPGA (and ASIC) designers are evolving to fully exploit the new generation of FPGA devices by replacing more ASICs with FPGAs. As FPGAs replace ASICs, FPGA design is moving from board engineers into chip design teams.

Both new and experienced FPGA designers find that adopting HDL design methods helps them meet their tight timeto-market requirements while designing ever larger and more complex FPGAs. The combination of these FPGA technology and design trends increase the need for FPGA design solutions that provide tools powerful enough to handle ASIC designs while also delivering the productivity of an integrated FPGA design flow. VeriBest's FPGA Desktop delivers the power and productivity that today's and tomorrow's teams require, for designing with Xilinx devices. **\$**C

Configuring Designs and Managing Hierarchy

Figure 6

<sup>1</sup> "ASICs Not What It Was," Ronald Collett, <u>Design Technology ROI</u>, **EE Times**, 1 February 1999, page 45.

## **Integrate FPGA**

by S.Dharmarajan, Senior Member Technical Staff, Cadence Design Systems, rajan@cadence.com

## System Design Using Concept<sup>®</sup> HDL

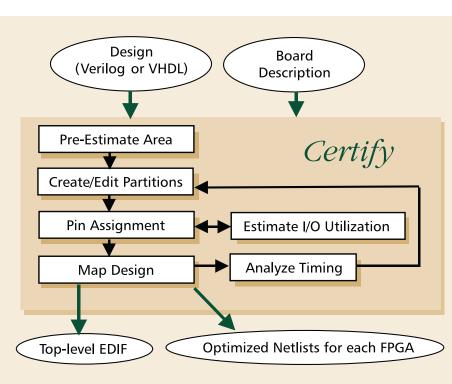

Concept HDL from Cadence Design Systems takes a big step forward in integrating System and FPGA design cycles. The latest release of Concept HDL (PE 13.5) provides many new features for FPGA design, including the capability to concurrently design the FPGA and the system that uses it.

oncept HDL has come a long way from the times when schematic entry was limited to adding gate-level primitives from FPGA vendor libraries. Now it supports top-down, mixed-level, and bottom-up FPGA design flows. From the system design perspective, Concept HDL provides a framework that seamlessly integrates FPGA and board design cycles. FPGA designers can use all Concept HDL features already available to the system designers. They can use Global Find, Global Navigate, Hierarchy Editor, and design reuse capabilities in addition to the features of earlier releases. This article focuses on how this high level of integration between the Concept HDL-based board design flow and FPGA flow can benefit you.

The Integrated Flow diagram shows the system design phases and their integration with the FPGA design phases. This article illustrates this flow using the example of an imageprocessing card based on a Xilinx FPGA for use with a generalpurpose microprocessor-based computer.

### Integrated FPGA and Board Design Flow

### **High Level System Simulation**

Concept HDL, based on the HDL-centric data model, provides the power of the HDL-based methodology with the convenience of schematic-based design. While designing an FPGA as a part of a system, you may initially simulate the system using its behavioral model to refine the expected behavior of the FPGA. This feature is especially useful for systems with many FPGAs. You can use different simulation models for the same component. You may simulate your designs using a combination of Verilog<sup>®</sup>, VHDL, smart models, and Hardware models. The HDL-centric architecture also provides for easy third-party tool integration and a high level of integration with simulators like Verilog-XL simulator, Affirma<sup>™</sup> Native Compiled Verilog<sup>™</sup> simulator, Leapfrog<sup>®</sup> VHDL simulator, and Affirma<sup>®</sup> Native Compiled VHDL simulator. You can also cross-probe the HDL code from Concept HDL — a valuable aid for debugging.

The facility to mix and match different types of simulation models provides a greater degree of design freedom. You can refine the expected behavior of the FPGA through these high level simulations and use this model to drive the FPGA design. The test vectors developed here can be used through the design cycle.

For the image processing card example, you may verify the image processing interfaces and algorithms by simulating a behavioral FPGA model with simulation models of the microprocessor, memory elements, and other system components. Thus, Concept HDL's powerful simulation capabilities allow you to refine the FPGA requirements very early in the design cycle using top-down synthesis and design of blocks

You can either directly synthesize the behavioral description of the FPGA using Synplify or design the FPGA using Concept HDL's extensive design capabilities. Concept HDL is fully integrated with Synplify from Synplicity for design synthesis so that you can specify Synplify synthesis attributes that drive and control synthesis, directly on the schematic blocks. Concept HDL automatically passes the synthesized structural netlist from Synplify to the Xilinx place and route tools.

### **NEW PRODUCTS – SOFTWARE**

Alternatively, you can create a complete design for the FPGA in Concept HDL. You can even choose to synthesize only parts of the design. This design can be flat or hierarchical, based on your preferences. Concept HDL helps you quickly create schematics from symbols or create symbols from schematics, and ensure consistent interfaces between different views. Concept HDL's design reuse features allow you to reuse older designs and save valuable design time. Concept HDL's simulation framework also allows you to simulate the FPGA block separately or simulate just some parts of it. You can easily simulate and compare the pre- and post-synthesis simulation results to verify the synthesis.

For the image processing example, you can reuse multipliers designed earlier, and synthesize only the control logic. Thus, the full integration with simulation helps you verify the functionality at any stage of the design. Concept HDL's extensive features and flexibility coupled to the integration with Synplify help you design and verify complex FPGAs with ease.

### Smooth Flow with Xilinx Place and Route Tools

Once you complete the logic design for the FPGA block, you can pass the design to the Xilinx place and route tools by just clicking a few buttons. You can also directly invoke the Xilinx Design Manager from the Cadence Programmable IC flow.

After your FPGA design is complete, using the Xilinx Alliance Series software, you can do post-route simulations using the post-route HDL files and timing data. SDF back annotation and simulation features let you compare simulation results among the behavioral model, logic-level FPGA design, and post-route FPGA design. The Concept HDL framework allows you to use the same test vectors for different views of the design (pre-route, post-route) making the comparison easier. Thus you can verify that the FPGA meets design requirements after including all physical delays.

Concept HDL's framework allows you to verify the correctness of your designs at various levels of abstraction, at different stages of your design cycle, with minimal effort.

### Easy Transfer of Data Between FPGA and PCB Tools

After your FPGA design is complete, you can automatically create a view for Allegro<sup>®</sup>, Cadence's benchmark PCB design tool. The normally tedious process, to ensure correct integration for system-level simulation and PCB design, is fully automatic, saving valuable design effort. This ensures that it is very easy to incorporate engineering changes. It is also possible to specify properties and constraints to guide the PCB tool on the FPGA design itself. The painless and reliable transfer of FPGA design information to the PCB design solution is a key feature of the Concept HDL design flow.

### Managing Signal Integrity Problems with Your FPGA

After the PCB design is complete, you can generate board-level SDF data for system-level simulation to ensure timing correctness. Full integration with SPECCTRAQuest<sup>™</sup> provides easy access to powerful high-speed system design and verification features without spending time and effort in translations. You can verify signal integrity of all signals interfacing with the FPGA before you commit to manufacturing. This is very useful for the new high-speed FPGAs from Xilinx. SPECCTRAQuest also provides you with power plane modeling and EMC analysis features critical for high-speed designs.

All this can be done without any database translations or going out of the Cadence Board Design Environment. This ensures that your design intent is captured and carried from the beginning to the end of the design cycle. This integration with Cadence's PCB design solution makes design of high speed systems more reliable.

### Conclusion

Concept HDL's powerful features for concurrent system and FPGA design, along with seamless integration with Cadence's PCB design solution, provides you with advanced capabilities to reliably design and verify large and complex system designs using FPGAs. It also allows for better and smoother communication between the system design and FPGA design. Using Concept HDL gives you the flexibility and power to effectively utilize the capacity of the latest Xilinx FPGAs without worrying about the CAD tools.

In the future, Cadence's Concept HDL will also provide features for concurrent design, generic data management, and other advanced features for system design. A tight integration with Cadence's new Integrated Native Complied Architecture for logic simulation will greatly speed up mixed language simulation.

For more details about the features of Concept HDL and other Cadence products, please visit the Cadence website at www.cadence.com or contact your local Cadence AE. §.

*Concept HDL ... provides you with advanced capabilities to reliably design and verify large and complex system designs using FPGAs.*

### **PERSPECTIVE – EDA TOOLS**

## VeriBest's Vision of the Future

VeriBest, Inc., a Xilinx Alliance partner, remembers the early beginnings of EDA tools for Xilinx design, and provides a view of the future.

emember the XC2000? I was a programmer in Huntsville, Alabama looking at designing an EDA environment for efficiently developing XC2000 and XC3000 designs. That was about ten years ago and the terms "Graphical User Interface" and "Design on NT" were unheard of in the design community. We've come a long way from the days of DOS command lines to the new vision of DesignView<sup>™</sup> — VeriBest's hierarchical development environment that supports the top-down, middle-out, and bottom-up design methodologies necessary for the future of IP design reuse.

### From Command Lines to Tri-Pane Design Desktops

Over the years, graphical interface design has become a key issue. You want to spend time on design, not memorizing command line sequences. Today, this environment is known as DesignView. Imagine a front-end design environment using multiple block views and multiple configurations allowing you to express "what if" structures in any combination of formats while simultaneously targeting multiple Xilinx families. Couple this ultimate expression of a design with seamless stimulus generation, LogiBLOX generation, integration with HDL simulators, synthesis tools, and Xilinx design tools. What you get is the power you need to have your designs meet schedule demands with the flexibility to explore your architectural alternatives; in essence, DesignView dramatically increases your productivity.

Providing much more than the flow managers of the past, DesignView allows you to *design the way you think* and view the design from the level most comfortable for you.

### DesignView Work Surface

Figure 1

### **DesignView Work Surface**

Let's look at DesignView's tri-pane work surface. The three work surface areas are:

- The Project Workspace area.

- The Design Editing area.

- The Output communication area.

The Project Workspace area contains five project tabs. These tabs allow you to access the:

- 1) Design hierarchy.

- 2) Design simulation environment (including associating and storing multiple stimuli for each hierarchical block).

- 3) Xilinx Place and Route files.

- 4) Project file manager.

- 5) Infoviewer (including links to the Web and Help files for VeriBest and Xilinx design tools).

### **PERSPECTIVE – EDA TOOLS**

The Design Editing area is the workspace area for all the design editors. Your design may consist of schematics, graphical high-level designs (incorporating state diagrams and flowcharts), and HDL (hardware description language) designs in Verilog and VHDL. A workbook mode is available, allowing you to instantly access your design files from a tabbed workbook.

The Output Communications area provides reports on tool operations, such as design verification, project searches, and HDL compilations.

The implementation of this tri-pane window environment makes DesignView unique.

### From Design Flows to Design Centric

Over the Xilinx 15 year history we have witnessed dramatic changes in design processes. The traditional top-down design flow now uses bottom-up flows that permit bottom-up verification. Middle-out flows permit synthesis and verification of single elements.

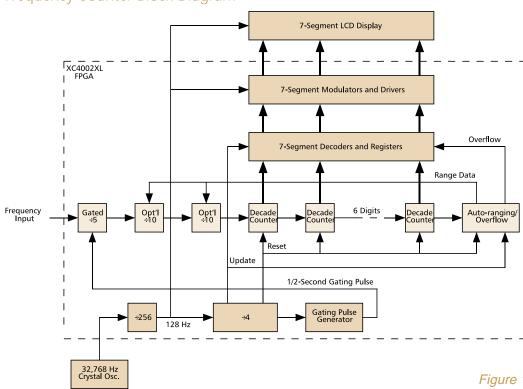

The primary failure of traditional design-flow-oriented EDA tools has been the limitations imposed on you. DesignView avoids this classic mistake by allowing all design process variants. In fact, DesignView is the only EDA tool that allows you to mix multiple design processes to complete a single design.