THE AUTHORITATIVE JOURNAL FOR PROGRAMMABLE LOGIC USERS

Celiournal

### Bright Ideas for Better Designs

### ARTICLES

Capturing Data from Gigasample Analog-to-Digital Converters

Designing for Power Budgets and Effective Thermal Management

Leveraging Programmability in Electronic System-Level Designs

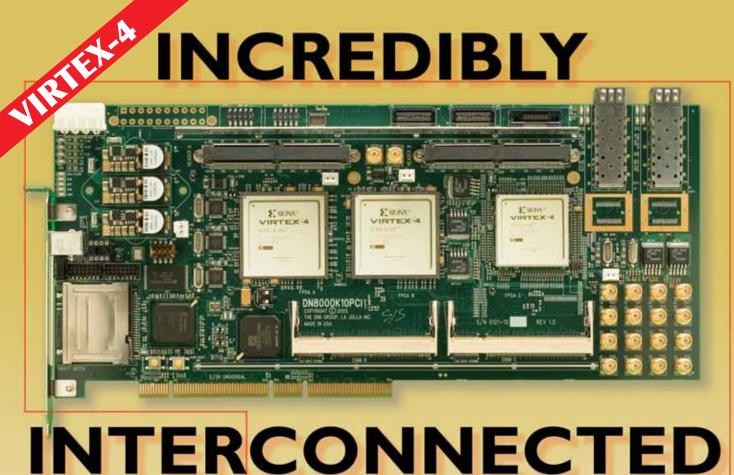

Implementing High-Performance Memory Interfaces with Virtex-4 FPGAs

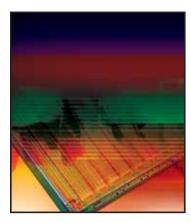

### REFERENCE

Xilinx Alliance Program Yellow Pages

## Support Across The Board.

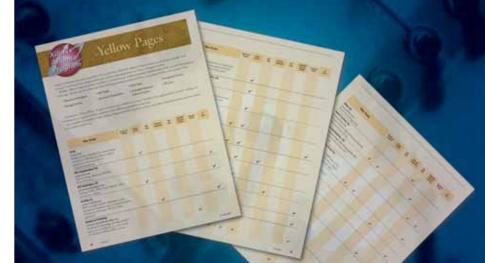

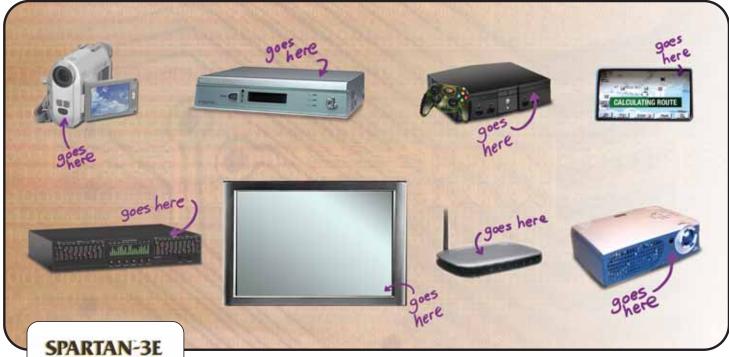

### Jump Start Your Designs with Mini-Module Development Platforms

### Mini-Module Features

- Small footprint (30 mm x 65.5 mm)

- Complete system-on-module solution with SRAM, Flash, Ethernet port and configuration memory

- Supports MicroBlaze™ or PowerPC® processors

- Based on the Virtex<sup>™</sup>-4 FX12 and 400K Gate Spartan<sup>™</sup>-3 FPGAs

- 76 User I/O

### **Baseboard Features**

- Supports mini-module family

- Module socket allows easy connection

- Provides 3.3 V, 2.5 V and 1.2 V

- USB and RS232 ports

- 2 x 16 character LCD

### Upcoming SpeedWay Design Workshops

- Developing with MicroBlaze

- Developing with PowerPC

- Xilinx Embedded Software Development

- Embedded Networking with Xilinx FPGAs

The Xilinx® Spartan<sup>™</sup>-3 and Virtex<sup>™</sup>-4 FX 12 Mini-Modules are off-the-shelf, fully configurable, complete system-on-module (SOM) embedded solutions capable of supporting MicroBlaze<sup>™</sup> or PowerPC® embedded processors from Xilinx.

Offered as stand-alone modules and as development kits with companion baseboards, power supplies, software and reference designs, these modules can be easily integrated into custom applications and can facilitate design migration.

Gain hands-on experience with these development kits and other Xilinx tools by participating in an Avnet SpeedWay Design Workshop™ this spring.

Learn more about these mini-modules and upcoming SpeedWay Design Workshops at:

www.em.avnet.com/spartan3mini www.em.avnet.com/virtex4mini www.em.avnet.com/speedway

Avnet Green Initiative

Enabling success from the center of technology™

1 800 332 8638 em.avnet.com

| EDITOR IN CHIEF   | Carlis Collins<br>carlis.collins@xilinx.com<br>408-879-4519 |

|-------------------|-------------------------------------------------------------|

| EXECUTIVE EDITOR  | Forrest Couch<br>forrest.couch@xilinx.com<br>408-879-5270   |

| MANAGING EDITOR   | Charmaine Cooper Hussain                                    |

| ONLINE EDITOR     | Tom Pyles<br>tom.pyles@xilinx.com<br>720-652-3883           |

| ART DIRECTOR      | Scott Blair                                                 |

| ADVERTISING SALES | Dan Teie                                                    |

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 Phone: 408-559-7778 FAX: 408-879-4780 www.xilinx.com/xcell/

© 2006 Xilinx, Inc. All rights reserved. XILINX, the Xilinx Logo, and other designated brands included herein are trademarks of Xilinx, Inc. PowerPC is a trademark of BM, Inc. All other trademarks are the property of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xlinx makes no warranties, express, implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against Xilinx for any loss, damage, or expense caused thereby.

## What's New?

New devices, new software, new services, and new publications to make it all easy to understand.

Our reader surveys tell us that the *Xcell Journal* is the primary source of programmable logic information for most of our customers. Your responses are overwhelmingly positive, and most of you tell us that you want more of the same; more articles, more information, more often. In response, we are launching a new series of publications that focus on the topics in which you are most interested.

We have three new magazines that will initially be produced every six months:

- *Embedded Magazine*, focusing on the use of embedded processors in Xilinx® programmable logic devices. (You'll discover simple and efficient methods of implementing highly optimized application-specific processor platforms more quickly on our devices.)

- *DSP Magazine*, focusing on the high-performance capabilities of our FPGA-based reconfigurable DSPs. (You'll find that you can create extremely high-performance DSP designs with relative ease.)

• *I/O Magazine*, focusing on the wide range of serial and parallel connectivity options available in Xilinx devices. (You'll see that your choices are almost unlimited.)

These magazines will help you explore topics that interest you the most and not waste your time with irrelevant details.

In addition to our new magazines, we've also created Solution Guides, designed to provide useful information on a wide range of hot topics such as Broadcast Engineering, Power Management, and Signal Integrity. As new industry challenges emerge, these Solution Guides will help you find answers quickly.

Until we assess the demand, these new publications are primarily available as PDF downloads (of individual articles and of whole publications). If we find sufficient demand, we plan to offer subscriptions to printed versions of these publications as well.

Please visit our publications website at www.xilinx.com/xcell.

If you find these new publications of value to you, send me a note and tell me what you think. For example, are PDF formats sufficient, or do you prefer printed copies mailed to you, like the *Xcell Journal*? Would you prefer to read them online in HTML format?

Thanks again for your feedback; it helps us serve you better.

mat Couch

Forrest Couch Executive Editor

### FIRST QUARTER 2006, ISSUE 56

## Xcelljournal

### ARTICLES

| Capturing Data from Gigasample Analog-to-Digital Converters                   | 5  |

|-------------------------------------------------------------------------------|----|

| Packet Subsystem on a Chip                                                    | 10 |

| Designing Reconfigurable Computing Solutions                                  | 15 |

| Integrating Security Services into Network Equipment                          | 19 |

| Designing for Power Budgets and Effective Thermal Management                  | 24 |

| Leveraging Programmability in Electronic System-Level Designs                 | 29 |

| Successful DDR2 Design                                                        | 32 |

| Implementing High-Performance<br>Memory Interfaces with Virtex-4 FPGAs        | 40 |

| FPGA-Based Solutions for Storage-Area Networks                                | 45 |

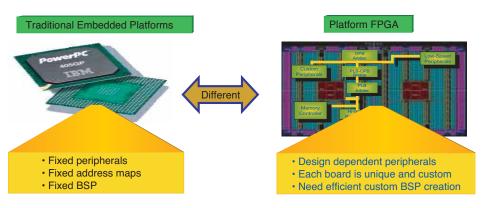

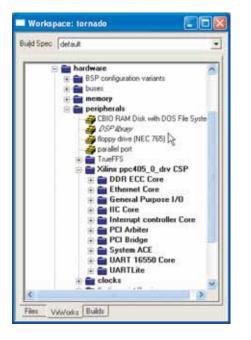

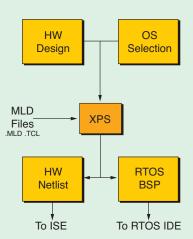

| Generating Efficient Board Support Packages                                   | 48 |

| Optimizing Embedded Systems for<br>Broadband 10 Gigabit Ethernet Connectivity | 53 |

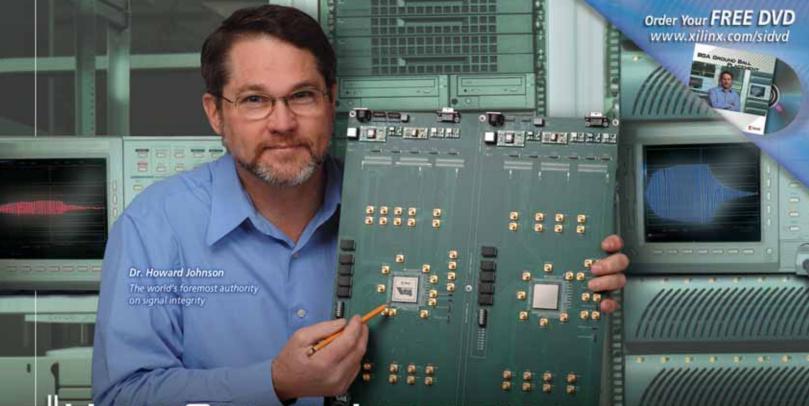

| Board Design Panacea                                                          | 59 |

| Operating a NAND Flash Device Through an FPGA                                 | 62 |

| Unveiling Nova                                                                | 65 |

| High Definition, Low Bandwidth                                                | 70 |

###

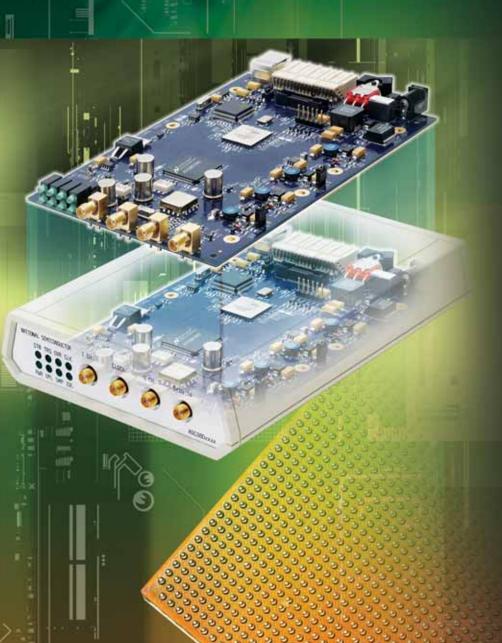

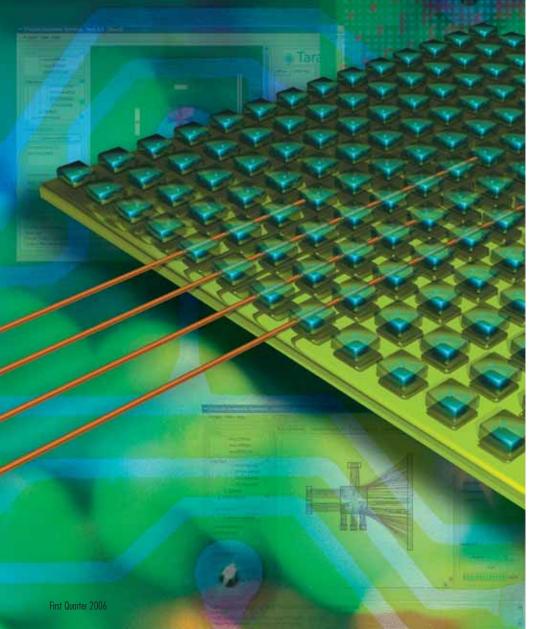

## Capturing Data from Gigasample Analog-to-Digital Converters

Interfacing National Semiconductor's ADC08D1500 to the Virtex-4 FPGA allows quick-start customer application development.

by Ian King Application Engineer National Semiconductor ian.king@nsc.com

Data conversion within the test and measurement domain and communications industry is moving into the gigasamples per second (GSPS) range. Developing a system capable of processing data at these speeds requires diverse engineering disciplines from the initial system concept through to board design, FPGA logic design, signal processing, and application software.

National Semiconductor has developed a leading-edge analog-to-digital (A/D) converter that can deliver as many as three billion samples per second to an 8-bit resolution. One of the main system design questions from customers regarding this product is how data can be reliably captured and processed at this speed. Therefore, National's applications team designed a development platform to provide a solution to this query and demonstrate a reliable data-capture method. This allows the design focus to shift away from the high-speed front end so that developers can focus on their intended application.

The platform also demonstrates that high clock speeds can be reached while maintaining low power dissipation sufficient for the entire system to be housed in a small enclosure, as would be required for a commercial or industrial system. In this article, I'll explain the techniques and analysis involved in achieving this goal.

5

### **Power Considerations**

When selecting an FPGA for data capture that can achieve low power levels and performance, a 90 nm device is the first choice. In applications where data is captured in bursts (such as oscilloscopes and radar), the static power of the FPGA device becomes an important factor. This is because the high-speed data transfer between devices takes place over a very short time period, so the capture logic will be static while the application consumes the data.

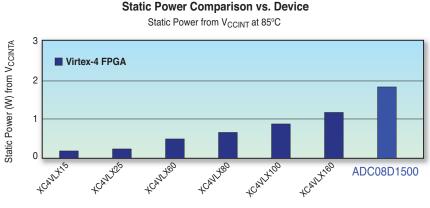

Figure 1 shows a comparison of Xilinx® Virtex<sup>TM</sup>-4 FPGA static power figures over device density. This indicates that the static power is significantly less than the power consumed by the National Semiconductor ADC08D1500 A/D converter, which is typically 1.8W when running from a 1.5 GHz sample clock. Therefore, for systems processing the captured data in bursts, the ADC can be the main source of heat and power dissipation. Having an ADC with low power figures is a key parameter in the design of products, especially those that are required to be small and portable. The design of this development platform confirms that these qualities are achieved by interfacing the ADC08D1500 to the Virtex-4 device.

### **Data Transmission**

The next consideration for systems using the ADC08D1500 and Virtex-4 FPGA is the signaling between these devices. There are two key issues when handling two channels (each providing data at a rate of 1.5 billion  $(1.5 \times 10^9)$  conversions per second):

- Signal integrity between the ADC and FPGA

- The rate of data transfer for each clock cycle

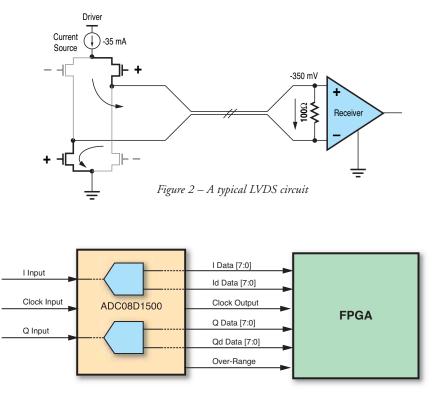

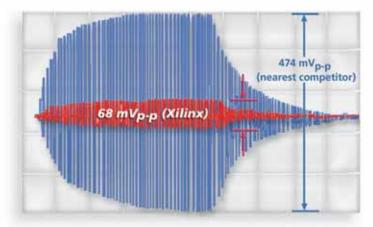

The ADC08D1500 uses low voltage differential signaling (LVDS) for each of its data outputs and clock signal. The main advantage of the LVDS signaling method is that you can achieve high data rates with a very low power budget. Two wires are used for each discrete signal that is to be carried across the circuit board, which should be designed to have a characteristic impedance of 100 Ohms (defined by the LVDS standard). These traces are differentially terminated at the receiver with a 100 Ohm resistor to match the transmission line (see Figure 2).

A signal voltage is generated across the terminating resistor by a 3.5 mA current source within the driving output buffer, which provides a 350 mV signal swing for the receiving circuit to detect. The ADC08D1500 has a total of four 8-bit

data buses, plus a clock and over-range signal that require an LVDS type connection to the FPGA (Figure 3). This adds up to a total of 34 differential pairs, all of which require 100 Ohm termination.

The Virtex-4 device offers active digitally controlled impedance (DCI) and a simple passive 100 Ohm termination onchip within the I/O buffers of the device. These on-chip termination methods eliminate the need to place passive resistors on

Devices Sorted by Equivalent Logic Element Density

Figure 1 – Comparing the Virtex-4 static power over device density with the operating power of the ADC08D1500

Figure 3 – ADC08D15000 connections to the FPGA

## The ADCO8D1500 provides a de-multiplexed data output for each of its two channels. Instead of providing a single 8-bit bus running at a data rate equal to the sampling speed, the ADC outputs two consecutive samples simultaneously on two 8-bit data buses (1:2 de-mux).

the circuit board and simplify the routing on the PCB. The DCI option consumes significantly more power than the passive option in this case, simply because of the number of discrete signal lines (68 total) that require termination. Therefore, I would advise turning on the DIFF\_TERM feature within each of the IOBs (I/O buffers) to which the ADC signals are connected.

### Data Capture

After transmitting data at high speeds using a robust signaling method, it is necessary to store this data into a memory array for post processing. The ADC08D1500 provides a de-multiplexed data output for each of its two channels. Instead of providing a single 8-bit bus running at a data rate equal to the sampling speed, the ADC outputs two consecutive samples simultaneously on two 8-bit data buses (1:2 de-mux).

If the ADC is configured as a singlechannel device and put into DES (dualedge sampling mode), then the sampling speed can be doubled (from 1.5 GSPS to 3.0 GSPS); thus, four consecutive samples are available simultaneously on each of the four buses (1:4 de-mux). This method of de-multiplexing the digital output reduces the data rate to at least half the sampling speed (1:2 de-mux), but increases the number of output data bits from 8 to 16.

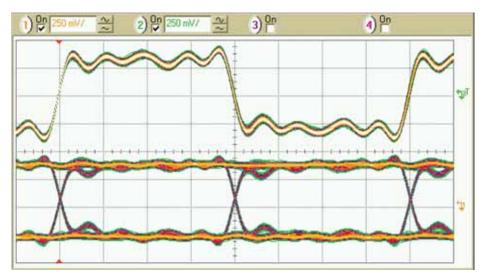

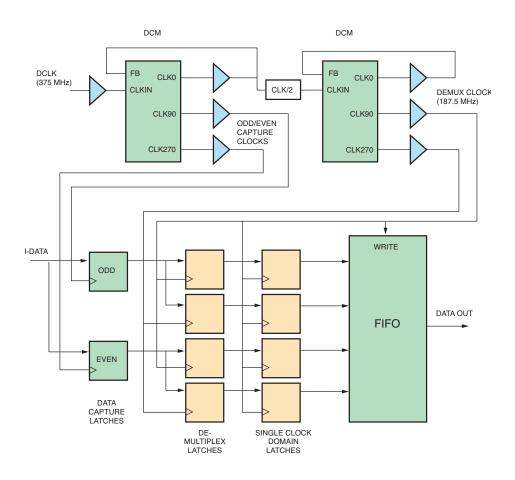

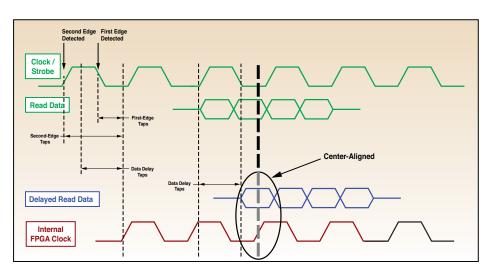

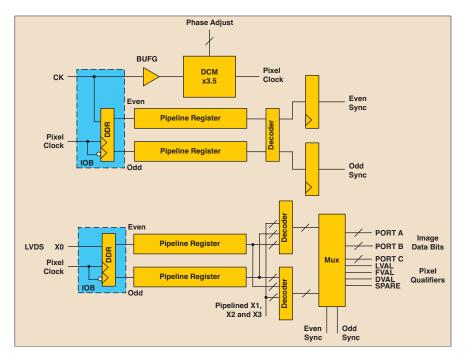

For a 1.5 GHz sample rate, the conversion data will be output synchronous to a 750 MHz clock. Even at this reduced speed, FPGA memories and latches would not be able to accept this data directly. It is therefore beneficial to make use of a DDR method, where data is presented to the outputs on the both the rising and falling edges of the clock (Figure 4).

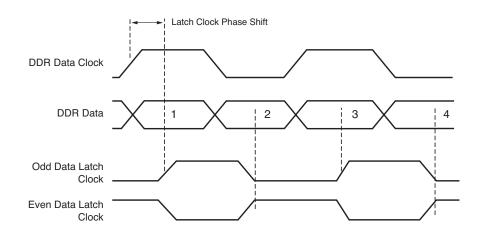

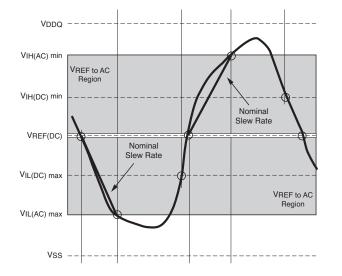

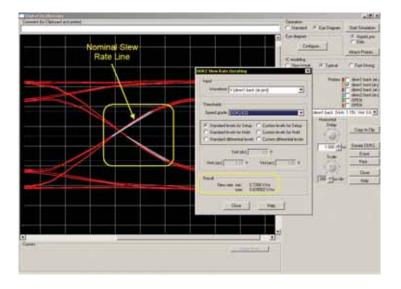

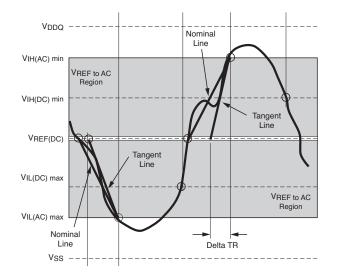

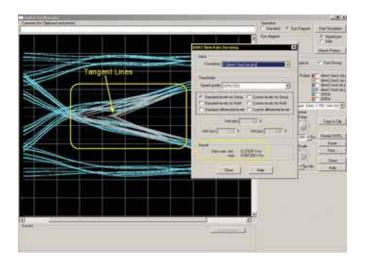

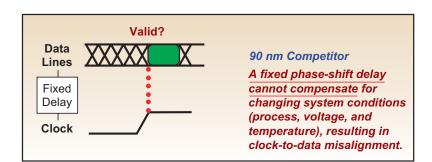

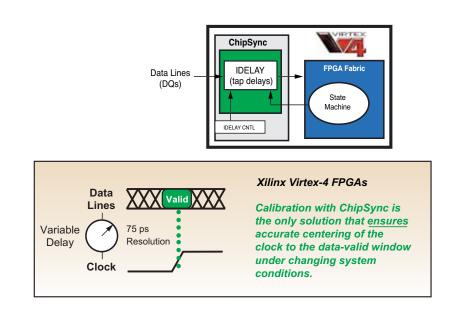

Although the data rate remains the same for DDR signaling, the clock frequency is halved again to a more manageable 375 MHz. This frequency is now in the realms of the FPGA IOB data latches. Before this data can be stored away to memory, a small pipeline constructed from a series of data latches is required. Starting with the inputs, for each data line connected to an IOB pair on the FPGA, two latches will be used to capture the incoming data. One latch is clocked on the rising edge of a phase-locked data clock, while the second latch is clocked using a signal that is 180 degrees out of phase. The relative position of these clocks should be adjusted so that the edges are aligned with the center of the data eye, taking into account the propagation delay of the signal as it enters the FPGA (Figure 5). To simplify this clocking scheme, the Virtex-4 device is equipped with DCMs that allow these clock signals to be generated internally and can be phase-locked to the incoming data clock.

After latching the incoming data using a DCM, the clock domain must be shifted

Figure 4 – Oscilloscope plot of clock (top trace) and data from the ADC in DDR mode

Figure 5 – DDR signaling with DCM-generated data-capture clocks

Figure 6 – Data-capture block diagram using two DCMs, latches, and a FIFO memory

Figure 7 – 128 bit input, 16 bit output, 4 KB deep FIFO

using an intermediate set of latches so that all of the data can be clocked into a memory array on the same clock edge. Because of the speed of the clock, there is not sufficient setup and hold time to re-clock the data; therefore the data must be de-multiplexed again to lower the data rate to 187.5 MHz. Once lowered, the data captured on the out-of-phase clock (even) can be re-captured using the in-phase clock (odd) running at the de-multiplexed rate (see Figure 6).

A second DCM is used to produce the de-mux clock. The clock input frequency is internally divided by two, which produces the 187.5 MHz clock signal. This DCM will provide an output that is phase-locked to the synchronous data clock (DCLK).

### Data Storage

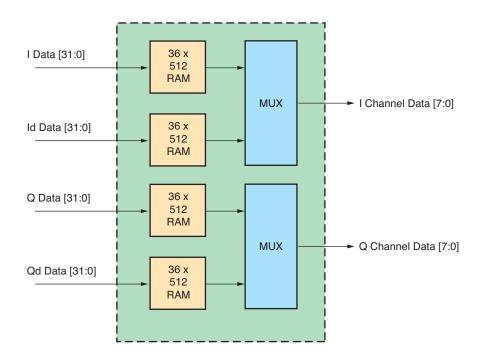

As shown in Figure 6, a single 8-bit data bus from the FPGA has been de-multiplexed by four. When all four data buses from the ADC are considered, this method produces a data word 128 bits wide running eight times slower than the sample speed for two-channel operation. The data can now be stored into a FIFO memory buffer.

Creating the custom FIFO for this application is made easy using the Xilinx LogiCORE<sup>TM</sup> FIFO Generator. Using this software wizard, you can create a FIFO with an input bus width as wide as 256 bits, having an aspect ratio (input-tooutput bus width ratio) of 8 to 1. As this design has a 128 bit input bus, the minimum output bus width is 16 bits. This works out well, allowing one 8 bit output bus to be used for I Channel data and the other for the Q channel.

Because the aspect ratio is not 1:1, the FIFO generator will create the memory design using block RAM within the FPGA. A single block RAM can be configured as 36 bits wide by 512 locations deep, so to capture the 128-bit conversion word, the design will use four block RAMs. This gives each channel a 4 KB storage depth without having to cascade FIFO blocks (Figure 7). Having 4K bytes of storage is more than sufficient data for

### The low power consumption of the two devices enables systems to operate without forced cooling in small enclosures and does not contribute to a large change in ambient temperature.

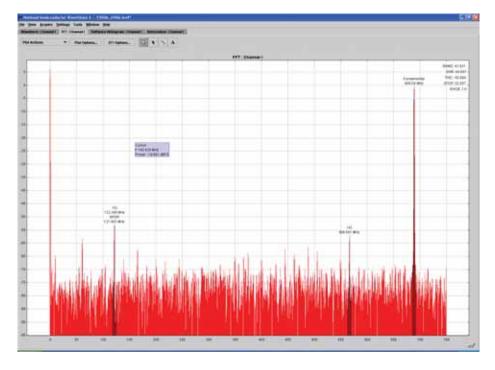

a Fast Fourier Transform (see Figure 8) to be applied to the digital conversion of the input signal and represents around 2.7  $\mu$ S of time-domain information at the 1.5 GHz conversion rate.

### Conclusion

When used for the data capture application described, about 85% of the logic fabric inside the Virtex-4 (LX15) device low switching noise and to be placed in very close proximity to a high-bandwidth, high-speed data converter without significantly downgrading the measured performance solved my FPGA design challenge.

The two-channel ADC development board discussed in this article is available to order from National Semiconductor in three speed grades: 500 MHz, 1 GHz,

Figure 8 – FFT analysis of 689 MHz input captured by ADC08D1500 and Virtex-4 FPGA

remains available for proprietary firmware development. This leaves space for additional signal processing and data analysis to be performed in hardware, reducing the burden on the software application.

The low power consumption of the two devices enables systems to operate without forced cooling in small enclosures and does not contribute to a large change in ambient temperature. The ability of the Virtex-4 FPGA to operate with and 1.5 GHz. On-board clocking is provided, so all that is required to get started is to provide an analog signal for sampling, plug in the power supply (included), and connect the USB interface to the host PC.

Single-channel device platforms are also available at 1 GHz and 1.5 GHz sample rates. For more information, visit www.national.com/xilinx and www. national.com/appinfo/adc/ghz\_adc.html.

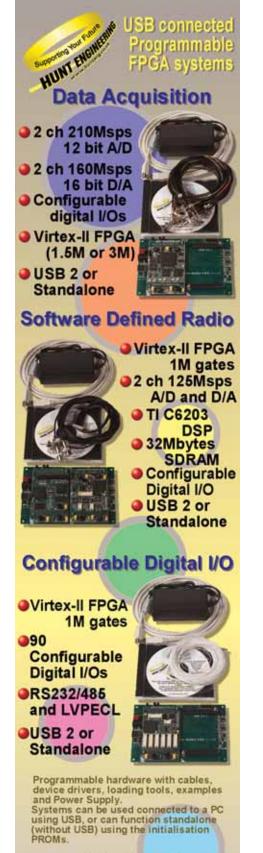

sales@hunteng.co.uk +44 (0)1278 760188

www.hunt-rtg.com

9

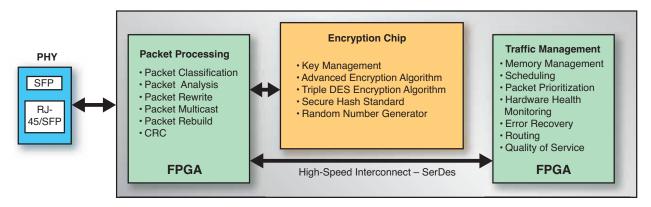

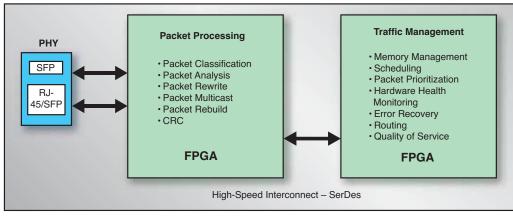

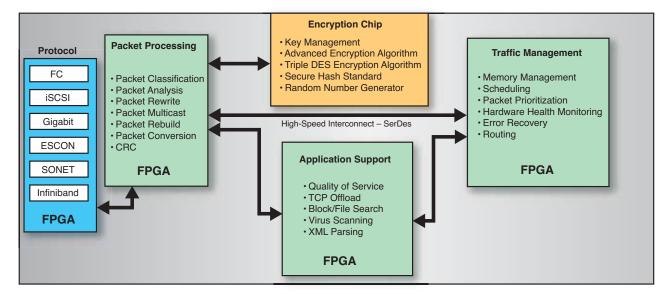

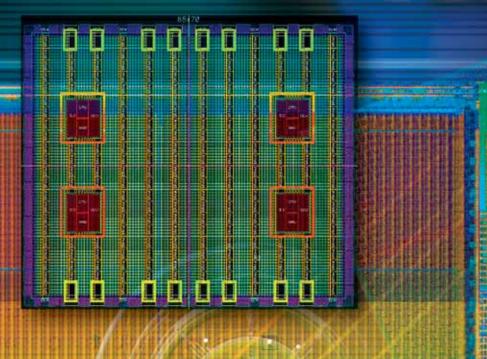

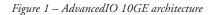

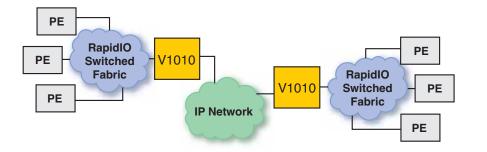

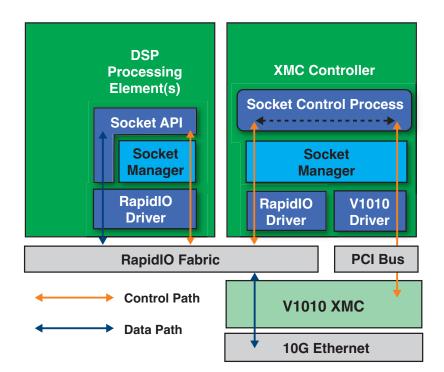

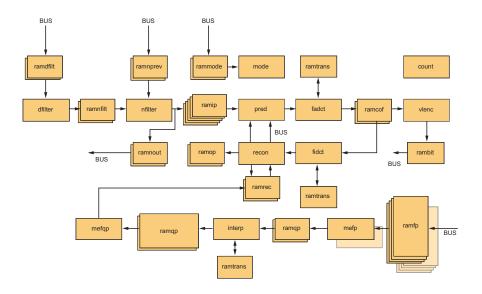

# Packet Subsystem on a Chip

Teja's packet-engine technology integrates all of the key aspects of a flexible packet processor.

by Bryon Moyer VP, Product Marketing Teja Technologies, Inc. bmoyer@teja.com

As the world gets connected, more and more systems rely on access to the network as a standard part of product configuration. Traditional circuit-based communications systems like the telephone infrastructure are gradually moving towards packet-based technology. Even technologies like Asynchronous Transfer Mode (ATM) are starting to yield to the Internet Protocol (IP) in places. All of this has dramatically increased the need for packet-processing technology.

The content being passed over this infrastructure has increased the demands on available bandwidth. Core routers target 10 Gbps; edge and access equipment work in the 1-5 Gbps range. Even some end-user equipment is starting to break the 100 Mbps range. The question is how to design systems to accommodate these speeds.

These systems implement a wide variety of network protocols. Because the protocols start out as software, it's easiest for network designers if as much of the functionality as possible can remain in software. So the further software programmability can be pushed up the speed range, the better. Although FPGAs can handle network speeds as high as 10 Gbps, RTL has typically been required for 1 Gbps and higher.

### Most traffic that goes through the system looks alike, and processors can be optimized for that kind of traffic.

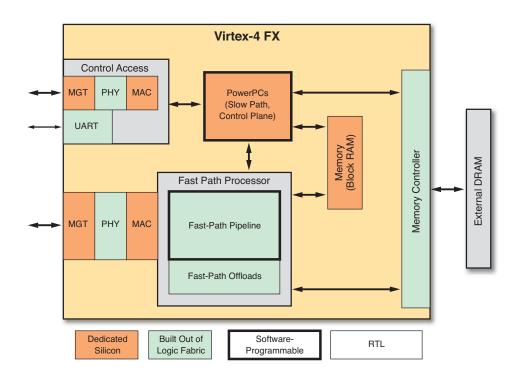

Teja Technologies specializes in packetprocessing technologies implemented in high-level software on multi-core environments. Teja has adapted its technology to Xilinx<sup>®</sup> Virtex<sup>TM</sup>-4 FPGAs, allowing highlevel software programmability of a packetprocessing engine built out of multiple MicroBlaze<sup>TM</sup> soft-processor cores. This combination of high-level packet technology – using Virtex-4 devices with on-board MACs, PHYs, PowerPC<sup>TM</sup> hard-core processors, and ample memory – provides a complete packet-processing subsystem that can process more than 1 Gbps in network traffic.

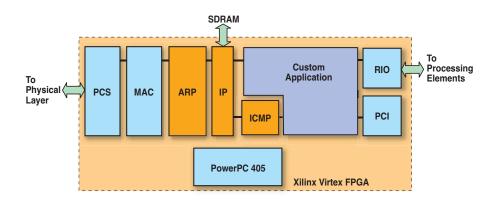

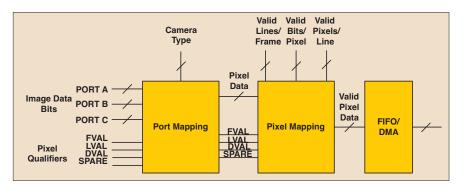

### The Typical Packet Subsystem

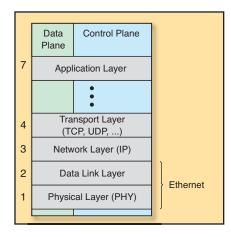

The network "stack" shown in Figure 1 is typically divided between the "control plane" and the "data plane." All of the packets are handled in the data plane; the control plane makes decisions on how the packets should be processed. The lowest layer sees every packet; higher layers will see fewer packets.

The control plane comprises a huge amount of sophisticated software. The data-plane software is simpler, but must operate at very high speed at the lowest layers because it has such a high volume of packets. Packet-processing acceleration usually focuses on layers one to three of the network stack, and sometimes layer four.

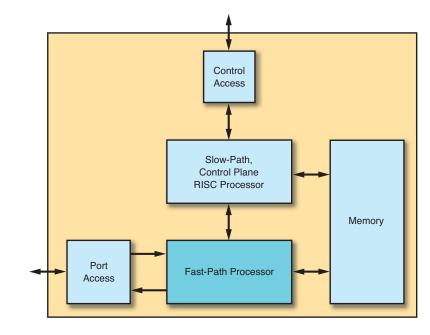

Most traffic that goes through the system looks alike, and processors can be optimized for that kind of traffic. For this reason, data-plane systems are often divided into the "fast path," which handles average traffic, and the "slow path," which handles exceptions. Although the slow path can be managed by a standard RISC processor like a PowerPC, the fast path usually uses a dedicated structure like a network processor or an ASIC. The focus of the fast path is typically IP, ATM, VLAN, and similar protocols in layers two and three. Layer four protocols like TCP and UDP are also often accelerated. Of course, to process packets, there must be a way to deliver the packets to and from the fast-path processor. Coming off an Ethernet port, the packets must first traverse the physical layer logic (layer one of the stack, often a dedicated chip) and then the MAC (part of layer two, also often its own dedicated chip).

One of the most critical elements in getting performance is the memory.

Figure 1 – The network protocol stack

Memory is required for packet storage, table storage, and for program and data storage for both the fast and slow paths. Memory latency has a dramatic impact on speed, so careful construction of the memory architecture is paramount.

Finally, there must be a way for the control plane to access the subsystem. This is important for initialization, making table changes, diagnostics, and other control functions. Such access is typically accomplished through a combination of serial connections and dedicated Ethernet connections, each requiring logic to implement.

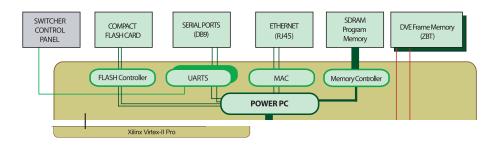

A diagram of this subsystem is shown in Figure 2; all of the pieces of this subsystem are critical to achieving the highest performance.

### The Teja Packet Pipeline

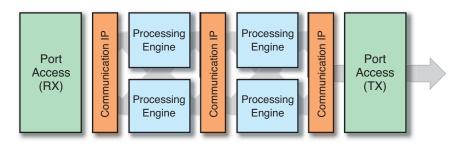

One effective way to accelerate processing is to use a multi-core pipeline. This allows you to divide the functionality into stages and add parallel elements as needed to hit performance. If you were to try to assemble such a structure manually, you would immediate-

Figure 2 – Typical packet-processing subsystem

ly encounter the kinds of challenges faced by experienced multi-core designers: how to structure communication between stages, scheduling, and shared resource access.

Teja has developed a pipeline structure by creating its own blocks that implement the

Access to the pipeline is provided by a block that takes each packet and delivers the critical parts to the pipeline. Because this block is in the critical path for every packet, it must be very fast, and has been designed by Teja for very high performance.

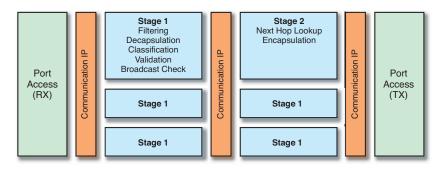

Figure 3 – Teja packet-processing pipeline

necessary functions for efficient processing and inter-communication. By taking advantage of this existing infrastructure, you can assemble pipelines easily in a scalable fashion.

The pipeline comprises processing engines connected by communication blocks and accessed through packet access blocks. Figure 3 illustrates this arrangement.

The engine consists primarily of a MicroBlaze processor and some private block RAM on the FPGA. In addition, if a stage has a particularly compute-intensive function like a checksum, or a longerlead function like an external memory read or write, an offload can be included to accelerate that function. Because the offload can be created as asynchronous if desired, the MicroBlaze processor is free to work on something else while the offload is operating.

The communication blocks manage the transition from stage to stage. As packet information moves forward, the communication block can perform load balancing or route a packet to a particular engine. Although the direction of progress is usually "forward" (left to right, as shown in Figure 3), there are times when a packet must move backwards. An example of this is with IPv4/v6 forwarding, when an IPv6 packet is tunneled on IPv4. Once the IPv4 packet is found, and it must go back for IPv6 decapsulation.

The result of this structure is that each MicroBlaze processor and offload can be working on a different packet at any given time. High performance is achieved because many in-flight packets are being handled at once.

The key to this structure is its scalability. Anytime additional performance is needed, you can add more parallel processing, or create another pipeline stage. The reverse is also true: if a given pipeline provides more performance than the target system requires, you can remove engines, making the subsystem more economical.

### The Rest of the Subsystem

What is so powerful about the combination of Teja's data-plane engine and the Virtex-4 FX devices is that most of the rest of the subsystem can be moved on-chip. Much of the external memory can now be moved into internal block RAM. Some external memory will still be required, but high-speed DRAM can be directly accessed by the Virtex-4 family, so no intervening glue is required. The chips have built-in Ethernet MACs which, combined with the available PHY IP and RocketIO<sup>TM</sup> technology, allow direct access from Ethernet ports onto the chip.

The integrated PowerPC cores (as many as two) allow you to implement the slow path and even the entire control plane on the same chip over an embedded operating system such as Linux. You can also provide

Figure 4 – Single-chip packet-processing subsystem

control access through serial and Ethernet ports using existing IP.

As a result, the entire subsystem shown in Figure 2 (with the exception of some external memory) can be implemented on a single chip, as illustrated in Figure 4.

### Flexibility: Customizing, Resizing, Upgrading

Teja's packet-processing infrastructure provides access to our company's real strength: providing data-plane applications that you can customize. We deliver applications such as packet forwarding, TCP, secure gateways, and others with source code. The reason for delivering source code is that if One of the most important aspects of software programmability is field upgrades. With a software upgrade, you can change your code – as long as you stay within the amount of code store available. As the Teja FPGA packet engine is software-programmable, you can perform software upgrades. But because it uses an FPGA, you can also upgrade the underlying hardware in the field. For example, if a software upgrade requires more code store than is available, you can make a hardware change to make more code store available, and then the software upgrade will be successful. Only an FPGA provides this flexibility.

Figure 5 – IPv4 forwarding engine

you need to customize the operation of the application, you can alter the delivered application using straight ANSI C. Even though you are using an FPGA, it is still software-programmable, and you can design using standard software methods.

An application as delivered by Teja is guaranteed to operate at a given line rate. When you modify that application, however, the performance may change. Teja's scalable infrastructure allows you to tailor the processor architecture to accommodate the performance requirements in light of changed functionality.

In a non-FPGA implementation, if you cannot meet performance, then you typically have to go to a much larger device, which will most likely be under-utilized (but cost full price). The beauty of FPGA implementation is that the pipeline can be tweaked to be just the right configuration, and only the amount of hardware required is used. The rest is available for other functions. Because a structure like this is typically designed by high-level system designers and architects, it is important that ANSI C is the primary language. At the lowest level, the hardware infrastructure, the mappings between software and hardware, and the software programs themselves are expressed in C. Teja has created an extensive set of APIs that allow both compile-time and real-time access from the software to the various hardware resources. Additional tools will simplify the task of implementing programs on the pipeline.

### **IPv4 Forwarding Provides Proof**

Teja provides IPv4 and IPv6 forwarding as a complete data-plane application. IPv4 is a relatively simple application that can illustrate the power of this packet engine. It is the workhorse application under most of the Internet today. IPv6 is gradually gaining some ground, with its promise of plenty of IP addresses for the future, but for now IPv4 still dominates. At its most basic, IPv4 comprises the following functions:

- Filtering

- Decapsulation

- Classification

- Validation

- Broadcast check

- Lookup/Next Hop calculation

- Encapsulation

Teja has implemented these in a two-stage pipeline, as shown in Figure 5. Offloads are used for the following functions:

- Checksum calculation

- Hash lookup

- Longest-prefix match

- Memory access

This arrangement provides full gigabit line-rate processing of a continuous stream of 64-byte packets, which is the most stringent Ethernet load.

### Conclusion

Teja Technologies has adapted its packetprocessing technology to the Virtex-4 FX family, creating an infrastructure of IP blocks and APIs that take advantage of Virtex-4 FX features. The high-level customizable applications that Teja offers can be implemented using software methodologies on a MicroBlaze multicore fabric while achieving speeds higher than a gigabit per second. Software programmability adds to the flexibility and ease of design already inherent in the Virtex family.

The flexibility of the high-level source code algorithms is bolstered by the fact that the underlying hardware utilization can be specifically tuned to the performance requirements of the system. And once deployed, both software and hardware upgrades are possible, dramatically extending the potential life of the system in the field.

Teja Technologies, the Virtex-4 FX family, and the MicroBlaze core provide a single-chip customizable, resizable, and upgradable packet-processing solution.

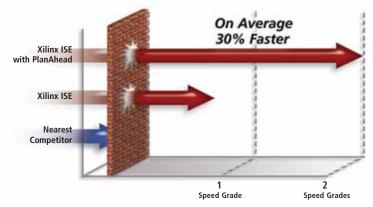

### Learn to increase Design Performance using the new PlanAhead Software Tool.

### www.xilinx.com/education

The new PlanAhead software tool from Xilinx allows you to quickly analyze, floorplan, and improve placement and timing of even the most complex designs. Use your Xilinx Training Credits or pay as you go for this in-depth, hands-on course:

### Designing with PlanAhead (2 Days)

Perfect for FPGA designers, system architects, and system engineers interested in analyzing and driving the physical implementation of their designs to maximize performance and capacity. With this comprehensive training, you will develop the necessary skills to import designs into the PlanAhead software, analyze design statistics, partition and floorplan, improve performance, run Design Rule Checks (DRC) and implement a floorplanned design, and more.

Visit *www.xilinx.com/education* for more information and registration. Or call us at 1-877-XLX-CLASS.

©2006 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

## Designing Reconfigurable Computing Solutions

The Virtex family of FPGAs is the foundation for Cray XD1 high-performance co-processing solutions.

by Geert C. Wenes, Ph.D. HPC Architect Cray, Inc. geertw@cray.com

Steve Margerm Senior Hardware Designer Cray, Inc. smargerm@cray.com

Sriram R. Chelluri Marketing Manager Xilinx, Inc. sriram.chelluri@xilinx.com

The reconfigurable computing (RC) architecture enables software logic that can be reconfigured or reprogrammed to implement specific functionalities on tunable hardware rather than on a general-purpose processor (GPP). RC can achieve ordersof-magnitude performance improvements on selected applications. An RC solution in a high-performance computing environment should include tight coupling and a transparent interface to a generalpurpose processor and its auxiliary resources (storage, I/O, networking).

Because FPGAs are tunable, high-density logic cores that provide high-performance and low-latency features, they are well suited for RC solutions. In this article, we'll describe what RC is, how it fits into the Cray, Inc. XD1 high-performance architecture, and why Cray selected Xilinx as the foundation for high-performance application acceleration.

### What's Different about RC?

A GPP is primarily designed to execute sequential instructions. System designers have introduced parallelism in two different ways: off-chip, by simply clustering many GPPs and distributing the workload among these multiple processors; or on-chip, either by duplicating the independent computational units on the chip or (more recently) by doubling the cores on a processor.

In contrast, FPGAs can perform many operations in parallel. Xilinx<sup>®</sup> FPGAs with embedded PowerPC<sup>TM</sup> processors can perform fixed-point arithmetic and embedded functions, offloading the main processor to other tasks. Furthermore, standard HDLs

for logic devices (such as VHDL and Verilog) have at their core the notions of parallel execution of statements and eventdriven simulation.

FPGAs, on the other hand, do not suffer from serial execution model restrictions found in standard languages such as C for generic CPUs. FPGAs are increasingly used to provide application performance. Industries such as manufacturing, government, research, media, and biosciences are deploying FPGAs as hardware application accelerators that can provide orders-of-magnitude (10 to 100x) performance improvements on selected applications over generic microprocessors. The advantages of such an RC solution are:

- Dramatic overall system performance gains at only incremental co-processing board costs

- The ability to reprogram, utilizing a consistent API to the hardware

- Easily upgrade or retarget hardware

### **Cray XD1 Architecture**

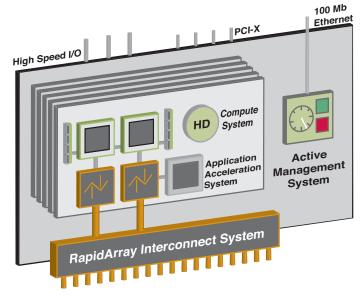

The Cray XD1 high-performance computer is based on the directly connected processor (DCP) architecture. The DCP architecture views the system as a pool of processing, logic, and memory resources interconnected by a high-bandwidth low-latency network. This innovative new computer unifies as many as hundreds of processors into a single, resilient computer. The Cray XD1 system combines both on-chip and off-chip parallelism.

The Cray XD1 architecture includes three key subsystems:

- Compute environment. The Cray XD1 compute subsystem comprises singleor dual-core AMD Opteron 64-bit processors integrated on a single board and six blades constituting a chassis (Figure 1). The operating system is Linux, supporting 32- and 64-bit x86compatible software.

- Interconnect. The Cray XD1 RapidArray interconnect directly connects blades over high-speed, low-latency pathways (Figure 2). Each fully configured chassis includes two interconnect components:

- An FPGA-based RapidArray communications processor (RAP) is tightly coupled to the AMD Opteron processors and switching fabric to offload and accelerate communications functions from the Opteron processors, freeing the latter to perform core compute tasks and enabling concurrent computing and communication. The FPGA enables interconnect bandwidth on par with memory bandwidth, solving a major system performance bottleneck.

- The RapidArray embedded switching fabric is a 96 GB/s, non-blocking, crossbar switching fabric in each chassis that provides four 2 GB/s links to each node and twenty-four 2 GB/s inter-chassis links.

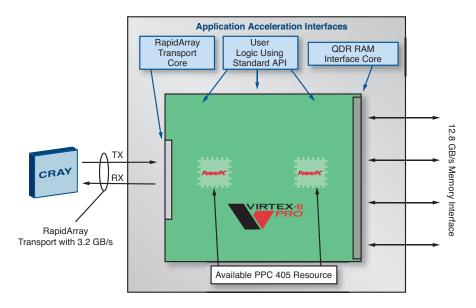

- Acceleration application modules. The application acceleration subsystem incorporates RC capabilities to deliver substantial performance increases for targeted applications (Figure 3). Each Cray XD1 chassis can be configured with six application acceleration processors (one per blade), originally developed using the Xilinx Virtex<sup>TM</sup>-II Pro device

Figure 1 – Single Cray XD1 chassis

but soon shipping with Virtex-4 FPGAs that you can program to accelerate key algorithms. The application acceleration processors are tightly integrated with Linux and the AMD Opteron processors and use standard software programming APIs, removing a major obstacle to application development.

### The FPGA as Co-Processor Model

Cray views the FPGA as a very tightly coupled application accelerator platform to speed up computations on demanding applications. The FPGAs are designed into an expansion module that connects to the high-speed, low-latency, point-to-point HyperTransport subsystem.

There are three main advantages that an FPGA has over a microprocessor:

- FPGAs have a flexible architecture. You can customize and optimize the logic and manipulate variable length data.

- FPGAs are inherently parallel devices.

- FPGAs can be reprogrammed to execute new applications without having to change the hardware.

### Xilinx Solution

Cray selected the Virtex-II Pro and Virtex-4 series of FPGAs as the foundation for its RC solutions because of their industryleading technical features and support for third-party development.

Figure 2 – Cray XD1 compute blade

Figure 3 – Xilinx-based application acceleration module

Advantages of Xilinx Virtex FPGAs include:

- Low latency and a high throughput range of 622 Mbps-10.3125 Gbps

- High-speed 500 MHz internal I/O clock

- Low power consumption

- Optional embedded hardware PowerPC processor or a software coprocessor

- Built-in scalable RAM

Cray chose the Virtex family of FPGAs because it was developed for high performance, from low- to high-density designs based on IP cores and customized modules.

### **Development Environment**

Many Xilinx and third-party tools simplify the development of co-processing solutions. Software developers can interface with software APIs provided by Cray and use a rich variety of third-party design tools to create their own applications using C and C++.

For instance, Celoxica Ltd. provides a C-based design and synthesis tool (DK Design Suite) for customers who want to use a software design flow to accelerate their applications using FPGAs integrated into the Cray XD1 supercomputer (*www.celoxica.com/products/dk/default.asp*).

As another example, the Cray XD1 system equipped with Mitrionics' Mitrion Virtual Processor and Mitrion Software Development Kit make it possible for supercomputer users to program FPGAs integrated into the Cray XD1 system on a software level, reducing the time and effort required to take advantage of FPGAbased computation (*www.mitrionics.com/ technology.shtml*).

For DSP solutions, Xilinx System Generator for DSP enables you to design DSP blocks using commercial tools like the MATLAB package from The MathWorks.

### **Applications Acceleration**

The XD1 has proven to be a successful product. For example, the Naval Research Laboratory (NRL) facility in Washington, D.C., is home to one of the largest Cray XD1 supercomputers ever installed and also employs the largest known number of application acceleration modules in the world. Equipped with 288 AMD Opteron dual-core processors and 144 Virtex-II Pro FPGAs, the 24-chassis machine will provide peak performance of 2.5 teraflops.

The use of FPGAs as application accelerators has been successfully demonstrated in many fields. For instance:

• In encryption/decryption applications, the RC5 cipher-breaking application

runs 1000x faster than on a 2.4 GHz Pentium 4, while for elliptic curve cryptography, speedups of 895 to 1300x compared to (a relatively slow) 1 GHz Pentium III are possible. Encryption algorithms like 3DES have been shown to run at more than 16 Gbps throughput from a high-level abstraction language like Mobius.

- In bioinformatics applications, the well-known Smith-Waterman code performs about 26 times faster than on the AMD Opteron, while applications in proteomics such as thinspline algorithms for comparing 2D gel contents run more than 20 times faster, reducing analysis times from days to hours.

- Complex, realistic vehicular traffic simulation codes perform 34x faster on Virtex-II Pro devices than on a 2.2 GHz Opteron, and remarkable sustained bandwidths from the FPGA to AMD processor have been observed at more than 1 GB/s, considerably higher than any PCI bandwidth.

### Conclusion

Cray's FPGA-based RC solutions are ideal for applications in industries such as manufacturing, government, research, media, and biosciences. Cray selected the Virtex-II Pro and Virtex-4 series because of their high performance, low latency, scalable memory, and an array of software tools and support.

With the Cray XD1 high-performance computer, reconfigurable computing has taken a major step forward by breaking down performance barriers at substantially lowered cost by using off-the-shelf components from Xilinx to solve difficult computational problems.

For more information about Cray RC solutions' HPC architectures, contact geertw@cray.com or visit www.cray.com/ products/xd1/index.html.

For more information about Xilinx FPGA-based co-processing solutions, contact sriramc@xilinx.com or visit www. xilinx.com/products/design\_resources/ dsp\_central/resource/coprocessing.htm.

### XILINX EVENTS AND TRADESHOWS

Xilinx participates in numerous trade shows and events throughout the year. This is a perfect opportunity to meet our silicon and software experts, ask questions, see demonstrations of new products, and hear other customer success stories.

For more information and the current schedule, visit www.xilinx.com/events/.

### Worldwide Events Schedule

### North America

**Jan. 5-8** CES Las Vegas, NV

Feb. 6-9 DesignCon West Santa Clara, CA

Feb. 21-23 IDGA SW Radio Summit Arlington, VA

April 3-6 Storage Networking World San Diego, CA

### April 4-6 ESC Silicon Valley San Jose, CA

April 4-6 ESC Silicon Valley Workshops San Jose, CA

April 5-7 CTIA Wireless Las Vegas, NV

April 24-27 NAB Las Vegas, NV

### Europe

Feb. 13-16 3GSM World Congress Barcelona, Spain

Feb. 14-16 Embedded World Nuremberg, Germany

### **XILINX**®

Phone: +1 (650) 292 4636 Fax: +1 (650) 618 2769 Email: sales@sensorynetworks.com

## **Special Offer for Xcell Readers**

Sensory Networks<sup>®</sup> Acceleration Development Kits enable software developers to quickly integrate hardware acceleration for Antivirus, Antispam, Antispyware, Content Filtering and Content Security applications.

Included in the package are two C-2000 Ultra Multi-Gigabit Security Accelerators plus all the tools and support necessary to quickly turbocharge new and existing network security applications. Package Includes:

- 2 x C-2000 ULTRA Content Security Accelerator Card

- Access to full suite of SDK development environment and tools

- Complete set of security application APIs

- Sample applications and example code

- User manuals

- Programming and integration guide

- 12 months developer support

- Membership in Sensory Networks' Partnership Program

To take advantage of this special offer, please visit:

Sensory Networks<sup>®</sup> and NodalCore<sup>®</sup> are registered trademarks of Sensory Networks Inc. CorePAKT<sup>™</sup> and Acceleration Development Kit<sup>™</sup> are trademarks of Sensory Networks Inc. Copyright © Sensory Networks Inc 2005. All Rights Reserved.

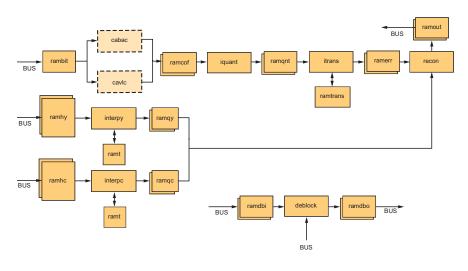

# Integrating Security Services into Network Equipment

Using Sensory Networks' NodalCore technology, Virtex-4 FPGAs can solve the design challenge of integrating high-performance security acceleration to cope with continually evolving network threats.

by Ryan Junee Product Manager Sensory Networks ryan.junee@sensorynetworks.com

Sriram R. Chelluri Vertical Marketing Manager Xilinx, Inc. *sriram.chelluri@xilinx.com*

In today's network environment, security threats are everywhere – from Web- and email-borne viruses and worms to productivity-hampering spam and spyware to malicious break-in attempts. Security functionality in network equipment is no longer "nice to have" – it is now a fundamental design requirement.

Designers of network equipment must be able to integrate applications such as antivirus, anti-spam, anti-spyware, intrusion detection and prevention, content filtering, and sometimes all of these in one box (a universal threat management or UTM appliance), without sacrificing performance throughput or detection accuracy. With today's rapidly increasing network speeds and the growing taxonomy of network threats, this is a difficult design challenge.

In this article, we'll present an FPGAbased solution to the problem and describe how to integrate security functions using an architecture that can be easily upgraded over time.

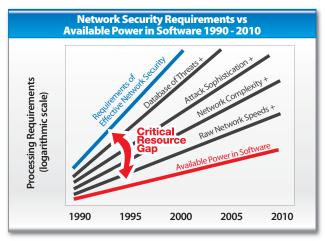

Figure 1 – Critical resource gap in traditional security appliances

### **Current Technical Challenges**

Today's security devices provide a "best effort" service but fall dramatically short of providing comprehensive protection. The growing number and sophistication of attacks and the exponential growth in raw network traffic leads to increases in both complexity and processing speed requirements in network security applications (Figure 1). This sort of processing power is simply not available in traditional security appliances built from standard PC hardware packaged into a rack-mount chassis.

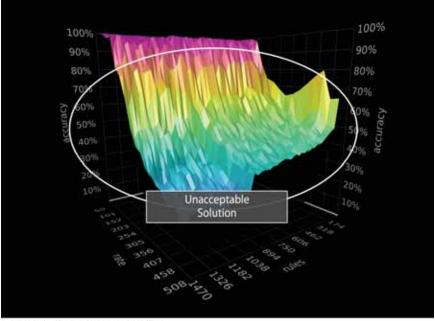

Figure 2 shows an example of the reduced accuracy in Snort (the industrystandard open-source intrusion detection system) as the number of rules (types of attacks detected) and the traffic rate are increased. Any IDS that cannot scale and maintain an accuracy rate of more than 90% is not worth implementing. Security processing has quickly become the major bot-tleneck in today's network environments, and is often dealt with by reducing the number of attack signatures that are detected or by dropping packets, leading to missed attacks and security holes in both cases.

There are two forms of data inspection for network security appliances:

• Header (or packet) processing. Processing is restricted to read and write operations on the packet header; thus the processing complexity is independent of the size of the packet. Examples include TCP flow reassembly, IP forwarding, and some Snort header rules. • Content processing. Read and write operations are applied to all of the data in the packet; in particular, the payload of the packet. Examples include pattern matching (searching packets for viruses), content decoding (MIME), and decompression/encryption (VPNs).

Today's security appliances perform these types of data inspection using either general-purpose processors,

network processing units (NPUs), or fixedfunction ASICs. These architectures all have drawbacks in performance, scalability, adaptability, and cost.

Under a general-purpose architecture, network traffic is captured using a network interface card (NIC) that connects to the host processor over a bus such as PCI. The function of reassembling data streams is handled by the operating system, while content decode and inspection operations are handled by a user-space software application. Although functionally separate, these operations all share the same CPU, memory, buses, and other system resources. The most computationally expensive operations will therefore consume most of the resources, leaving little processing time for other operations and causing critical bottlenecks.

NPU-based solutions are limited when it comes to content decode and inspection operations. Although NPUs are very good at processing packets, they break down when scanning content across multiple packets. Even multi-core NPUs designed for content processing often cannot scale to wire speed for deep packet inspection.

ASIC-based security appliances are expensive, with long lead times and high risk. They are not adaptable to changing threat environments and cannot be upgraded with new performance and features. This leads to a solution that is not future-proof.

What is needed for the modern-day dynamic environment of network security is an adaptable co-processing platform, with the ability to:

- Accelerate deep packet inspection

- Deal with large databases

- Adapt to new security threats

- Adapt to new content types

- Adapt to new security applications

10:90 mix of attack: normal traffic

Figure 2 – Snort 2.0 performance on a dual 3 GHz Xeon

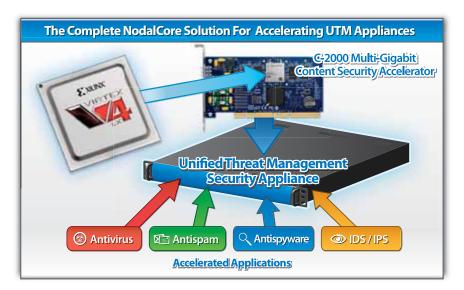

Figure 3 – Building a security appliance with the NodalCore SPU

To meet these design criteria, a security co-processor based on reconfigurable technology is required, and must meet the following guidelines to be market-viable:

- Interfaces with standard architectures (Pentium, NPU, multi-core MIPS)

- Designed for deterministic processing in the data plane (pattern matching, decoding)

- Allows in-field upgrades of functionality to adapt to new threats, new applications, and new content types

- Scalable number of parallel execution units

### The NodalCore Co-Processing Solution

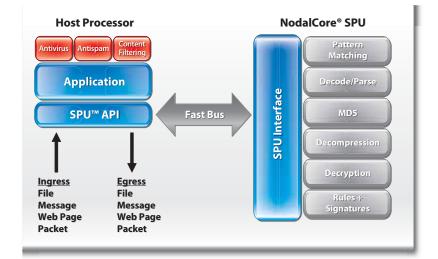

Sensory Networks has designed a co-processing solution called the NodalCore Security Processing Unit (SPU) based on Xilinx® Virtex<sup>TM</sup>-II Pro and Virtex-4 FPGAs (Figure 3). The NodalCore architecture can be used in conjunction with a CPU- or NPU-based system to bridge the performance and scalability gap by providing the computational power necessary for the next generation of adaptable security products.

The NodalCore SPU is designed to offload and accelerate bottleneck operations associated with high-performance network security applications such as antivirus, anti-spam, anti-spyware, intrusion detection, and content classification (Figure 4). The NodalCore SPU's dedicated regular expression pattern-matching engine operates with compressed signature databases stored in external SRAM or RLDRAM memory. Using patent-pending high-performance matching algorithms and a scalable architecture, the SPU can achieve data throughput as high as 1.6 Gbps per bank of RLDRAM memory.

Sensory Networks' CorePAKT massive memory architecture (MMA) compression technology ensures that compiled signature databases occupy a memory footprint smaller than any other competing technology on the market. Compression rates of more than 90% are possible, meaning that databases of more than 10 million signatures are easily supported. The ability to store multiple databases in a compressed format while still achieving gigabit throughputs makes NodalCore technology ideal for applications demanding high performance on large signature databases. The NodalCore SPU is one of the only products on the market that can provide wire-speed performance on full commercial antivirus databases that often contain hundreds of thousands of signatures.

The SPU is a packet-based architecture with standard PCI-64/66, QDR, and soonto-be-released PCI-X and PCI-Express interfaces, allowing seamless integration with standard host systems. The ability to process packets in parallel and rapidly adapt to hostile network security threats is a key differentiator of Sensory Networks' technology. The NodalCore SPU architecture allows hardware modules to be upgraded in the field to deal with new attacks, content types, and application demands.

### **Heart and Soul**

Virtex-II Pro and Virtex-4 FPGAs provide the foundation for NodalCore technology. The dynamic environment of network threats requires a reconfigurable solution with the processing power to handle deep packet inspection – something that cannot be solved by pure general-purpose CPUs or NPUs without encountering performance and scalability issues. A FPGA-based configurable co-processing solution enables security devices to:

- Adapt to changing threats

- Meet performance and scalability requirements

Figure 4 – SPU architecture

- Support a broad range of features and performance at various price points

- Provide phased product releases

- Achieve fast time to market

The Virtex product line comprises lowpower and high-performance FPGAs capable of speeds as high as 10.3125 Gbps with built-in multi-gigabit transceivers. Both the Virtex-II and Virtex-4 devices feature embedded PowerPCTM 405 hardware cores that run at speeds as fast as 450 MHz, soft IP cores such as the 32-bit MicroBlaze<sup>TM</sup> RISC processor, and up to 200,000 cells of configurable logic. The Virtex-4 series features a scalable Advanced Silicon Modular Block (ASMBL) architecture that has allowed Xilinx to produce a programmable silicon platform with unprecedented capabilities and configurations to build co-processing solutions.

The NodalCore SPU was initially designed using the Virtex-II Pro FPGA to meet its high-performance and fieldupgradability requirements. The dynamic nature of the network security landscape meant that an FPGA-based solution was a much better fit than an ASIC-based solution.

The ability for appliance vendors to offer after-sale performance upgrades is another important benefit that increases the marketability of Sensory Networks' range of products. The latest NodalCore SPU is designed using the Virtex-4 FPGA because of its higher performance, faster I/O, and attractive cost. It also offers an easy upgrade path to newer and faster FPGA families.

### Porting Security Applications to NodalCore

Developers can easily port new or existing security applications to the NodalCore platform and gain immediate improvements in throughput and accuracy. Sensory Networks provides a comprehensive suite of drivers, libraries, and development tools that abstract the hardware layers behind fully-featured C and C++ APIs. You can push bottleneck functionality down to the hardware by making simple function calls to pass the data.

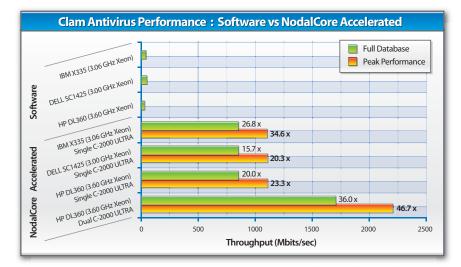

To demonstrate this process, Sensory Networks has ported Clam Antivirus to the NodalCore platform and shown as much as a 50x performance improvement. Clam AV is one of the world's largest open-source antivirus projects, and is used by many large telecommunications companies and managed service providers (see *www.clamav.net*). An analysis of Clam AV showed that the pattern-matching portion of the code was a severe bottleneck, so a NodalCore C-2000 accelerator card was added to the appliance.

Using Sensory Networks' C++ API and Linux device drivers (Clam AV runs under Linux), the pattern-matching code was pushed down to the NodalCore hardware. This meant that the virus signatures also needed to be loaded onto the C-2000. Thanks to Sensory Networks' CorePAKT memory compression technology, the

Figure 5 – Antivirus throughput comparison

entire ClamAV virus database (more than 40,000 virus signatures) was compiled and loaded onto the card. The resulting improvement in throughput is illustrated in Figure 5, using different base platforms for comparison.

### **Integrating Commercial Security Applications**

If you do not wish to develop your own security applications, you can select from a wide variety of commercial plug-in applications that run on the NodalCore platform. Sensory Networks has a range of industryleading application partners that provide best-of-breed antivirus, anti-spam, antispyware, intrusion detection, and content filtering applications. In addition, Sensory Networks supports a wide range of opensource security applications such as Clam AV, Spam Assassin, DSpam, and Snort that are fully ported and tested.

These applications can be quickly and easily integrated without the need to write code, providing "security on tap." You simply need to design a Xilinx Virtex-4 FPGA onto the motherboard (or use a separate PCI card) and install the software to have a security product with market-leading performance. Sensory Networks has a range of reference designs available, and an expert consulting services team that can assist with aspects of this development.

### Conclusion

Because of the growing number and sophistication of network attacks, designers of network appliances must integrate specialized security processing hardware. This hardware needs to provide gigabit throughput, support very large signature databases, and adapt to new types of threats.

Sensory Networks provides a range of solutions based on the Virtex FPGA family that allow you to quickly and easily integrate security applications into network appliances.

To download white papers, datasheets, and API reference documentation for the NodalCore SPU, visit *www.sensorynetworks.com*. Development kits can be ordered online. To learn more about implementing reconfigurable computing solutions, contact *sriram.chelluri@xilinx.com*.

Honey, will you please tell Alex to stop programming the FPGA!

### Viva! Absurdly Easy.

### Viva! Software

### The Easiest Development Tool for Programming FPGAs

Viva may just be the easiest and most intuitive development tool ever created for FPGAs. That's because only Viva delivers a true data set recursive and polymorphic object oriented programming language with a graphical, drag-and-drop interface. In fact, Viva is so easy you can get the hang of it in a just few minutes. Whether you're working with FPGAs in high-performance or embedded environments, Viva is the right solution for you. And Viva is perfectly suited for use with hardware from SGI, Nallatech and Digilent, including Xilinx Starter Kits. Find out why organizations like NASA and the US Air Force use Viva! software to program FPGAs. Visit www.starbridgesystems.com/viva or call (801) 984-4444 today.

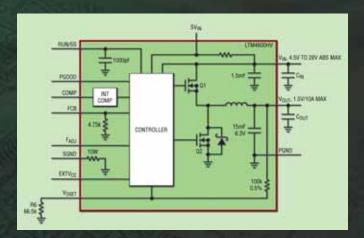

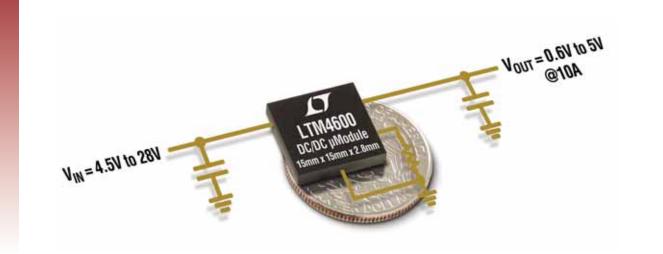

## Designing for Power Budgets and Effective Thermal Management

Xilinx provides the critical edge with power-optimized FPGAs, thermal-efficient packaging, and power analysis tools.

by Anil Telikepalli Sr. Manager, Virtex Solutions Xilinx, Inc. anil.telikepalli@xilinx.com

Meeting power and thermal budgets is one of the essential criteria by which our customers measure the success of their FPGA-based system designs. Constrained both by the density (bandwidth, logic density, and functionality) of the applications they are creating and the environments in which these systems are deployed, FPGA designers need every advantage as they painstakingly balance performance, cost, reliability, and power.

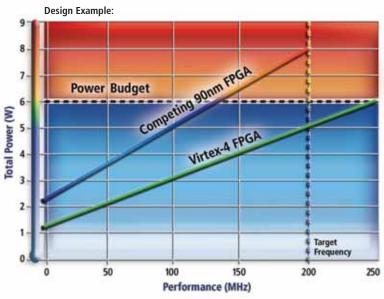

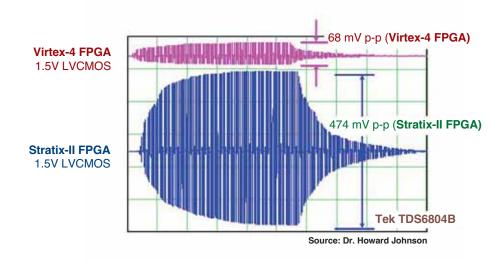

Xilinx demonstrated its commitment to empower its customers' success with the introduction of the Virtex<sup>TM</sup>-4 family of FPGAs. Delivering the lowest total power in any 90 nm high-performance FPGA without compromising performance (1 to 5W lower than any competing 90 nm device), Virtex-4 devices employ a variety of powersaving design techniques to provide the lowest inrush current, static power, and dynamic power. (For more details about the Virtex-4 power advantage, please see "Power vs. Performance: The 90 nm Inflection Point" in the August 2005 issue of the *Power Management Solution Guide*, *www.xilinx.com/solguides.*)

This substantial power advantage provided by Virtex-4 devices translates directly to additional measurable benefits in performance, cost, and reliability. Reducing the FPGA's contribution to total power in a given design alleviates a host of problems incurred by excessive power.

### What Cost Power?

Excessive power is expensive in many ways. It creates the need for special system design and operational considerations such as electricity changes and battery back-up costs. Increased power requires more of everything, including more area on the PCB, a larger chassis, more floor space, and larger air-conditioning systems. And because dynamic power is a function of clock frequency, you may be forced to run a design at a lower performance just to keep total power consumption low.

Perhaps the most critical issue is the effect excessive power can have on reliability. Continuously operating systems with junction temperatures running from 85°C to more than 100°C increase reliability issues and decrease mean time between failures (MTBF).

### **Power and Thermal Budgets**

Every system has a power and thermal budget driven by a standard such as NEBS, ETSI, or other requirements (see sidebar, "NEBS"). A look at various types of electronic equipment can provide valuable insight into the importance of power budgets and demonstrate how a seemingly small power savings for each FPGA can translate into enormous value within overall system operation.

### Infrastructure Equipment

Metro aggregation systems (such as enterprise Ethernet/layer 2 switches and multiservice provisioning platforms) are typically deployed in temperature-controlled rooms to ensure acceptable transistor junction temperatures. A typical multi-service provisioning platform (MSPP) is populated with multiple line cards supporting a range of data and voice transmission standards. Each line card usually contains numerous ASSPs, ASICs, and FPGAs.

Figure 1 – Heat transfer in devices and how Virtex-4 FPGAs address them

For an FPGA that performs connectivity and traffic management functions, reducing power is critical to system reliability and operational costs. Using a poweroptimized FPGA that saves 1-5W per device will dramatically impact the MSPP's total power, potentially allowing the use of smaller power supplies and reducing the size and number of heat sinks.

Now consider wireless base stations that are deployed outdoors in harsh environmental conditions with ambient temperatures exceeding 80°C and transistor junction temperatures in excess of 100°C. A typical wireless network may comprise as many as 35,000 base stations, with each base station utilizing 16 or more line cards.

Wireless base station power budgets are 1.2-2.5 KW; each line card (excluding backplane, fans, and system control) is about 20W. Using an FPGA for connectivity and signal processing, which saves as much as a third of the typical 6W power budget, can in turn save as much as \$1 million in operational expenditures.

### System Reliability Case Study

As stated previously, many applications are restricted in power by standards. Consider the networking OEMs who sell their equipment to operators and service providers. In the U.S., the operators require OEMs to meet NEBS (National Equipment Building Systems) standards. In particular, the GR-63-CORE and GR- 1089-CORE standards specify equipment reliability criteria, on which the power, signal integrity, and thermal management of the equipment (and hence the components used) have a direct impact.

For example, consider an RPR (Resilient Packet Ring) MSPP. Such a system is limited to 4 KW/rack and must remain operational for 99.999% of the time, which equates to no more than five minutes of downtime per year.

Because FPGAs are used extensively in these systems within the various line cards, it is critical to keep the FPGA static and dynamic power consumption to an absolute minimum to help OEMs meet the GR-63-CORE standard.

The typical line card power budgets and FPGA power consumption illustrate the value Virtex-4 FPGAs offer by saving a just couple of watts per FPGA:

- 12-port DS3 card: 30W; FPGA = 4-5W

- 4-port OC-12 card: 28W; FPGA = 4-5W

- 12-port 10/100 Base-T card: 50W; FPGA = 4-5W

- 32-port T1/E1: 9W; FPGA = 2-3W

### **Thermal Management**

Given the increasing criticality with which system vendors are scrutinizing their power and thermal budgets, Xilinx continues to strive to improve upon the edge it already provides with the Virtex-4 family.

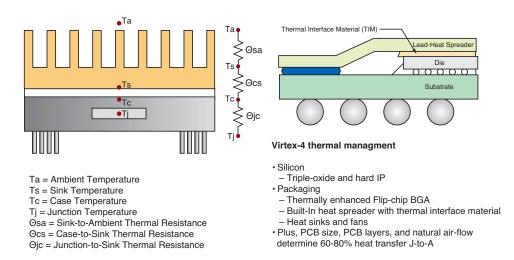

Figure 1 shows heat transfer at various locations on a device with definitions of temperature and thermal resistance at each point. In addition to the effective thermal management Virtex-4 FPGAs provide at the silicon level, Xilinx also offers thermally enhanced flip-chip packages with built-in heat spreaders.

The new Xilinx flip-chip BGA packages are the latest package offering for Xilinx high-performance FPGA products. Unlike traditional packaging in which the die is attached to the substrate face-up and the connection is made by using wire, the solder bumped die in the flip-chip BGA is flipped over and placed face down, with the conductive bumps connecting directly to the matching metal pads on the laminate substrate.

The flip-chip package accommodates more I/O pins than traditional wire-bond packages by using the internal chip area for package connections. Furthermore, the cavity-up nature of flip-chip packages allows for superior thermal dissipation through the top of the package.

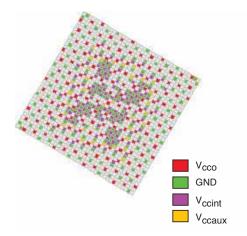

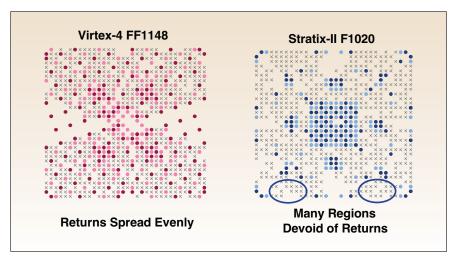

Virtex-4 pinout provides abundant power and ground pins (Figure 2) – one adjacent to every user pin, providing even distribution for better thermal dissipation when compared to the clustered power and ground pins found in typical flipchip packages.

To facilitate user design, Xilinx provides

Figure 2 – Virtex-4 packaging, with uniform distribution of power and ground pins, enables better thermal dissipation.

### Xilinx Virtex-4 Web Power Tool Version 7.1

|                                                                     | Veitage (V)     | Intimated Parent (WW)                | Estimated Current (mA) |

|---------------------------------------------------------------------|-----------------|--------------------------------------|------------------------|

| V <sub>COM1</sub> 1.2V                                              | 12              | 95                                   | 48                     |

| Volatia 2.9V                                                        | 28              | 42                                   | 11                     |

| Cos 2.3/ Power (mm)                                                 | 23              | *                                    |                        |

| COB 2.0( Power (mmt)                                                | 2.9             | 8.                                   |                        |

| CCB 1.0/ Fower (mill)                                               | 1.8             | 1                                    | 3                      |

| COB 1.5/ Fever (mH)                                                 | 15              | 0                                    | (B.).                  |

| oce 1.3/ Pawer (mill)                                               | u               | 4.                                   | 8                      |

|                                                                     | SatalPears)     | 145                                  | NAR                    |

| V <sub>DCB</sub> 1.3/ Palwer (mill)<br>No. In a privalgeneration, h | Satal Person    |                                      | 2 NA                   |

| uis chevel.                                                         |                 | Same and Sugar                       |                        |

| r Juis cheef.                                                       |                 | - To <u>(100)</u> or a special (100) | -                      |

| dals cheel.<br>Local information on Nie w                           |                 | The Loss of the American Const.      |                        |

| e date cheel.<br>e date bite malled on Nie w                        | when average to |                                      |                        |

Figure 3a – The Web Power tool allows you to set the operating voltage for the design; when feasible, this enables you to lower the voltage to save power.

|   | frequencia<br>participation of | tioner<br>Tione |      | 1101         |     | Arresta<br>Tanta<br>Rate (14 | Artest al<br>Resident<br>Dest |     |

|---|--------------------------------|-----------------|------|--------------|-----|------------------------------|-------------------------------|-----|

|   |                                | E               | 1.4  | 11           | ю.  | 1.1                          | -                             | ۰.  |

|   | 14                             | 2               | 1.1  | F.1.         | 8   |                              | 1                             | 4   |

| - | 18                             | 9.1             | 19   | 9.1          | 10  | 1.1                          |                               | ¥   |

|   | 128                            | 3               |      | 3            | 1   | 4                            | 1.00 -                        | 8   |

|   | 1.0                            | 8.              | 3    | 3.1          | 1   | 10.                          | 1.00 00                       | ÷ . |

|   |                                |                 | 10   | 3.1          | 1.  |                              | L= =                          |     |

|   | 1.                             | 1.1             | 4    | 8. L -       | 8.1 | A                            | L= =                          | ۹   |

|   | 18                             | <b>B</b> .S.    |      | 9.1          | 8.  | 4                            | 200 00                        | 87. |

|   |                                | A.S.            | 10.1 | <b>3</b> .11 | 8.  | 1.1                          | L= =                          | 4   |

|   |                                | £.]             |      | 80.          | A   | A                            | L= =                          |     |

| _ |                                |                 |      | 3.1          |     | 8.1                          | 1.00 10                       | ۰.  |

|   |                                |                 | 1.1  | 8.1          |     | 1                            | 100 10                        |     |

|   |                                |                 |      |              |     |                              | Table                         |     |

Figure 3b – You select the particular utilization of slices, flip-flops, shift register and LUT RAMs, their toggle rates, and routing density to calculate the power used by the configurable logic blocks (CLBs).

JEDEC JESD-51 thermal characteristics (http://direct.xilinx.com/bvdocs/userguides/ ug075.pdf) for a four-layer board. Although a four-layer board is quite conservative for most applications, it does provide a uniform standard-based comparison. For simulating your unique board setup, Xilinx can provide compact resistor models for the Virtex-4 device package combination.

### **Power Analysis Tools**

Another edge Xilinx offers its customers is the ability to calculate power estimates both before and after design implementation. Xilinx Web Power tools provide preimplementation estimates of a design's power consumption based on the expected utilization of device resources, operating frequencies, and toggle rates.

Post-implementation, XPower enables

### Web Power

Xilinx Web Power tools help you estimate total power consumption accurately before design implementation. System architects can estimate power using high-level design details and make intelligent design choices on clock frequencies, implementing a function using hard IP or

logic, type of I/O standard, and other factors. The Web Power tool relies exclusively on your estimates of FPGA design parameters such as utilization, toggle rates, and operating conditions (Figure 3a/3b).

To calculate a power estimate for a given design, simply enter the estimated design parameters for resource utilization, operating environment, clock rates, and toggle rates, push a button to calculate power, and save the settings. A brief look reveals the intuitively simple nature of this process:

- 1. Set the operating voltage of the design.

- 2. Enter the settings for the part and

package, typical or worst case process, and thermal information (ambient temperature and airflow).

- 3. Select the particular utilization of slices, flip-flops, shift register and RAM LUTs, their toggle rates and routing density, to calculate the power used by the configurable logic blocks (CLBs).

- Specify the number of DSP48s, their architectural usage level, and toggle rates.

- 5. Select the digital clock manager (DCM) settings.

- 6. Specify input/output settings.

- Press the "calculate" button to generate the pre-implementation power estimate with totals at every level.

- Press the "save settings" button to save the settings for future analysis and modifications.

### XPower

Xilinx XPower is a post-implementation power analysis and power estimation software. Included in all configurations of the Xilinx Integrated Software Environment (ISE<sup>TM</sup> software), XPower enables you to analyze total device power.

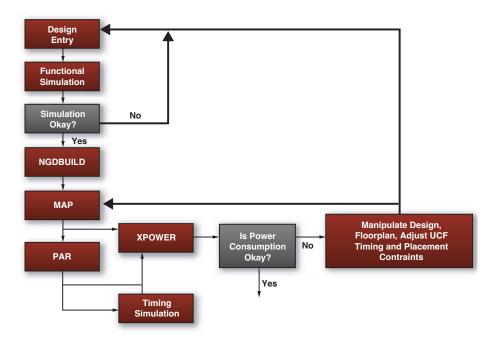

Figure 4 – You can run XPower after map, place and route, or timing simulation.

XPower can read HDL simulation data to estimate toggle rates. XPower uses proprietary algorithms to estimate toggle rates even if the simulation vectors are missing, which is useful for iterative design. Figure 4 shows XPower in the design flow.

XPower includes a design wizard that provides a step-by-step dialog box format to help you import design and simulation data and set loading and default data. The design wizard also helps you get accurate power estimates quickly and easily.

The step-by-step process for using XPower is straightforward and intuitive:

- 1. Invoke XPower in ISE software.

- 2. Open design.

- 3. Load design (NCD).

- 4. Load optional PCF and simulation data files.

- 5. Launch the new design wizard.

- 6. Set voltage, ambient temperature, and airflow.

- 7. Set frequencies and activity rates.

- 8. Set capacitive loads for outputs.

- 9. Set/verify DC loads for outputs.

- Set/verify enable rates for bi-directional I/Os if simulation data is not loaded.

- 11. Set global default activity to estimated value.

- 12. Set estimated activity for any single or groups of signals.

### **Corroborative Results**

Given the value of these power estimation and analysis tools and the essential need for accuracy both before and after the design has been implemented, you might wonder just how much of an advantage these tools provide.

Of course, a great deal hinges on the accuracy of the settings relative to actual design parameters and operating conditions. Nonetheless, Xilinx offers the results of this simple, yet revealing test example as evidence of the veracity of these power tools.

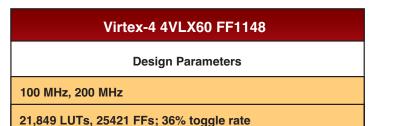

Using a Virtex-4 4VLX60 device, we tested for a correlation of logic, register, and interconnect power across a large design. We ran the design through ISE 7.1i software and compared the power data to estimates developed by the Web Power tool and measurements in a lab. The results in Figure 5 speak for themselves.

| Power Data Comparison – Dynamic |                |             |               |  |  |  |  |

|---------------------------------|----------------|-------------|---------------|--|--|--|--|

| Frequency (MHz)                 | Web Power (mW) | XPower (mW) | Measured (mW) |  |  |  |  |

| 0                               | 0              | 0           | 0             |  |  |  |  |

| 100                             | 1,864          | 1,750       | 1,742         |  |  |  |  |

| 200                             | 3,727          | 3,429       | 3,482         |  |  |  |  |

Figure 5 – When compared with actual measured results, the close approximation of the pre- and post-implementation power estimation tools demonstrates the value these tools provide to system architects and FPGA designers.

### Conclusion

Designing high-performance FPGAbased systems constrained by exacting power and thermal budgets will never cease to present a daunting challenge to the design engineers and architects who must regularly build them.

As Xilinx customers continue to place their trust in our ability to provide them with the essential edge in power-optimized FPGAs, tools, and package technology, we have and will continue to strive to reduce the challenge of effective power and thermal management. For more information, visit *www.xilinx.com/ virtex4/lowpower.*

### **NEBS**

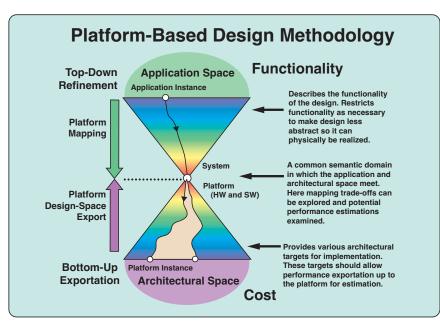

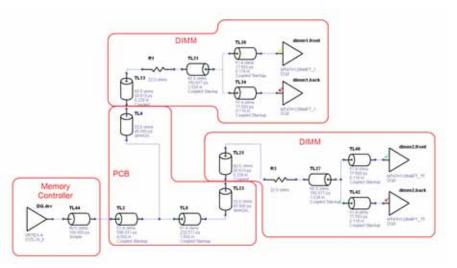

The National Equipment Building Systems (NEBS) standards prevent the target system from interfering with other equipment, while ensuring scalability and safety. The two major standards, GR-63-CORE and GR-1089-CORE, were originally developed by Bellcore/Telcordia in the 1970s and deployed in 1985.