THE AUTHORITATIVE JOURNAL FOR PROGRAMMABLE LOGIC USERS

## ESL Expands the Reach of FPGAs

## INSIDE

ESL Tools Make FPGAs Nearly Invisible to Designers

Evaluating Hardware Acceleration Strategies Using C-to-Hardware Tools

The Benefits of FPGA Coprocessing

Accelerating System Performance Using ESL Design Tools and FPGAs

Tune Multicore Hardware for Software

## Support Across The Board.

## Jump Start Your Designs with Mini-Module Development Platforms

## Mini-Module Features

- Small footprint (30 mm x 65.5 mm)

- Complete system-on-module solution with SRAM, Flash, Ethernet port and configuration memory

- Supports MicroBlaze™ or PowerPC® processors

- Based on the Virtex<sup>™</sup>-4 FX12 and 400K Gate Spartan<sup>™</sup>-3 FPGAs

- 76 User I/O

## **Baseboard Features**

- Supports mini-module family

- Module socket allows easy connection

- Provides 3.3 V, 2.5 V and 1.2 V

- USB and RS232 ports

- 2 x 16 character LCD

## Upcoming SpeedWay Design Workshops

- Developing with MicroBlaze

- Developing with PowerPC

- Xilinx Embedded Software Development

- Embedded Networking with Xilinx FPGAs

The Xilinx® Spartan<sup>™</sup>-3 and Virtex<sup>™</sup>-4 FX 12 Mini-Modules are off-the-shelf, fully configurable, complete system-on-module (SOM) embedded solutions capable of supporting MicroBlaze<sup>™</sup> or PowerPC® embedded processors from Xilinx.

Offered as stand-alone modules and as development kits with companion baseboards, power supplies, software and reference designs, these modules can be easily integrated into custom applications and can facilitate design migration.

Gain hands-on experience with these development kits and other Xilinx tools by participating in an Avnet SpeedWay Design Workshop™ this spring.

Learn more about these mini-modules and upcoming SpeedWay Design Workshops at:

www.em.avnet.com/spartan3mini www.em.avnet.com/virtex4mini www.em.avnet.com/speedway

Avnet Green Initiative

Enabling success from the center of technology™

1 800 332 8638 em.avnet.com

## XCell journal

| PUBLISHER             | Forrest Couch<br>forrest.couch@xilinx.com<br>408-879-5270                  |

|-----------------------|----------------------------------------------------------------------------|

| EDITOR                | Charmaine Cooper Hussair                                                   |

| ART DIRECTOR          | Scott Blair                                                                |

| ADVERTISING SALES     | Dan Teie<br>1-800-493-5551                                                 |

| TECHNICAL COORDINATOR | Milan Saini                                                                |

| INTERNATIONAL         | Dickson Seow, Asia Pacific<br>dickson.seow@xilinx.com                      |

|                       | Andrea Barnard, Europe/<br>Middle East/Africa<br>andrea.barnard@xilinx.com |

|                       |                                                                            |

Yumi Homura, Japan yumi.homura@xilinx.com

SUBSCRIPTIONS

All Inquiries www.xcellpublications.com

REPRINT ORDERS

1-800-493-5551

www.xilinx.com/xcell/

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 Phone: 408-559-7778 FAX: 408-879-4780 www.xilinx.com/xcell/

© 2006 Xilinx, Inc. All rights reserved. XILINX, the Xilinx Logo, and other designated brands included herein are trademarks of Xilinx, Inc. PowerPC is a trademark of IBM, Inc. All other trademarks are the property of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilinx makes no warranties, express, implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against Xilinx for any loss, damage, or expense caused thereby.

# A Shortcut to Success

This issue of the *Xcell Journal* features a very cohesive collection of articles about electronic system level (ESL) design. ESL is an umbrella term for tools and methods that allow designers with software programming skills to easily implement their ideas in programmable hardware (like FPGAs) without having to learn traditional hardware design techniques. The proliferation of these tools will make it easier for designers to use programmable devices for algorithm acceleration, high-performance computing, high-speed packet processing, and rapid prototyping.

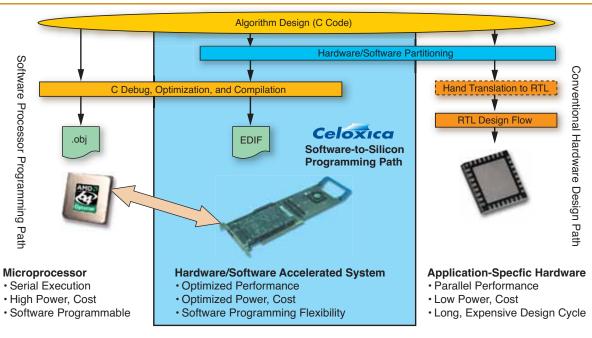

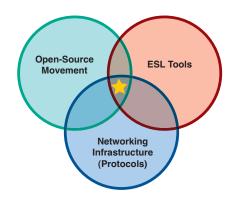

In an effort to organize those vendors developing ESL products, in March 2006 Xilinx launched the ESL Initiative, inviting companies such as Celoxica and Impulse Accelerated Technologies to optimize support for Xilinx<sup>®</sup> embedded, DSP, and logic platforms and to establish common standards for ESL tool interoperability, among other goals.

Xilinx also set its own standards for participation in the ESL Initiative. To qualify as a partner, a company's ESL methodologies must be at a higher level of abstraction than RTL. They must also demonstrate a working flow for FPGAs and position their tools as an FPGA solution rather than an ASIC solution that also happens to work with FPGAs. Participants were additionally invited to write an article for this issue.

We also invited *FPGA Journal* Editor Kevin Morris to share his thoughts about ESL, and as you'll see he offers quite a interesting perspective. Depending on who you talk to, ESL is either all hype or the real deal. At Xilinx, we've committed to this promising technology – working with a variety of vendors (12 and growing) whose solutions are designed for a variety of applications.

I invite you to learn more about ESL and particularly each company's respective products by delving further into this issue of the *Xcell Journal*, or by visiting *www.xilinx.com/esl*.

mant Couch

Forrest Couch Publisher

## ON THE COVER

## Evaluating Hardware Acceleration Strategies Using C-to-Hardware Tools

Software-based methods enable iterative design and optimization for performance-critical applications.

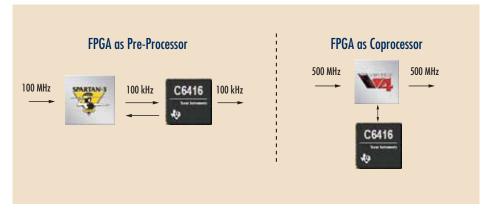

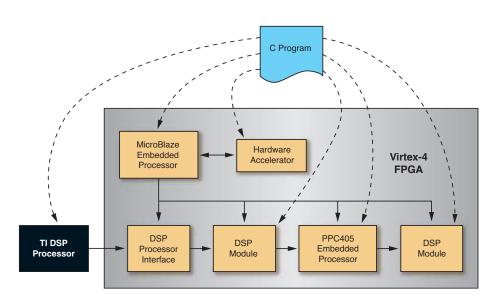

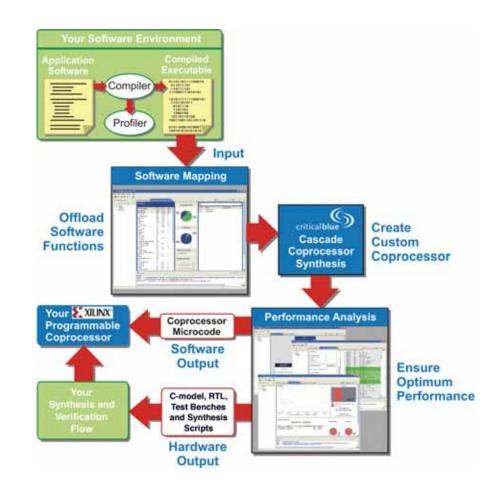

The Benefits of FPGA Coprocessing The Xilinx ESL Initiative brings the horsepower of an FPGA coprocessor closer to the reach of traditional DSP system designers.

Accelerating System Performance Using ESL Design Tools and FPGAs ESL design tools provide the keys for opening more applications to algorithm acceleration.

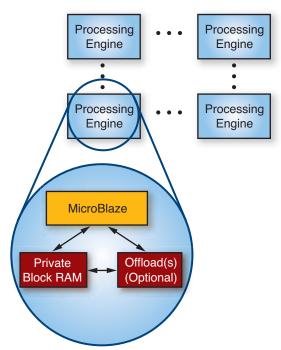

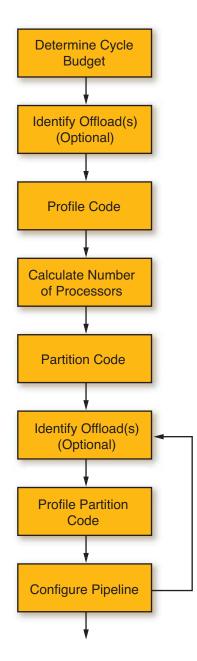

**Tune Multicore Hardware for Software** Teja FP and Xilinx FPGAs give you more control over hardware configuration.

Viewpoint

**ESL Tools Make FPGAs Nearly Invisible to Designers** You can increase your productivity through ESL methodologies.

## THIRD QUARTER 2006, ISSUE 58

## Xcelljournal

## VIEWPOINTS

| ESL Tools Make FPGAs Nearly Invisible to Designers | 6 |

|----------------------------------------------------|---|

|                                                    |   |

| Join the "Cool" Club                               | 9 |

## ESL

| Bringing Imaging to the System Level with PixelStreams                     |    |

|----------------------------------------------------------------------------|----|

| Evaluating Hardware Acceleration Strategies Using C-to-Hardware Tools      |    |

| Accelerating Architecture Exploration for FPGA Selection and System Design | 19 |

| Rapid Development of Control Systems with Floating Point                   |    |

| Hardware/Software Partitioning from Application Binaries                   | 26 |

| The Benefits of FPGA Coprocessing                                          | 29 |

| Using SystemC and SystemCrafter to Implement Data Encryption               | 32 |

| Scalable Cluster-Based FPGA HPC System Solutions                           | 35 |

| Accelerate Image Applications with Poseidon ESL Tools                      |    |

| Accelerating System Performance Using ESL Design Tools and FPGAs           | 41 |

| Transforming Software to Silicon                                           | 46 |

| A Novel Processor Architecture for FPGA Supercomputing                     | 49 |

| Turbocharging Your CPU with an FPGA-Programmable Coprocessor               | 52 |

| Tune Multicore Hardware for Software                                       | 55 |

| Automatically Identifying and Creating Accelerators Directly from C Code   | 58 |

## GENERAL

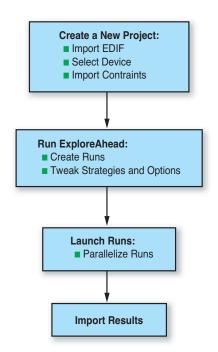

| ExploreAhead Extends the PlanAhead Performance Advantage          | 62 |

|-------------------------------------------------------------------|----|

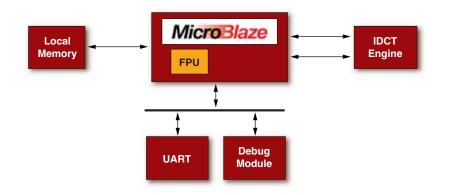

| Designing Flexible, High-Performance Embedded Systems             | 66 |

| Tracing Your Way to Better Embedded Software                      | 70 |

| To Interleave, or Not to Interleave: That is the Question         | 74 |

| Using FPGA-Based Hybrid Computers for Bioinformatics Applications | 80 |

| II DRR Delivers High-Performance SDR                              | 84 |

| Eliminate Packet Buffering Busywork                               | 88 |

REFERENCE.

# ESL Tools Make FPGAs Nearly Invisible to Designers

You can increase your productivity through ESL methodologies.

by Steve Lass Sr. Director, Software Marketing Xilinx, Inc. steve.lass@xilinx.com

FPGA business dynamics have been rather consistent over the past decade. Price per gate has continued to fall annually by an average of 25%, while device densities have continued to climb by an average of 56%. Concurrent with advances in silicon, design methodologies have also continued to evolve.

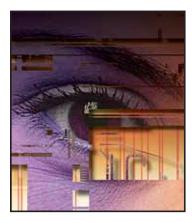

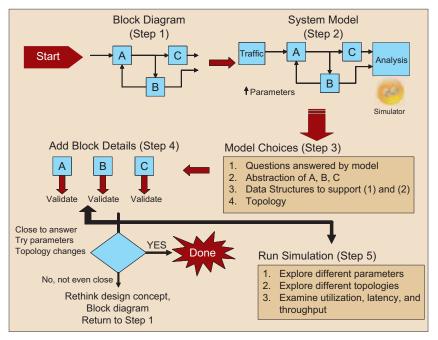

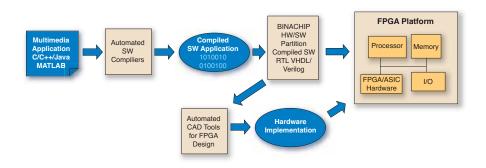

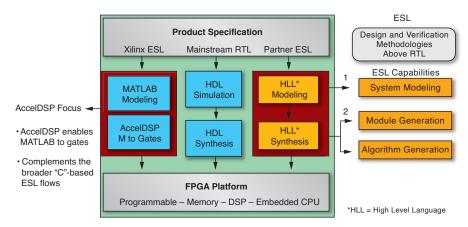

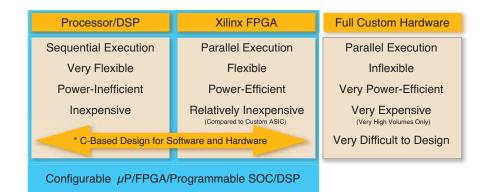

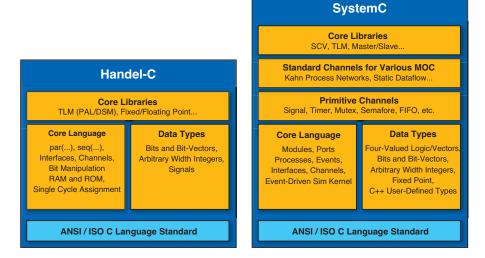

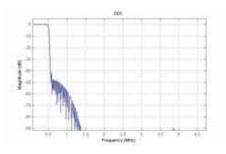

In particular, a new paradigm known as electronic system level (ESL) design is promising to usher in a new era in FPGA design. Although the term ESL is broad and its definition subject to different interpretations, here at Xilinx it refers to tools and methodologies that raise design abstraction to levels above the current mainstream register transfer level (RTL) language (Figure 1).

Xcell Journal

Figure 1 – Design methodologies are evolving to HLL-based system-level design.

Put another way, it is now possible for you to capture designs in high-level languages (HLLs) such as ANSI C and implement them in an optimized manner on FPGA hardware. These advances in software methodologies – when combined with the increasing affordability of FPGA silicon – are helping to make programmable logic the hardware platform of choice for a wide and rapidly expanding set of target applications.

### **Defining the Problem**

You might wonder what problem ESL is trying to solve. Why is it needed? To answer this, let's consider the following three scenarios. First, many of today's design problems originate as a software algorithm in C. The traditional flow to hardware entails a manual conversion of the C source to equivalent HDL. ESL adds value by providing an automatic conversion from HLL to RTL or gates. For those wishing to extract the most performance, you can optionally hand-edit the intermediate RTL.

Second, for both power and performance reasons, it is clear that traditional processor architectures are no longer sufficient to handle the computational complexity of the current and future generation of end applications. ESL is a logical solution that helps overcome the challenges of processor bottlenecks by making an easy and automated path to hardware-based acceleration possible.

Third, as the types of appliances that can now be deployed on FPGAs become more sophisticated, traditional simulation methods are often not fast enough. ESL methodologies enable faster system simulations, utilizing very high speed transactionbased models that allow you to verify functionality and perform hardware/software trade-off analysis much earlier in the design cycle.

## Value Proposition for FPGAs

ESL technologies are a unique fit for programmable hardware. Together, ESL tools and FPGAs enable a desktop-based development environment that allows applications to target hardware using standard software-development flows. You can design, debug, and download applications developed using HLLs to an FPGA board much the same way that you can develop, debug, and download code to a CPU board.

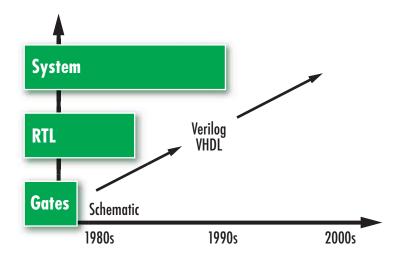

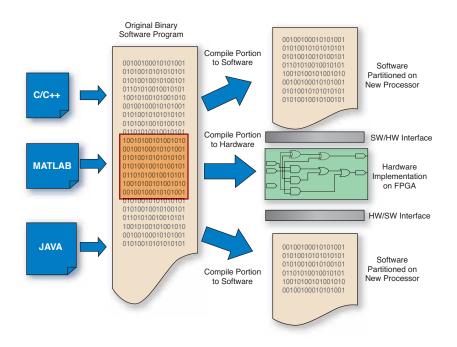

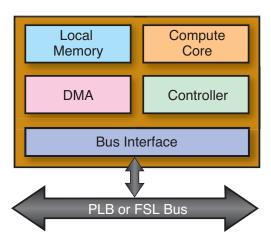

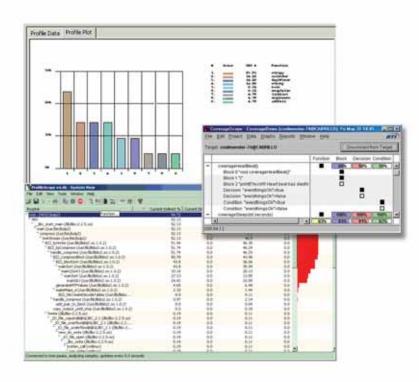

Additionally, with powerful 32-bit embedded processors now a common feature in FPGAs, you can implement a complete system – hardware and software – on a single piece of silicon. Not only does this provide a high level of component integration, but with the help of ESL tools, it is now easy and convenient to dynamically partition design algorithms between the appropriate hardware (FPGA fabric) and software (embedded CPU) resources on the chip (Figure 2).

ESL brings a productivity advantage to both current FPGA hardware designers as well as to a potentially large number of software programmers. Hardware engineers are using HLL-based methods for rapid design prototyping and to better manage the complexity of their designs. Software developers, interested in accelerating their CPU bottlenecks, are using ESL

Figure 2 – ESL facilitates dynamic hardware/software partitioning conveniently possible in FPGAs.

7

## ESL adds value by being able to abstract away the low-level implementation details associated with hardware design. By doing so, the tools simplify hardware design to such an extent so as to render the hardware practically "invisible" to designers.

flows to export computationally critical functions to programmable hardware.

ESL adds value by being able to abstract away the low-level implementation details associated with hardware design. By doing so, the tools simplify hardware design to such an extent so as to render the hardware practically "invisible" to designers. This helps expand the reach of FPGAs from the traditional base If you remain skeptical about the role of HLLs in hardware design, you are not alone. Your concerns might range from compiler quality of results and tool easeof-use issues to the lack of language standardization and appropriate training on these emerging technologies. The good news is that ESL suppliers are aware of these challenges and are making substantial and sustained investments to advance

| Partner       | From HLL<br>To FPGA | Xilinx CPU<br>Support | Description (Key Value)                                                           |  |

|---------------|---------------------|-----------------------|-----------------------------------------------------------------------------------|--|

| Bluespec      | ~                   |                       | SystemVerilog-Like to FPGA (High QoR )                                            |  |

| Binachip      | ~                   | ~                     | Processor Acceleration (Accelerates Binary Software Code in FPGA)                 |  |

| Celoxica      | ~                   | ~                     | Handel-C, SystemC to FPGA (High QoR)                                              |  |

| Cebatech      | ~                   |                       | ANSI C to FPGA (Time to Market)                                                   |  |

| Critical Blue | ~                   |                       | Co-Processor Synthesis (Accelerates Binary Software Code in FPGA)                 |  |

| Codetronix    | ~                   | ~                     | Multi-Threaded HLL for Hardware/Software Design (Time to Market)                  |  |

| Impulse       | ~                   | ~                     | Impulse-C to FPGA (Low Cost)                                                      |  |

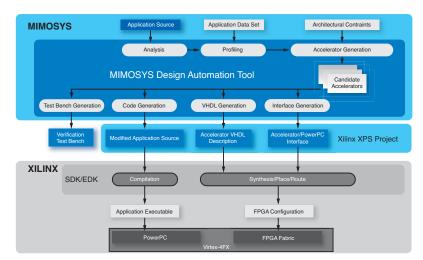

| Mimosys       | ~                   | ~                     | PowerPC APU-Based Acceleration (Ease of Use)                                      |  |

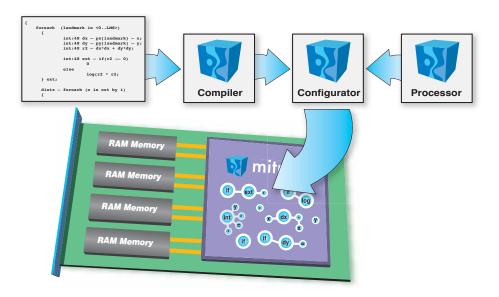

| Mitrion       | ~                   |                       | Mitrion-C to FPGA (Supercomputing Applications)                                   |  |

| Mirabilis     |                     | ~                     | High-Speed Virtual Simulation<br>(Perform Hardware/Software Trade-Off Analysis)   |  |

| Nallatech     | ~                   |                       | Dime-C to FPGA (High-Performance Computing Applications)                          |  |

| Poseidon      | ~                   | ~                     | MicroBlaze/PowerPC Acceleration<br>(Analysis, Profiling, and C Synthesis)         |  |

| SystemCrafter | ~                   |                       | SystemC to FPGA (Rapid Prototyping)                                               |  |

| Teja          | ~                   | ~                     | Distributed Processing Using MicroBlaze/PowerPC<br>(High-Speed Packet Processing) |  |

Table 1 – Xilinx partners provide a wide spectrum of system-level design solutions.

of hardware designers to a new and potentially larger group of software designers, who until now were exclusively targeting their applications to processors. As there are many more software developers in the world than hardware designers, this equates to a large new opportunity for FPGAs. the state of the art. These efforts are beginning to yield results, as evidenced by an increasing level of interest from end users. For instance, more than two-thirds of the engineers in a Xilinx<sup>®</sup> survey expressed a keen interest in learning about the capabilities of ESL. Xilinx estimates that hundreds of active design seats exist where ESL methods are being used with FPGAs to solve practical problems.

You may also be wondering if ESL will signal the end of current RTL-based design methodologies. Although there is little doubt that ESL should be regarded as a disruptive technology, ESL flows today are positioned to complement, rather than compete, with HDL methods. In fact, several ESL tools write out RTL descriptions that are synthesized to gate level using current RTL synthesis. And there will always be scenarios where design blocks may need to be hand-coded in RTL for maximum performance. By plugging into the existing well-developed infrastructure, ESL can help solve those design challenges not addressed by current methodologies.

## **Next Steps**

If you are looking for a place to begin your orientation on ESL and FPGAs, a good place to start would be the ESL knowledge center at *www.xilinx.com/esl*. In March 2006, Xilinx launched the ESL Initiative – a collaborative alliance with the industry's leading tool providers to promote the value, relevance, and benefits of ESL tools for FPGAs (Table 1). The website aims to empower you with knowledge and information about what is available and how to get started, including information on lowcost evaluation platforms that bundle FPGA boards with ESL software and design examples.

This issue of the *Xcell Journal* features a range of articles on ESL and FPGAs written by engineers at Xilinx as well as our ESL partners. These articles are designed to give you better insights into emerging ESL concepts. You may find that some of these technologies do indeed present a better approach to solving your design challenges. We hope that some of you will feel inspired to take the next step and become part of the growing number of early adopters of this unique and revolutionary new methodology.

# Join the "Cool" Club You're not doing ESL yet? Loser!

by Kevin Morris Editor – FPGA Journal Techfocus Media, Inc. kevin@techfocusmedia.com

When the Xcell Journal asked me to write a viewpoint

on ESL, I thought, "Hey, why not? They've got 'Journal' in their name and I know all about ESL." ESL is the design methodology of the future. ESL will revolutionize the electronics industry. ESL will generate billions of dollars worth of engineering productivity while the people and companies that develop the technology fight tooth and nail to capture infinitesimal percentages of that sum.

ESL (electronic system level [design]) brings with it a pretentious name and the potential for manic marketing misrepresentation. Although there are excellent ESL products and efforts underway, the early market is a good time for the buyer to beware and for savvy design teams to understand that they are likely to be experimenting with cutting-edge, nascent technology. ESL is also currently an over-broad term, encapsulating a number of interesting but diverse tools and technologies.

In order to understand ESL, we need to hack through the typical layers of marketing hype and confusion to get down to the fundamentals. ESL is not about languages or layers of abstraction. ESL is about productivity. Electronic hardware design (this is important because ESL is a hardware designer's term) is far too inefficient. Forget the fact that we have boosted productivity an order of magnitude or two over the past 20 years because of technology advances in electronic design automation. Moore's Law is a much harsher mistress than that. Do the math. In two decades, the gate count of the average digital design platform has risen by a factor of something like 2K. Even if EDA has managed a 200x improvement in gates per digital designer day, they are falling behind at a rate of more than 5x per decade.

This effect was observed ad-infinitum in practically every EDA PowerPoint presentation given in the 1990s. Logarithmic graphs of gate counts were shown skyrocketing upward exponentially while designer productivity lounged along linearly, leaving what the EDA marketers proudly promoted as "The Gap." This gap (skillfully highlighted and animated by black-belt marketing ninjas) was their battle cry – their call to arms. Without the help of their reasonably priced power tools, you and your poor, helpless electronic system design company would be gobbled up by The Gap, digested by your competitors who were, of course, immune to Moore's Law because of the protective superpower shield of their benevolent EDA suppliers.

This decade, however, The Gap has gone into public retirement. Not because it isn't still there – it is, growing as fast as ever. This pause is because we found a killer-app use for all of those un-designable gap gates, giving us a temporary, one-time reprieve from the doom of design tool deficiency. Our benefactor? Programmability. It has been widely documented that devices like FPGAs pay a steep price in transistor count for the privilege of programmability. Estimates run as high as 10x for the average area penalty imposed by programmable logic when compared with custom ASIC technologies. Dedicate 90% of

9

your logic fabric transistors to programmability, throw in a heaping helping of RAM for good measure, and you've chewed up enough superfluous silicon to leave a manageable design problem behind.

By filling several process nodes worth of new transistors with stuff you don't have to engineer, you've stayed on the productivity pace without having to reinvent yourself. Now, unfortunately, the bill is coming due again. FPGAs have become as complex as ASICs were not that long ago, and the delta is diminishing. Design teams around the world are discovering that designing millions of gates worth of actual FPGA logic using conventional RTL methodologies can be a huge task.

In an ASIC, however, this deficiency in design efficiency was masked by the mask. The cost and effort required to generate and verify ASIC mask sets far exceeded the engineering expense of designing an ASIC with RTL methodologies. Boosting the productivity of the digital designer would be a bonus for an ASIC company, but not a game-changing process improvement. Even if digital design time and cost went to zero, cutting-edge ASIC development would still be slow and expensive.

In FPGA design, there is no such problem to hide behind, however. Digital design is paramount on the critical path of most FPGA projects. Are you an FPGA designer? Try this test. Look outside your office door up and down the corridor. Do you see a bunch of offices or cubes filled with engineers using expensive design-formanufacturing (DFM) software, correcting for optical proximity, talking about "rule decks" and sweating bullets about the prospect of their design going to "tapeout"? Not there, are they? Now look in a mirror. There is your company's critical path.

With ESL the buzzword-du-jour in design automation, everyone in the EDA industry is maneuvering – trying to find a way to claim that what they were already doing is somehow ESL so they can be in the "cool" club. As a result, everything from bubble and block diagram editors to transaction-level simulation to almost-high-level hardware synthesis has been branded "ESL" and rushed to the show floor at the Design Automation Conference, complete with blinking lights, theme music, and special, hush-hush secret sneak-preview demos served with shots of espresso in exclusive private suites.

FPGAs and ESL are a natural marriage. If we believe our premise that ESL technology delivers productivity – translating into a substantial reduction in time to market – we see a 100% alignment with FPGA's key value proposition. People need ESL techniques to design FPGAs for the same reason they turned to FPGAs in the first place –

## FPGA platforms and ESL tools deliver dramatically increased flexibility.

they want their design done now. Secondorder values are aligned as well, as both FPGA platforms and ESL tools deliver dramatically increased flexibility. When design changes come along late in your product development cycle, both technologies stand ready to help you respond rapidly.

With all of this marketing and uncertainty, how do you know if what you're doing is actually ESL? You certainly do not want all of the other designers pointing and laughing at engineering recess if you show up on the playground with some lame tool that isn't the real thing. Although there is no easy answer to that question, we can provide some general guidelines. First, if you are describing your design in any language in terms of the structure of the hardware, what you are doing probably isn't ESL. Most folks agree that the path to productivity involves raising the abstraction layer.

If we are upping our level of abstraction, how will the well-heeled hardware engineer be describing his design circa 2010? Not in RTL. Above that level of abstraction, however, a disquieting discontinuity occurs. Design becomes domain-specific. The natural abstraction for describing a digital signal processing or video compression algorithm probably bears no resemblance to the native design tongue of the engineer developing packet-switching algorithms, for example. As a result, we are likely to see two different schools of thought in design description. One group will continue to pursue generalpurpose specification techniques, while the other charts a course of domain-specificity.

In the software world, there is ample precedent for both ways of thinking. Even though software applications encompass a huge gamut from business to entertainment to scientific, most software engineers manage to develop their applications using one of the popular general-purpose languages like C/C++ or Java. On the other hand, some specialized application types such as database manipulation and user interface design have popularized the use of languages specific to those tasks. Software is a good exemplar for us, because programmers have been working at the algorithmic level of abstraction for years. Hardware design is only just now heading to that space.

The early ESL tools on the market now address specific hot spots in design. Some provide large-scale simulation of complex, multi-module systems. Others offer domainspecific synthesis to hardware from languages like C/C++ or MATLAB's M, aimed at everything from accelerating software algorithms and offloading embedded processors to creating super-high-performance digital signal processing engines for algorithms that demand more than what conventional Von Neumann processors can currently deliver.

These tools are available from a variety of suppliers, ranging from FPGA vendors themselves to major EDA companies to high-energy startups banking on hitting it big based on the upcoming discontinuity in design methodology. You should be trying them out now. If not, plan on being left behind by more productive competitors over the next five years. At the same time, you should realize that today's ESL technologies are still in the formative stage. These are nascent engineering tools with a long way to go before they fulfill the ultimate promise of ESL - a productivity leap in digital design methodology that will ultimately allow us to keep pace with Moore's Law. 🕏

## WHAT'S NEW

To complement our flagship publication *Xcell Journal*, we've recently launched three new technology magazines:

- *Embedded Magazine*, focusing on the use of embedded processors in Xilinx<sup>®</sup> programmable logic devices.

- *DSP Magazine*, focusing on the high-performance capabilities of our FPGA-based reconfigurable DSPs.

- *I/O Magazine*, focusing on the wide range of serial and parallel connectivity options available in Xilinx devices.

In addition to these new magazines, we've created a family of Solution Guides, designed to provide useful information on a wide range of hot topics such as *Broadcast Engineering, Power Management*, and *Signal Integrity*. Others are planned throughout the year.

www.xilinx.com/xcell/

# Bringing Imaging to the System Level with PixelStreams

You can develop FPGAbased HDTV and machine vision systems in minutes using Celoxica's suite of ESL tools and the PixelStreams video library.

by Matt Aubury Vice President, Engineering Celoxica matt.aubury@celoxica.com

The demand for high-performance imaging systems continues to grow. In broadcast and display applications, the worldwide introduction of HDTV has driven data rates higher and created a need to enhance legacy standard definition (SD) content for new displays. Simultaneously, rapid changes in display technology include novel 3D displays and new types of emissive flat panels.

Concurrently, machine vision techniques that were once confined to manufacturing and biomedical applications are finding uses in new fields. Automotive applications include lane departure warning, drowsy driver detection, and infrared sensor fusion. Security systems currently in development can automatically track people in closed-circuit TV images and analyze their movements for certain patterns of behavior. In homes, video-enabled robots will serve as entertainment and labor-saving devices.

Xcell Journal

Cost, processing power, and time to market are critical issues for these new applications. With flexible data paths, high-performance arithmetic, and the ability to reconfigure on the fly, FPGAs are increasingly seen as the preferred solution. However, designers of reconfigurable imaging systems face some big hurdles:

- Getting access to a rich library of reusable IP blocks

- Integrating standard IP blocks with customized IP

- Integrating the imaging part of the system with analysis, control, and networking algorithms running on a CPU such as a PowerPC<sup>TM</sup> or Xilinx<sup>®</sup> MicroBlaze<sup>TM</sup> processor

In this article, I'll introduce PixelStreams from Celoxica, an open framework for video processing that has applicability in both broadcast and machine vision applications. PixelStreams leverages the expressive power of the Celoxica DK Design Suite to develop efficient and high-performance FPGAbased solutions in a fraction of the time of traditional methods.

## **Filters and Streams**

A PixelStreams application is built from a network of filters connected together by streams. Filters can generate streams (for example, a sync generator), transform streams (for example, a colorspace converter), or absorb streams (for example, video output).

Streams comprise flow control, data transport, and high-level type information. The data component in turn contains:

- An active flag (indicating that this pixel is in the current region-of-interest)

- Optional pixel data (in 1-bit, 8-bit, or signed 16-bit monochrome, 8-bit YCbCr, or RGB color)

- An optional (x, y) coordinate

- Optional video sync pulses (horizontal and vertical sync, blanking, and field information for interlaced formats)

Combining all of these components into a single entity gives you great flexibili-

ty. Filters can perform purely geometric transforms by modifying only the coordinates, or create image overlays just by modifying the pixel data.

Filters use the additional type information that a stream provides in two ways: to ensure that they are compatible with the stream they are given (for example, a sync generator cannot be attached directly to a video output because it does not contain any pixel data), and to automatically parameterize themselves. Filters are polymorphic; a single PxsConvert() filter handles colorspace conversion between each of the pixel data formats (which includes 20 different operations).

### Flow Control

Flow control is handled by a downstream "valid" flag (indicating the validity of the data component on a given clock cycle) and an upstream "halt" signal. This combination makes it easy to assemble multirate designs, with pixel rates varying (dynamically if necessary) from zero up to the clock rate. Simple filters are still easy to design. For example, a filter that modifies only the pixel components would use a utility function to copy the remaining components (valid, active, coordinates, and sync pulses) from its inputs to outputs while passing the halt signal upstream. More complex filters that need to block typically require buffering at their inputs, which is easily handled by using the generic PxsFIFO() filter.

Sophisticated designs will require filter networks in multiple clock domains. These are easy to implement using the DK Design Suite, which builds efficient and reliable channels between clock domains and sends and receives filters that convert streams to channel communications. The first domain simply declares the channel (in this case, by building a short FIFO to maximize throughput) and uses the PxsSend() filter to transmit the stream:

// domain 1

chan X with { fifolength = 16 };

PxsSend (&S0, &X);

The second domain imports the channel using extern and receives the stream from it with a PxsReceive() filter:

// domain 2 extern chan X; ... PxsReceive (&S1, &X);

## **Custom Filters**

PixelStreams comes "batteries included," with more than 140 filters, many of which can perform multiple functions. A sample of this range is shown in Table 1. Every PixelStreams filter is provided with complete source code. Creating custom filters is often just a matter of modifying one of the standard filters. New filters are accessible from either the graphical editor or from code.

- Image analysis and connected component ("blob") labeling

- Image arithmetic and blending

- Clipping and region-of-interest

- Colorspace conversion and dithering

- Coordinate transforms, scaling, and warping

- Flow control, synchronization, multiplexing, FIFOs, and cross-clock domain transport

- Convolutions, edge detection, and non-linear filtering

- Frame buffering and de-interlacing

- Color look-up-tables (LUTs)

- Grayscale morphology

- Noise generators

- Video overlays, text and cursor generators, line plotter

- Sync generators for VGA, TV, HDTV

- Video I/O

Table 1 – An overview of the provided source-level IP

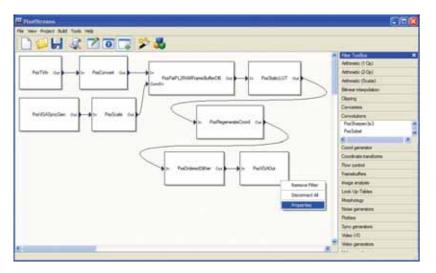

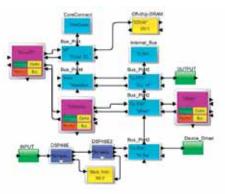

Figure 1 – Example application built using the PixelStreams graphical editor

| <pre>#define ClockRate 65000000 #include "pxs.hch" void main (void) {     /* Streams */     PXS_I_S (Stream0, PXS_RGB_U8);     PXS_I_S (Stream1, PXS_YCbCr_U8);     PXS_PV_S (Stream2, PXS_EMPTY);     PXS_PV_A (Stream3, PXS_EMPTY);     PXS_PV_A (Stream4, PXS_RGB_U8);     PXS_PV_S (Stream6, PXS_RGB_U8);     PXS_PV_S (Stream6, PXS_RGB_U8);     PXS_PV_S (Stream7, PXS_RGB_U8);     PXS_PV_S (Stream8, PXS_RGB_U8);     PXS_PV_S (Stream8, PXS_RGB_U8);     PXS_PV_S (Stream7, PXS_RGB_U8);     PXS_PV_S (Stream8, PXS_RGB_U8);     PXS_PV_S (Stream7, PXS_RGB_U8);     PXS_PV_S (Stream7, PXS_RGB_U8);     PXS_PV_S (Stream8, PXS_RGB_U8);     PXS_PV_S (Stream8, PXS_RGB_U8);     PXS_PV_S (Stream8, PXS_RGB_U8);     PXS_PV_S (Stream1, 0, 0, ClockRate);     PxsConvert (&amp;Stream1, &amp;Stream0);     PxsPalPL2RAMFrameBufferDB (&amp;Stream3, &amp;Stream4, Width, PXS_BOB, PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);     Put/O40_mm0_ended; </pre> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>#include "pxs.hch" void main (void) {     /* Streams */     PXS_I_S (Stream0, PXS_RGB_U8);     PXS_I_S (Stream1, PXS_YCbCr_U8);     PXS_PV_S (Stream2, PXS_EMPTY);     PXS_PV_A (Stream3, PXS_EMPTY);     PXS_PV_A (Stream4, PXS_RGB_U8);     PXS_PV_S (Stream6, PXS_RGB_U8);     PXS_PV_A (Stream7, PXS_RGB_U8);     PXS_PV_A (Stream7, PXS_RGB_U8);     PXS_PV_S (Stream8, PXS_RGB_U8);     PXS_PV_S (Stream8, PXS_RGB_U8);     /* Filters */     par     {         PxsTVIn (&amp;Stream1, 0, 0, ClockRate);         PxsConvert (&amp;Stream1, &amp;Stream0);         PxsPalPL2RAMFrameBufferDB (&amp;Stream0, &amp;Stream3, &amp;Stream4, Width, PXS_BOB,         PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);     } } </pre>                                                                                                                                                                                                                                 |

| <pre>void main (void) {     /* Streams */     PXS_I_S (Stream0, PXS_RGB_U8);     PXS_I_S (Stream1, PXS_YCbCr_U8);     PXS_PV_S (Stream2, PXS_EMPTY);     PXS_PV_A (Stream3, PXS_EMPTY);     PXS_PV_A (Stream4, PXS_RGB_U8);     PXS_PV_S (Stream6, PXS_RGB_U8);     PXS_PV_A (Stream7, PXS_RGB_U8);     PXS_PV_S (Stream7, PXS_RGB_U8);     PXS_PV_S (Stream8, PXS_RGB_U8);     /* Filters */     par     {         PxsTVln (&amp;Stream1, 0, 0, ClockRate);         PxsConvert (&amp;Stream1, &amp;Stream0);         PxsPalPL2RAMFrameBufferDB (&amp;Stream0, &amp;Stream3, &amp;Stream4, Width, PXS_BOB,         PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);     } } </pre>                                                                                                                                                                                                                                                                                        |

| <pre>/* Streams */ PXS_I_S (Stream0, PXS_RGB_U8); PXS_I_S (Stream1, PXS_YCbCr_U8); PXS_PV_S (Stream2, PXS_EMPTY); PXS_PV_A (Stream3, PXS_EMPTY); PXS_PV_A (Stream4, PXS_RGB_U8); PXS_PV_S (Stream6, PXS_RGB_U8); PXS_PV_S (Stream7, PXS_RGB_U8); PXS_PV_S (Stream8, PXS_RGB_U8); /* Filters */ par {     PxsTVIn (&amp;Stream1, 0, 0, ClockRate);     PxsConvert (&amp;Stream1, &amp;Stream0);     PxsPalPL2RAMFrameBufferDB (&amp;Stream0, &amp;Stream3, &amp;Stream4, Width, PXS_BOB,     PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate); }</pre>                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <pre>/* Streams */ PXS_I_S (Stream0, PXS_RGB_U8); PXS_I_S (Stream1, PXS_YCbCr_U8); PXS_PV_S (Stream2, PXS_EMPTY); PXS_PV_A (Stream3, PXS_EMPTY); PXS_PV_A (Stream4, PXS_RGB_U8); PXS_PV_S (Stream6, PXS_RGB_U8); PXS_PV_A (Stream7, PXS_RGB_U8); PXS_PV_S (Stream8, PXS_RGB_U8); /* Filters */ par {     PxsTVIn (&amp;Stream1, 0, 0, ClockRate);     PxsConvert (&amp;Stream1, &amp;Stream0);     PxsPalPL2RAMFrameBufferDB (&amp;Stream0, &amp;Stream3, &amp;Stream4, Width, PXS_BOB,     PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate); </pre>                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PXS_I_S (Stream0, PXS_RGB_U8);<br>PXS_I_S (Stream1, PXS_YCbCr_U8);<br>PXS_PV_S (Stream2, PXS_EMPTY);<br>PXS_PV_A (Stream3, PXS_EMPTY);<br>PXS_PV_A (Stream4, PXS_RGB_U8);<br>PXS_PV_S (Stream6, PXS_RGB_U8);<br>PXS_PV_A (Stream7, PXS_RGB_U8);<br>PXS_PV_S (Stream8, PXS_RGB_U8);<br>/* Filters */<br>par<br>{<br>PxsTVIn (&Stream1, 0, 0, ClockRate);<br>PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PXS_I_S (Stream1, PXS_YCbCr_U8);<br>PXS_PV_S (Stream2, PXS_EMPTY);<br>PXS_PV_A (Stream3, PXS_EMPTY);<br>PXS_PV_A (Stream4, PXS_RGB_U8);<br>PXS_PV_S (Stream6, PXS_RGB_U8);<br>PXS_PV_A (Stream7, PXS_RGB_U8);<br>PXS_PV_S (Stream8, PXS_RGB_U8);<br>/* Filters */<br>par<br>{<br>PxsTVIn (&Stream1, 0, 0, ClockRate);<br>PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PXS_I_S (Stream1, PXS_YCbCr_U8);<br>PXS_PV_S (Stream2, PXS_EMPTY);<br>PXS_PV_A (Stream3, PXS_EMPTY);<br>PXS_PV_A (Stream4, PXS_RGB_U8);<br>PXS_PV_S (Stream6, PXS_RGB_U8);<br>PXS_PV_A (Stream7, PXS_RGB_U8);<br>PXS_PV_S (Stream8, PXS_RGB_U8);<br>/* Filters */<br>par<br>{<br>PxsTVIn (&Stream1, 0, 0, ClockRate);<br>PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PXS_PV_S (Stream2, PXS_EMPTY);<br>PXS_PV_A (Stream3, PXS_EMPTY);<br>PXS_PV_A (Stream4, PXS_RGB_U8);<br>PXS_PV_S (Stream6, PXS_RGB_U8);<br>PXS_PV_A (Stream7, PXS_RGB_U8);<br>PXS_PV_S (Stream8, PXS_RGB_U8);<br>/* Filters */<br>par<br>{<br>PxsTVIn (&Stream1, 0, 0, ClockRate);<br>PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PXS_PV_A (Stream3, PXS_EMPTY);<br>PXS_PV_A (Stream4, PXS_RGB_U8);<br>PXS_PV_S (Stream6, PXS_RGB_U8);<br>PXS_PV_A (Stream7, PXS_RGB_U8);<br>PXS_PV_S (Stream8, PXS_RGB_U8);<br>/* Filters */<br>par<br>{<br>PxsTVIn (&Stream1, 0, 0, ClockRate);<br>PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PXS_PV_A (Stream4, PXS_RGB_U8);<br>PXS_PV_S (Stream6, PXS_RGB_U8);<br>PXS_PV_A (Stream7, PXS_RGB_U8);<br>PXS_PV_S (Stream8, PXS_RGB_U8);<br>/* Filters */<br>par<br>{<br>PxsTVIn (&Stream1, 0, 0, ClockRate);<br>PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PXS_PV_S (Stream6, PXS_RGB_U8);<br>PXS_PV_A (Stream7, PXS_RGB_U8);<br>PXS_PV_S (Stream8, PXS_RGB_U8);<br>/* Filters */<br>par<br>{<br>PxsTVIn (&Stream1, 0, 0, ClockRate);<br>PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PXS_PV_A (Stream7, PXS_RGB_U8);<br>PXS_PV_S (Stream8, PXS_RGB_U8);<br>/* Filters */<br>par<br>{<br>PxsTVIn (&Stream1, 0, 0, ClockRate);<br>PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PXS_PV_S (Stream8, PXS_RGB_U8);<br>/* Filters */<br>par<br>{<br>PxsTVIn (&Stream1, 0, 0, ClockRate);<br>PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| /* Filters */<br>par<br>{<br>PxsTVIn (&Stream1, 0, 0, ClockRate);<br>PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| par<br>{<br>PxsTVIn (&Stream1, 0, 0, ClockRate);<br>PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <pre>{     FxsTVIn (&amp;Stream1, 0, 0, ClockRate);     PxsConvert (&amp;Stream1, &amp;Stream0);     PxsPalPL2RAMFrameBufferDB (&amp;Stream0, &amp;Stream3, &amp;Stream4, Width, PXS_BOB,</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PxsTVIn (&Stream1, 0, 0, ClockRate);<br>PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PxsConvert (&Stream1, &Stream0);<br>PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PxsPalPL2RAMFrameBufferDB (&Stream0, &Stream3, &Stream4, Width, PXS_BOB,<br>PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PalPL2RAMCT(0), PalPL2RAMCT(1), ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PxsVGASyncGen (&Stream2, Mode);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PxsScale (&Stream2, &Stream3, 704, 576, 1024, 768);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PxsStaticLUT (&Stream4, &Stream7, PxsLUT8Square);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PxsOrderedDither (&Stream8, &Stream6, 5);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PxsVGAOut (&Stream6, 0, 0, ClockRate);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PxsRegenerateCoord (&Stream7, &Stream8);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Figure 2 – Generated source code for example application

## **Concept to FPGA Hardware in 10 Minutes**

Let's take a simple HDTV application as an example. We have an SD video stream that we want to de-interlace, upscale, apply gamma correction to, then dither and output to an LCD.

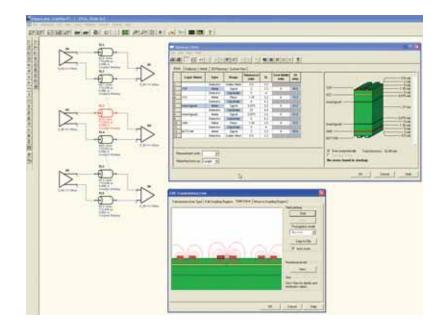

We can assemble the blocks for this very quickly using the PixelStreams graphical editor. The TV (SD) input undergoes colorspace conversion from YCbCr to RGB and is stored in a frame buffer that implements simple bob de-interlacing. Pixels are fetched from the frame buffer, with the upscaling achieved by modifying the lookup coordinates. The output stream is gamma-corrected using a color LUT, dithered, and output. Assembling this network takes only a few minutes. The editor uses heuristics to set the stream parameters automatically. The final design is shown in Figure 1.

One click generates code for this network, with a corresponding project and workspace, and launches the DK Design Suite. The generated code is shown in Figure 2. For this simple application each filter is a single process running in a parallel "par" block. More sophisticated designs will have C-based sequential code running in parallel to the filters.

One more click starts the build process for our target platform (in this case, Celoxica's Virtex<sup>TM</sup>-4 based RC340 imaging board). The build process automatically runs ISE<sup>TM</sup> software place and route and generates a bit file, taking about five minutes. One last click and the design is downloaded to the board over USB, as shown in Figure 3.

As designs become more complex, it becomes easier to code them directly rather than use the graphical editor. This enables a higher level of design abstraction, with the ability to construct reusable hierarchies of filters and add application control logic.

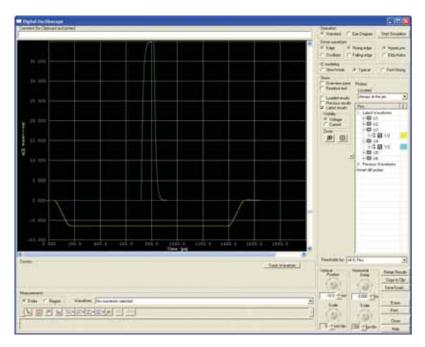

## Simulation

Simulation is handled by the DK Design Suite's built-in cycle-based simulator and utilizes its virtual platform technology to show video input and output directly on screen. Celoxica's co-simulation manager can simulate designs incorporating CPUs and external RTL components.

## Future versions of PixelStreams will extend both its flexibility as a framework and the richness of the base library of IP.

## **Synthesis**

PixelStreams capitalizes on the strengths of the DK Design Suite's built-in synthesis to achieve high-quality results on Xilinx FPGAs. For example:

- When building long pipelines, it is common that certain components of streams will not be modified. These will be efficiently packed into SRL16 components.

- When doing convolutions or coordinate transforms, MULT18 or DSP48 components will be automatically targeted (or if the coefficients are constant, efficient constant multipliers are built).

- Line buffers and FIFOs will use either distributed or pipelined block RAM resources, which are automatically tiled.

- The data components of a stream are always registered, to maximize the timing isolation between adjacent filters.

- DK's register retiming can move logic between the pipeline stages of a filter to maximize clock rate (or minimize area).

In addition, DK can generate VHDL or Verilog for use with third-party synthesis tools such as XST or Synplicity and simulation tools such as Aldec's Active HDL or Mentor Graphics's ModelSim.

## **System Integration**

A complete imaging system typically comprises:

- A PixelStreams filter network, with additional C-based control logic

- A MicroBlaze or PowerPC processor managing control, user interface, or high-level image interpretation functions

- VHDL or Verilog modules (possibly as the top level)

To deal with CPU integration, PixelStreams provides a simple "PxsBus" that can be readily bridged to CPU buses such as AMBA or OPB or controlled remotely (over PCI or USB). This is purely a control bus, allowing filters to be controlled by a CPU (for adding menus or changing filter coefficients) or to provide real-time data back from

Figure 3 – Application running in hardware

a filter to the controlling application (such as the result of blob analysis).

To support integration with RTL flows, PixelStreams offers a PxsExport() filter that packages a filter network into a module that can be instantiated from VHDL or Verilog. Alternatively, an RTL module can be instantiated within a PixelStreams top level using PxsImport(). Used together, pre-synthesized filter networks can be rapidly instantiated and reduce synthesis time.

## Conclusion

Combining the two main elements of ESL tools for Xilinx FPGAs - C- and modelbased design - PixelStreams offers a uniquely powerful framework for implementing a variety of imaging applications. The provision of a wide range of standard filters combined with features for integration into RTL flows and hardware/software co-design makes it easy to add imaging features to your system-level designs.

Future versions of PixelStreams will extend both its flexibility as a framework and the richness of the base library of IP. We plan to add additional pixel formats (such as Porter-Duff based RGBA) and color depths and increase the available performance by introducing streams that transfer multiple pixels per clock cycle. We also intend to introduce the ability to easily transmit streams over other transports, such as USB, Ethernet, and highspeed serial links, add more filters for machine vision features such as corner detection and tracking, and offer additional features for dynamically generating user interfaces.

You can use PixelStreams to target any prototyping or production board identified for a project with the addition of simple I/O filters. It can immediately target Celoxica's range of RC series platforms and is fully compatible with the ESL Starter Kit for Xilinx FPGAs. For more information, visit www.celoxica.com/xilinx, www.celoxica. com/pxs, and www.celoxica.com/rc340.

## Evaluating Hardware Acceleration Strategies Using C-to-Hardware Tools

Software-based methods enable iterative design and optimization for performance-critical applications.

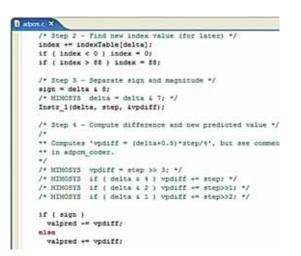

by David Pellerin CTO Impulse Accelerated Technologies, Inc. david.pellerin@impulsec.com

Scott Thibault, Ph.D. President Green Mountain Computing Systems, Inc. *thibault@gmvhdl.com*

Language-based ESL tools for FPGAs have proven themselves viable alternatives to traditional hardware design methods, bringing FPGAs within the reach of software application developers. By using softwareto-hardware compilation, software developers now have greater access to FPGAs as computational resources.

What has often been overlooked by traditional hardware designers, however, is the increased potential for design exploration, iterative performance optimization, and higher performance when ESL tools are used in combination with traditional FPGA design methods.

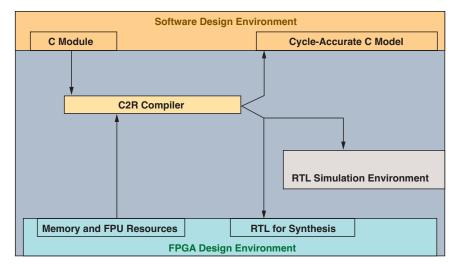

In this article, we'll describe the role of C-to-hardware ESL tools for iterative design exploration and interactive optimization. We'll present techniques for evaluating alternative implementations of C-language accelerators in Xilinx<sup>®</sup> FPGAs and explore the relative performance of fixed- and floating-point FPGA algorithms.

## **Crossing the Abstraction Gap**

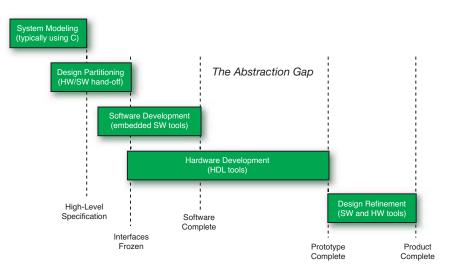

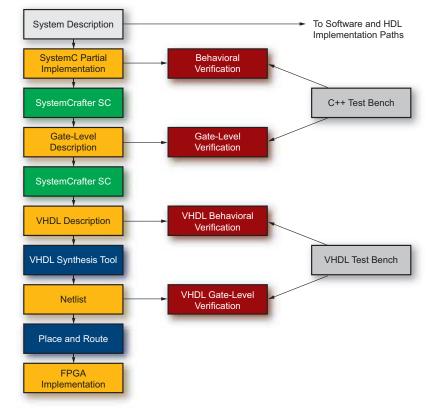

Before ESL tools for FPGAs existed, it was necessary to describe all aspects of an FPGAbased application using relatively low-level methods such as VHDL, Verilog, or even schematics. These design methods are still adequate, and in many cases preferable, for traditional FPGA-based hardware applications. However, when using traditional hardware design methods for creating complex control or computationally intense applications, a significant gap in abstraction (Figure 1) can exist between the original software algorithm and its corresponding synthesizable hardware implementation, as expressed in VHDL or Verilog. Crossing this gap may require days or weeks of tedious design conversion, making iterative design methods difficult or impossible to manage.

Tools providing C compilation and optimization for FPGAs can help software and hardware developers cross this gap by providing behavioral algorithm-level methods of design. Even for the most experienced FPGA designers, the potential exists for design improvements using such tools. Although it may seem counterintuitive to an experienced hardware engineer, using higher level tools can actually result in higher performance applications because of the dramatically increased potential for design experimentation and rapid prototyping.

## Iterative Optimization Is the Key

To understand how higher level tools can actually result in higher performance applications, let's review the role of software compilers for more traditional non-FPGA processors.

Modern software compilers (for C, C++, Java, and other languages) perform much more than simple language-to-instruction conversions. Modern processors, computing platforms, and operating systems have a diverse set of architectural characteristics, but today's compilers are built in such a way that you can (to a great extent) ignore these many architectural features. Advanced optimizing compilers take advantage of low-level processor and platform features, resulting in faster, more efficient applications.

Nonetheless, for the highest possible performance, you must still make programming decisions based on a general understanding of the target. Will threading an application help or hurt performance?

Figure 1 – Crossing the abstraction gap: in system-level design, hardware development can be the bottleneck when creating a working prototype.

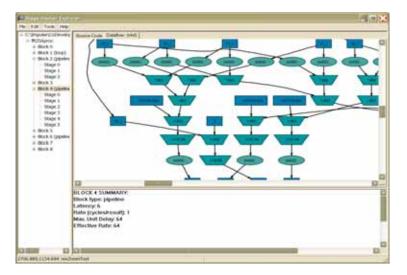

Figure 2 – A dataflow graph allows C programmers to analyze the generated hardware and perform explorative optimizations to balance trade-offs between size and speed. Illustrated in this graph is the final stage of a six-stage pipelined loop. This graph also helps C programmers understand how sequential C statements are parallelized and optimized.

Should various types of data be stored on disk, maintained in heap memory, or accessed from a local array? Is there a library function available to perform a certain I/O task, or should you write a custom driver? These questions, and others like them, are a standard and expected part of the application development process.

For embedded, real-time, and DSP application developers there are even more decisions to be made – and more dramatic performance penalties for ignoring the realities of the target hardware. For these platforms, the ability to quickly experiment with new algorithmic approaches is an important enabler. It is the primary reason that C programming has become an important part of every embedded and DSP programmer's knowledge base. Although most embedded and DSP programmers understand that higher performance is theoretically possible using assembly language, few programmers wish to use such a low level of abstraction when designing complex applications.

What does all of this mean for FPGA programmers? For software engineers considering FPGAs, it means that some understanding of the features and constraints of FPGA platforms is critical to success; it is not yet possible to simply ignore the nature of the target, nor is it practical to consider legacy application porting to be a simple recompilation of existing source code. For hardware engineers, it means that software-to-hardware tools should be viewed as complements to – not replacements for – traditional hardware development methods. For both software and hardware designers, the use of higher level tools presents more opportunities for increasing performance through experimentation and fast prototyping.

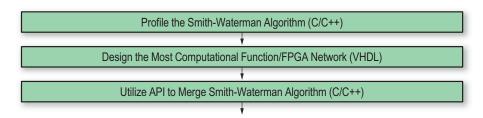

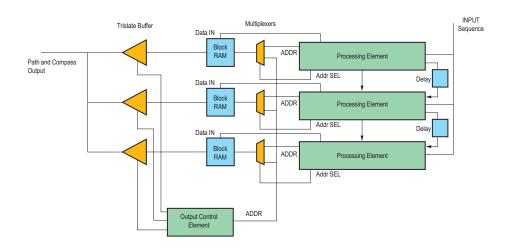

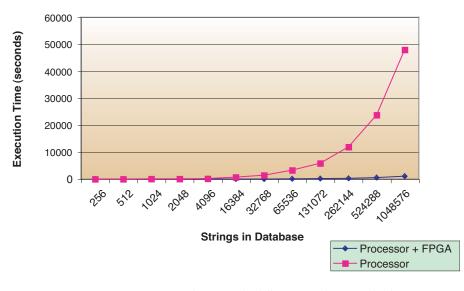

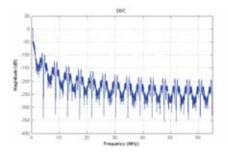

Practically speaking, the initial results of software-to-hardware compilation from C language descriptions are not likely to equal the performance of hand-coded VHDL, but the turnaround time to get those first results working may be an order of magnitude better. Performance improvements can then occur iteratively, through an analysis of how the application is being compiled to the hardware and through the experimentation that C-language programming allows.