Network infrastructures and the communications they carry are both evolving at a rapid rate. The distinctions formerly separating video, voice, and data communications are beginning to blur. At the same time, mobile and wired/broadband networks continue to merge and integrate. For service providers within the access, metro, and core spaces, these developments pose a growing challenge.

These service providers are increasingly confronting the crucial necessity to separate and control their traffic at the service, application, or user-level. With the current high bandwidth of 10 Gbps, such requirements translate into the capability of efficiently supporting QoS mechanisms in the hardware equipment at various switching points in the network. The Traffic Manager (TM) provides a fully flexible and scalable solution that can meet your QoS requirements while easily integrating within your access, metro, or core equipment.

## Xilinx Solution for Traffic Management

## The Traffic Manager offers service providers a number of unique benefits, including:

- **Reducing Development Time.** Without the need to reinvent the wheel, the TM is built as an IP core, implementing a customizable QoS engine that can directly fit into your Xilinx FPGA solution.

- **Rich Functionality.** From congestion-control mechanisms, to policing procedures, to scheduling algorithms, the TM provides a rich set of functions and algorithms across the QoS spectrum.

- Flexibility. The functionality provided by the TM is customizable through configuration

and runtime parameters. The TM can have up to five queuing stages that are modular

and capable of being configured independently. This feature is ideal for separating

and scheduling traffic at multiple dimensions.

- **Scalability.** Functions implemented by the TM are designed to scale according to the number of queues and channels in your application. Usage of FPGA resources scales accordingly and is limited to only what is required by a given TM configuration.

- **Ease of Integration.** With the support of a flexible bus interface that can support channel interleaving at any granularity level (down to the byte level), the TM easily interfaces to your existing design, regardless of your interface.

#### **Traffic Manager Key Features**

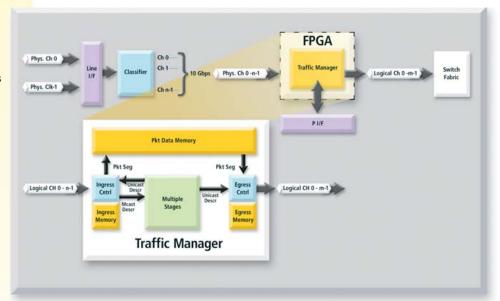

Figure 1: Traffic Manager Functional Modules

- **Scheduling.** One of the following algorithms per stage

- Strict Priority (SP)

- · Round Robin

- · Weighted Round Robin,

- · Deficit Weighted Round Robin

- Strict Priority Plus (a combination of SP and any other algorithm)

- Multigroup Scheduling. Queues can be organized into independent groups. The selected scheduling algorithm runs on each group of queues independently.

- Policing. One of the following two policing algorithms can be assumed at the entry of a stage:

- Single Rate Three Color Mode (SrTCM)

- Two Rate Three Color Mode (TrTCM)

- **Rate Control.** Traffic shaping can be implemented at the queue level by using one of the following algorithms:

- · Single token-bucket

- Dual token-bucket

- **Flow Control.** Flow control can be used to provide backpressure at the queue level in any stage.

- **Congestion Control.** One of the following algorithms can be used at the entry of a stage and at the queue level:

- · Single token-bucket

- · Dual token-bucket

- Statistics. Gathered at the queue level.

- Multicasting. Multicasting has a dedicated path and can be implemented in any stage.

- Wide range of memory support. The following memories are supported:

- · Block RAM

- · DDRII and QDRII SRAM

- · DDRII SDRAM and RLDRAM

#### **Application Example**

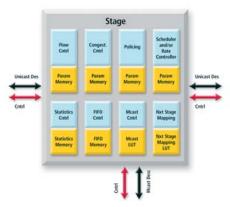

Figure 2 depicts a two-stage access application. Stage 1 handles the users' VoIP and data traffic. It uses a deficit round-robin scheduler among all queues, establishing a level of fairness among the longer data packets and the shorter VoIP packets. The second stage accepts x IPTV channels that are to be multicast to subgroups of users and consolidates the traffic of each of the n users independently. Both stages support flow control providing back-pressure per queue. The weights of WRED of the first stage, the rates of policing in the second stage, and the weights of the Weighted Round Robin scheduler in the second stage can be set according to each user's Service Level Agreement.

Figure 2: Traffic Manager in an Access Application

#### **Take the Next Step**

Please contact your local Xilinx sales representative to learn more about how the Xilinx Traffic Manager can help you manage and control traffic on your network. Or contact us on the Web at: http://www.xilinx.com/qos

# Corporate Headquarters Xilinx, Inc. 2100 Logic Drive

2100 Logic Drive San Jose, CA 95124 Tel: (408) 559-7778 Fax: (408) 559-7114 Web: www.xilinx.com

### European Headquarters

Xilinx

Citywest Business Campus

Saggart,

Co. Dublin

Ireland

Tel: +353-1-464-0311

Fax: +353-1-464-0324

Web: www.xilinx.com

#### Japan

Xilinx, K.K. Shinjuku Square Tower 18F 6-22-1 Nishi-Shinjuku Shinjuku-ku, Tokyo 163-1118, Japan Tel: 81-3-5321-7711 Fax: 81-3-5321-7765 Web: www.xilinx.co.jp

#### Asia Pacific

Xilinx Asia Pacific Pte. Ltd.

No. 3 Changi Business Park Vista, #04-01

Singapore 486051

Tel: (65) 6544-8999

Fax: (65) 6789-8886

RCB no: 20-0312557-M

Web: www.xilinx.com

Distributed By:

© 2006 Xilinx Inc. All rights reserved. The Xilinx name, logo, and Virtex-II Pro are registered trademarks; ChipScope is a trademark; and The Programmable Logic Company is a service mark of Xilinx Inc. All other trademarks are the property of their owners

Printed in the U.S.A. PN 0010934