# SDSoC Environment User Guide

**Platforms and Libraries**

UG1146 (v2016.1) May 11, 2016

## **Revision History**

The following table shows the revision history for this document.

| Date       | Version  | Revision                                            |

|------------|----------|-----------------------------------------------------|

| 05/11/2016 | 2016.1   | Updates to reflect changes to software.             |

| 12/14/2015 | 2015.4   | Add TCL APIs for hardware platform file generation. |

|            |          | Update to sample applications (template.xml).       |

| 09/30/2015 | 2015.2.1 | Add support for ZC702 standalone board.             |

|            |          | Update to ZC702 tutorial.                           |

|            |          | Update to Platform Direct I/O tutorial.             |

| 07/20/2015 | 2015.2   | First version of the document.                      |

## **Table of Contents**

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 2                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 3                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                           |

| Chapter 1: Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                           |

| Chapter 2: SDSoC Platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                           |

| Hardware Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                           |

| Software Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 9                                                                                                       |

| Metadata Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                           |

| Vivado Design Suite Project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                           |

| Library Header Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 19                                                                                                      |

| Pre-built Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 20                                                                                                      |

| Linux Boot Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 22                                                                                                      |

| Using PetaLinux to Create Linux Boot Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 24                                                                                                      |

| Standalone Boot Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 25                                                                                                      |

| Platform Sample Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 26                                                                                                      |

| FreeRTOS Configuration/Version Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 30                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                           |

| Chapter 3: C-Callable Libraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32                                                                                                        |

| Chapter 3: C-Callable Libraries Header File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                           |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 33                                                                                                      |

| Header File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 33<br>. 33                                                                                              |

| Header File<br>Static Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 33<br>. 33<br>. 36                                                                                      |

| Header File<br>Static Library<br>Creating a Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 33<br>. 33<br>. 36<br>. 37                                                                              |

| Header File<br>Static Library<br>Creating a Library<br>Testing a Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 33<br>. 33<br>. 36<br>. 37<br>. 37                                                                      |

| Header File<br>Static Library<br>Creating a Library<br>Testing a Library<br>C-Callable Library Example: Vivado FIR Compiler IP                                                                                                                                                                                                                                                                                                                                                                                                                   | . 33<br>. 33<br>. 36<br>. 37<br>. 37                                                                      |

| Header File<br>Static Library<br>Creating a Library<br>Testing a Library<br>C-Callable Library Example: Vivado FIR Compiler IP                                                                                                                                                                                                                                                                                                                                                                                                                   | . 33<br>. 33<br>. 36<br>. 37<br>. 37<br>. 37                                                              |

| Header File<br>Static Library<br>Creating a Library<br>Testing a Library<br>C-Callable Library Example: Vivado FIR Compiler IP<br>C-Callable Library Example: HDL IP                                                                                                                                                                                                                                                                                                                                                                             | . 33<br>. 33<br>. 36<br>. 37<br>. 37<br>. 37<br><b>39</b>                                                 |

| Header File<br>Static Library<br>Creating a Library<br>Testing a Library<br>C-Callable Library Example: Vivado FIR Compiler IP<br>C-Callable Library Example: HDL IP<br>C-Callable Library Example: HDL IP                                                                                                                                                                                                                                                                                                                                       | . 33<br>. 33<br>. 36<br>. 37<br>. 37<br>. 37<br>. 37<br>. 39<br>. 40                                      |

| Header File<br>Static Library<br>Creating a Library<br>Testing a Library<br>C-Callable Library Example: Vivado FIR Compiler IP<br>C-Callable Library Example: HDL IP<br>C-Callable Library Example: HDL IP<br>Chapter 4: Tutorial: Creating an SDSoC Platform<br>Example: Direct I/O in an SDSoC Platform                                                                                                                                                                                                                                        | . 33<br>. 33<br>. 36<br>. 37<br>. 37<br>. 37<br>. 37<br>. 40<br>. 49                                      |

| Header File<br>Static Library<br>Creating a Library<br>Testing a Library<br>C-Callable Library Example: Vivado FIR Compiler IP<br>C-Callable Library Example: HDL IP<br>C-Callable Library Example: HDL IP<br>Chapter 4: Tutorial: Creating an SDSoC Platform<br>Example: Direct I/O in an SDSoC Platform<br>Example: Software Control of Platform IP                                                                                                                                                                                            | . 33<br>. 33<br>. 36<br>. 37<br>. 37<br>. 37<br>. 37<br>. 40<br>. 49                                      |

| Header File<br>Static Library<br>Creating a Library<br>Testing a Library<br>C-Callable Library Example: Vivado FIR Compiler IP<br>C-Callable Library Example: HDL IP<br>C-Callable Library Example: HDL IP<br>Chapter 4: Tutorial: Creating an SDSoC Platform<br>Example: Direct I/O in an SDSoC Platform<br>Example: Software Control of Platform IP                                                                                                                                                                                            | . 33<br>. 33<br>. 36<br>. 37<br>. 37<br>. 37<br>. 37<br>. 37<br>. 40<br>. 40<br>. 55                      |

| Header File<br>Static Library<br>Creating a Library<br>Testing a Library Example: Vivado FIR Compiler IP<br>C-Callable Library Example: HDL IP<br>C-Callable Library Example: HDL IP<br>Chapter 4: Tutorial: Creating an SDSoC Platform<br>Example: Direct I/O in an SDSoC Platform<br>Example: Software Control of Platform IP<br>Example: Sharing a Platform IP AXI Port                                                                                                                                                                       | . 33<br>. 33<br>. 36<br>. 37<br>. 37<br>. 37<br>. 37<br>. 40<br>. 49<br>. 55                              |

| Header File         Static Library.         Creating a Library.         Testing a Library.         C-Callable Library Example: Vivado FIR Compiler IP.         C-Callable Library Example: HDL IP.         C-Callable Library Example: HDL IP.         Chapter 4: Tutorial: Creating an SDSoC Platform.         Example: Direct I/O in an SDSoC Platform.         Example: Software Control of Platform IP.         Example: Sharing a Platform IP AXI Port         Appendix A: Additional Resources and Legal Notices .                         | . 33<br>. 33<br>. 36<br>. 37<br>. 37<br>. 37<br>. 37<br>. 40<br>. 49<br>. 55<br><b>60</b><br>. 60         |

| Header File         Static Library         Creating a Library         Testing a Library         C-Callable Library Example: Vivado FIR Compiler IP.         C-Callable Library Example: HDL IP         Chapter 4: Tutorial: Creating an SDSoC Platform.         Example: Direct I/O in an SDSoC Platform         Example: Software Control of Platform IP.         Example: Software Control of Platform IP.         Example: Sharing a Platform IP AXI Port         Appendix A: Additional Resources and Legal Notices         Xilinx Resources | . 33<br>. 33<br>. 36<br>. 37<br>. 37<br>. 37<br>. 37<br>. 40<br>. 49<br>. 55<br><b>60</b><br>. 60<br>. 60 |

## Chapter 1

## Introduction

The SDSoC<sup>TM</sup> (Software-Defined System On Chip) environment is an Eclipse-based integrated development environment (IDE) for implementing heterogeneous embedded systems using Zynq®-7000 All Programmable SoCs and Zynq UltraScale+<sup>TM</sup> MPSoCs. The SDSoC system compiler generates an application-specific system-on-chip by compiling application code written in C/C++ into hardware and software that extends a target platform. The SDSoC environment includes platforms for application development; other platforms are provided by Xilinx partners.

An SDSoC platform defines a base hardware and software architecture and application context, including processing system, external memory interfaces, custom input/output, and software run time including operating system (possibly "bare metal"), boot loaders, drivers for platform peripherals and root file system. Every project you create within the SDSoC environment targets a specific platform, and you employ the tools within the SDSoC IDE to customize the platform with application-specific hardware accelerators and data motion networks that connect accelerators to the platform. In this way, you can easily create highly tailored application-specific systems-on-chip for different base platforms, and can reuse base platforms for many different application-specific systems-on-chip.

This document describes how to create a custom SDSoC platform starting from a hardware system built using the Vivado® Design Suite, and a software run-time environment, including operating system kernel, boot loaders, file system, and libraries.

**IMPORTANT:** For additional information on using the SDSoC environment, see the <u>SDSoC</u> Environment User Guide (UG1027).

## Chapter 2

## **SDSoC Platforms**

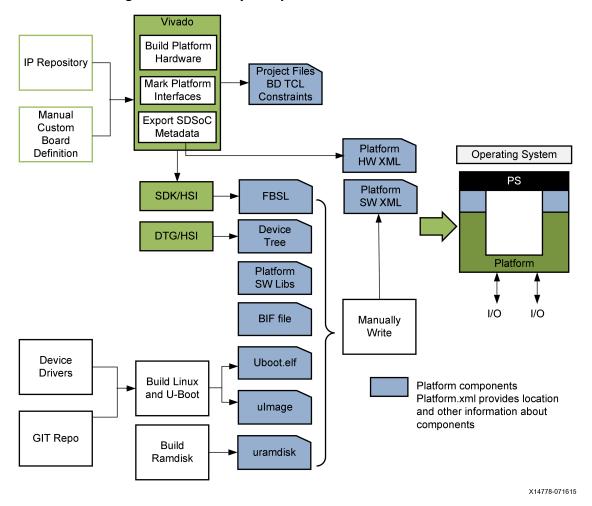

An SDSoC platform consists of a Vivado® Design Suite hardware project, a target operating system, boot files, and optionally, software libraries that can be linked with user applications that target the platform. An SDSoC platform also includes XML metadata files that describe the hardware and software interfaces used by the SDSoC compilers to target the platform.

A platform provider builds the platform hardware using the Vivado Design Suite and IP Integrator. After the hardware has been built and verified, the platform provider executes Tcl commands within the Vivado tools to specify SDSoC platform hardware interfaces and generate the SDSoC platform hardware metadata file.

The platform creator must also provide boot loaders and target operating system required to boot the platform. A platform can optionally include software libraries to be linked into applications targeting the platform using the SDSoC compilers. If a platform supports a target Linux operating system, you can build the kernel and U-boot bootloader at the command line or using the PetaLinux tool suite. You can use the PetaLinux tools, SDSoC environment or the Xilinx SDK to build platform libraries. Currently, the software platform metadata file must be created manually.

Figure 2–1: Primary Components of an SDSoC Platform

An SDSoC platform consists of the following elements:

- Metadata files

- Platform hardware description file (<platform>\_hw.pfm) generated using Vivado tools

- Platform software description file (<platform>\_sw.pfm) written by hand

- Vivado Design Suite project

- Sources

- Constraints

- IP blocks

- Software files

- Library header files (optional)

- Static libraries (optional)

- Linux related objects (device-tree, u-boot, Linux-kernel, ramdisk)

- Pre-built hardware files (optional)

- Bitstream

- Exported hardware files for SDK

- Pre-generated device registration and port information software files

- Pre-generated hardware and software interface files

X14784-070915

In general, only the platform builder can ensure that a platform is "correct" for use within the SDSoC environment. However, you can find a Platform Checklist in <sdsoc\_root>/docs/SDSoC\_platform\_checklist.xlsx, which contains an embedded platform\_dm\_test.zip archive containing a basic liveness test for every data mover used by the SDSoC system compiler. Unzip platform\_dm\_test.zip into a work area, and from within an SDSoC environment Terminal shell, execute the following.

\$ make PLATFORM=<platform\_path> axidma\_simple \$ make PLATFORM=<platform\_path> axidma\_sg \$ make PLATFORM=<platform\_path> axidma\_2d \$ make PLATFORM=<platform\_path> axififo \$ make PLATFORM=<platform\_path> zero\_copy \$ make PLATFORM=<platform\_path> xd adapter

Each of these tests should build cleanly, and should be tested on the board.

A platform should provide tests for every custom interface so that users have examples of how to access these interfaces from application C/C++ code.

### **Hardware Requirements**

This section describes requirements on the hardware design component of an SDSoC platform. In general, nearly any design targeting the Zynq®-7000 All Programmable SoC using the IP Integrator within the Vivado® Design Suite can be the basis for an SDSoC platform. The process of capturing the SDSoC hardware platform is conceptually straightforward.

- 1. Build and verify the hardware system using the Vivado Design Suite.

- 2. Load the SDSoC Vivado Tcl APIs.

- 3. Execute Tcl APIs in the Vivado Tcl Console to accomplish the following steps:

- a. Declare the hardware platform name

- b. Declare a brief platform description

- c. Declare the platform clock ports

- d. Declare the platform AXI bus interfaces

- e. Declare the platform AXI4-Stream bus interfaces

- f. Declare the available platform interrupts

- g. Generate the platform hardware description metadata file

There are several rules that the platform hardware design must observe.

- 1. The Vivado project name must match the platform name. If the Vivado project contains more than one block diagram, the block diagram used is the one that has the same name as the platform.

- 2. Every platform IP that is not part of the standard Vivado IP catalog must be local to the platform Vivado Design Suite project. References to external IP repository paths are not allowed.

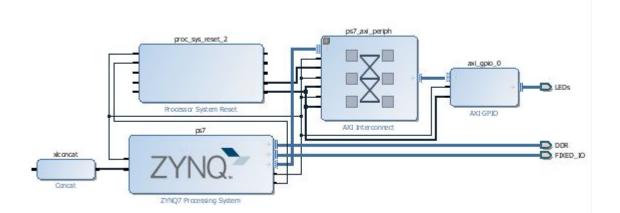

- 3. Every platform must contain a Processing System IP block from the Vivado IP catalog.

- 4. An SDSoC platform hardware port interface must be an AXI, AXI4-Stream, clock, reset, or interrupt interface only. Custom bus types or hardware interfaces must remain internal to the platform.

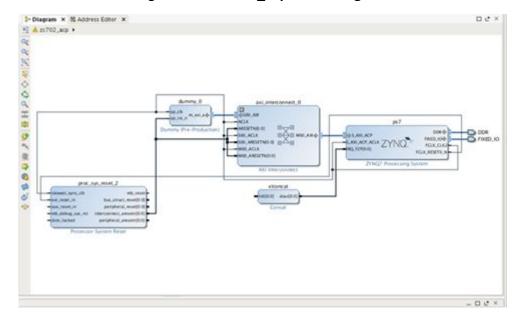

- 5. Every platform must declare at least one general purpose AXI master port from a Processing System IP or an interconnect IP connected to such an AXI master port, that will be used by the SDSoC compilers for software control of datamover and accelerator IPs.

- 6. Every platform must declare at least one AXI slave port that will be used by the SDSoC compilers to access DDR from datamover and accelerator IPs.

- 7. To share an AXI port between the SDSoC environment and platform logic (for example, S\_AXI\_ACP), you must export an unused AXI master or slave of an AXI Interconnect IP block connected to the corresponding AXI port, and the platform must use the ports with least significant indices

- 8. Every platform AXI interface will be connected to a single data motion clock by the SDSoC environment.

**NOTE:** Accelerator functions generated by the SDSoC compilers might run on a different clock that is provided by the platform.

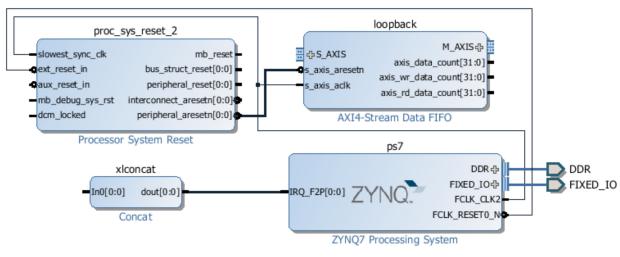

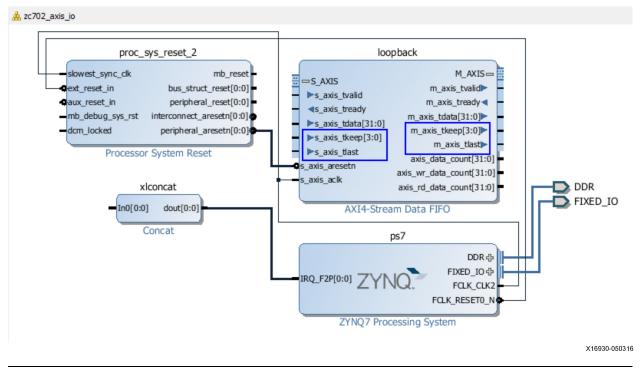

- 9. Every platform AXI4-Stream interface requires TLAST and TKEEP sideband signals to comply with the Vivado tools data mover IP used by the SDSoC environment.

- 10. Every exported platform clock must have an accompanying Processor System Reset IP block from the Vivado IP catalog.

- 11. Platform interrupt inputs must be exported by a Concat (xlconcat) block connected to the Processing System 7 IP IRQ\_F2P port. IP blocks within a platform can use some of the sixteen available fabric interrupts, but must use the least significant bits of the IRQ\_F2P port without gaps.

### **Software Requirements**

This section describes requirements for the run-time software component of an SDSoC platform.

The SDSoC environment currently supports Linux, standalone (bare metal), and FreeRTOS operating systems running on the Zynq®-7000 AP SoC target, but a platform is not required to support all of them. The SDSoC environment supports Linux and standalone (bare-metal) operating systems running on the Zynq UltraScale+™ MPSoC.

When platform peripherals require Linux kernel drivers, you must configure the kernel to include several SDSoC environment specific drivers which are available with the linux-xlnx kernel sources in the drivers/staging/apf directory. The base platforms included with the SDSoC environment provide instructions, for example, platforms/zc702/boot/how-to-build-this-linux-kernel.txt.

This linux kernel (uImage) and the associated device tree (devicetree.dtb) are based on the 4.4 version of the linux kernel. To build the kernel:

1. Clone/pull from the master branch of the Xilinx/linux-xlnx tree at github, and check out the xilinx-v2016.1 tag.

git checkout -b sdsoc\_release\_tag xilinx-v2016.1

2. Add the following CONFIGs to xilinx\_zynq\_defconfig and then configure the kernel.

```

CONFIG_STAGING=y

CONFIG_XILINX_APF=y

CONFIG_XILINX_DMA_APF=y

CONFIG_DMA_CMA=y

CONFIG_CMA_SIZE_MBYTES=256

CONFIG_CROSS_COMPILE="arm-linux-gnueabihf-"

CONFIG_LOCALVERSION="-xilinx-apf"

```

One way to do this is:

cp arch/arm/configs/xilinx\_zynq\_defconfig arch/arm/configs/tmp\_defconfig

3. Edit arch/arm/configs/tmp\_defconfig using a text editor and add the above config lines to the bottom of the file.

make ARCH=arm tmp\_defconfig

4. Build the kernel using:

make ARCH=arm UIMAGE\_LOADADDR=0x8000 uImage

By default, the SDSoC system compiler generates an SD card image for booting the platform.

For creating a standalone platform, you must first build the hardware component. After building it, run the Vivado® hardware export command to create the hardware handoff file. Using this newly generated hardware handoff file, use SDSoC IDE to create a hardware platform project. From this project, you can create a new board support project. The system.mss file, as well as the linker script can now be delivered as part of the platform. Details of this process can be found in the section Create the Standalone Platform Software

. The platform can bundle the libraries and header files in the platform using the procedure listed in the section Platform Software Description File below.

### **Metadata Files**

The SDSoC platform includes the following XML metadata files that describe the hardware and software interfaces.

- Platform hardware description file

- Platform software description file

### **Platform Hardware Description File**

A platform hardware description file <platform>\_hw.pfm is an XML metadata file that describes the hardware system to the SDSoC environment, including available clock frequencies, interrupts, and the hardware interfaces that the SDSoC environment can use to communicate with hardware functions.

As shown in the figure in SDSoC Platforms, you create this file by building a base hardware platform design using the Vivado Design Suite. Using a Vivado Tcl API, you declare the SDSoC Platform port interface and generate the SDSoC platform hardware description. The tutorials in this document provide example usages of these Vivado Tcl APIs.

### **SDSoC Vivado Tcl Commands**

This section describes the Vivado® IP Integrator Tcl commands that specify the hardware interface of an SDSoC<sup>™</sup> platform, which includes clock information and clock, reset, interrupt, AXI, and AXI4-Stream interfaces. Once you have built and verified your hardware system within the Vivado Design Suite, the process of creating an SDSoC platform hardware description file consists of the following steps.

1. Load the SDSoC Vivado Tcl API by executing the following command in the Tcl console.

source -notrace <sdsoc\_root>/scripts/vivado/sdsoc\_pfm.tcl

- 2. Execute Tcl APIs in Vivado to accomplish the following steps:

- a. Declare the hardware platform name

- b. Declare a brief platform description

- c. Declare the platform clock ports

- d. Declare the platform AXI bus interfaces

- e. Declare the platform AXI4-Stream bus interfaces

- f. Declare the available platform interrupts

- g. Generate the platform hardware description metadata file

The following describes the TCL API to be used within a block diagram.

#### Create hardware platform description

To create a new hardware pfm file, set the name and description, use:

sdsoc::create\_pfm <platform>\_hw.pfm

#### Arguments:

<platform> - platform name

#### Returns:

new platform handle

To set the platform name and description:

sdsoc::pfm\_name <platform handle> <vendor> <library> <platform> <version>

sdsoc::pfm\_description <platform handle> <Description>"

#### Example:

#### Clocks

You can export any clock source with the platform, but for each you must also export synchronized reset signals using a Processor System Reset IP block in the platform. To declare clocks, use:

sdsoc::pfm\_clock <pfm> <port> <instance> <id> <is\_default> <proc\_sys\_reset>

Arguments:

| Argument       | Description                                                                |

|----------------|----------------------------------------------------------------------------|

| pfm            | pfm handle                                                                 |

| port           | Clock port name                                                            |

| instance       | Instance name of the block that contains the port                          |

| id             | Clock id (user-defined, must be a unique non-negative integer)             |

| is_default     | True if this is the default clock, false otherwise                         |

| proc_sys_reset | Corresponding proc_sys_reset block instance for synchronized reset signals |

Every platform must declare one default clock for the SDSoC environment to use when no explicit clock has been specified. A clock is the default clock when the "is\_default" argument is set to true.

#### Examples:

| sdsoc::pfm_clock | <pre>\$pfm FCLK_CLK</pre> | 0 ps7 0 | false | proc_sys_reset_0 |

|------------------|---------------------------|---------|-------|------------------|

| sdsoc::pfm_clock | \$pfm FCLK_CLK            | 1 ps7 1 | false | proc_sys_reset_1 |

| sdsoc::pfm_clock | \$pfm FCLK_CLK            | 2 ps7 2 | true  | proc_sys_reset_2 |

| sdsoc::pfm_clock | \$pfm FCLK_CLK            | 3 ps7 3 | false | proc_sys_reset_3 |

#### AXI Ports

#### To declare AXI ports, use:

sdsoc::pfm axi port <pfm> <axi port> <instance> <memport>

#### Arguments:

| Argument | Description                                                      |  |

|----------|------------------------------------------------------------------|--|

| pfm      | pfm handle                                                       |  |

| port     | AXI port name                                                    |  |

| instance | Instance name of the block that contains the port                |  |

| memport  | Corresponding memory interface port type. Values:                |  |

|          | <ul> <li>M_AXI_GP – A general-purpose AXI master port</li> </ul> |  |

|          | • S_AXI_HP – A high-performance AXI slave port                   |  |

|          | • S_AXI_ACP – An accelerator coherent slave port                 |  |

|          | • MIG – An AXI slave connected to a MIG memory controller        |  |

#### Examples:

| <pre>sdsoc::pfm_axi_port</pre> | <pre>\$pfm M_AXI_GP0 ps7 M_AXI_GP</pre> |

|--------------------------------|-----------------------------------------|

| sdsoc::pfm_axi_port            | \$pfm M_AXI_GP1 ps7 M_AXI_GP            |

| <pre>sdsoc::pfm_axi_port</pre> | <pre>\$pfm S_AXI_ACP ps7 S_AXI_ACP</pre> |

|--------------------------------|------------------------------------------|

| sdsoc::pfm_axi_port            | <pre>\$pfm S_AXI_HP0 ps7 S_AXI_HP</pre>  |

| sdsoc::pfm_axi_port            | <pre>\$pfm S_AXI_HP1 ps7 S_AXI_HP</pre>  |

| sdsoc::pfm_axi_port            | <pre>\$pfm S_AXI_HP2 ps7 S_AXI_HP</pre>  |

| sdsoc::pfm_axi_port            | <pre>\$pfm S_AXI_HP3 ps7 S_AXI_HP</pre>  |

#### Example for an AXI interconnect:

sdsoc::pfm\_axi\_port \$pfm S01\_AXI axi\_interconnect\_0 MIG

#### AXI4-Stream Ports

#### To declare AXI4-Stream ports, use:

sdsoc::pfm\_axis\_port <pfm> <axis\_port> <instance> <type>

#### Arguments:

| Argument | Description                                       |

|----------|---------------------------------------------------|

| pfm      | pfm handle                                        |

| port     | AXI4-Stream port name                             |

| instance | Instance name of the block that contains the port |

| type     | Interface type (values: M_AXIS, S_AXIS)           |

#### Examples:

| <pre>sdsoc::pfm_axis_port</pre> | <pre>\$pfm S_AXIS axis2io S_AXIS</pre> |

|---------------------------------|----------------------------------------|

| <pre>sdsoc::pfm_axis_port</pre> | \$pfm M_AXIS io2axis M_AXIS            |

#### **Interrupt Ports**

Interrupts must be connected to the platform Processing System 7 IP block through an IP integrator Concat block (xlconcat). If any IP within the platform includes interrupts, these must occupy the least significant bits of the Concat block without gaps.

To declare interrupt ports, use:

sdsoc::pfm\_irq <pfm> <port> <instance>

#### Arguments:

| Argument | Description                                              |

|----------|----------------------------------------------------------|

| pfm      | pfm handle                                               |

| port     | irq port name                                            |

| instance | Instance name of the concat block that contains the port |

#### Example:

```

for {set i 0} {$i < 16} {incr i} {

sdsoc::pfm_irq   $pfm In$i xlconcat</pre>

```

```

}

```

#### **IO Devices**

If you use the Linux UIO framework, you must declare the devices. To declare an instance to be a Linux IO platform device, use:

sdsoc::pfm\_iodev <pfm> <port> <instance> <type>

Arguments:

| Argument | Description                                      |

|----------|--------------------------------------------------|

| pfm      | pfm handle                                       |

| port     | I/O port name                                    |

| instance | Instance name of the block that contains the UIO |

| type     | I/O device type (e.g., UIO, KIO)                 |

Example:

sdsoc::pfm iodev \$pfm S AXI axio gpio 0 uio

#### Write hardware platform description file

After using the above Tcl API commands to describe your platform, use the following to write the hardware platform description file:

sdsoc::generate\_hw\_pfm <pfm>

#### Example:

sdsoc::generate\_hw\_pfm \$pfm

This command will write the file specified in the sdsoc::create pfm command.

#### Complete Example

All platforms included in the SDSoC release include the Tcl script used to generate the corresponding hardware description file. The Tcl script is located inside the vivado directory and is called <platform> pfm.tcl.

The following is a complete example of the usage of the Tcl API to generate a ZC702 platform

```

sdsoc::pfm clock

$pfm FCLK CLK0 ps7 0 false proc sys reset 0

$pfm FCLK CLK1 ps7 1 false proc sys reset 1

sdsoc::pfm clock

sdsoc::pfm clock

$pfm FCLK CLK2 ps7 2 true proc sys reset 2

sdsoc::pfm clock

$pfm FCLK CLK3 ps7 3 false proc sys reset 3

sdsoc::pfm axi port

$pfm M AXI GP0 ps7 M AXI GP

$pfm M AXI GP1 ps7 M AXI GP

sdsoc::pfm axi port

$pfm S AXI ACP ps7 S AXI ACP

sdsoc::pfm axi port

$pfm S_AXI_HP0 ps7 S_AXI_HP

sdsoc::pfm_axi_port

$pfm S AXI HP1 ps7 S AXI HP

sdsoc::pfm axi port

sdsoc::pfm axi port

$pfm S AXI HP2 ps7 S AXI HP

sdsoc::pfm axi port

$pfm S AXI HP3 ps7 S AXI HP

for {set i 0} {$i < 16} {incr i} {

sdsoc::pfm irq

$pfm In$i xlconcat

}

sdsoc::generate hw pfm $pfm

```

### **Platform Software Description File**

As described in SDSoC Platforms, an SDSoC platform has a software component that includes operating system, boot loaders, and libraries. The platform software description file contains metadata about the software runtime needed by the SDSoC system compilers to generate application-specific systems-on-chip built upon a platform.

#### **Boot Files**

By default, the SDSoC environment creates an SD card image to boot a board into a Linux prompt or execute a standalone program.

Describe the files for Linux using the following format. If you are using a unified boot image or .ub file containing a kernel image, device tree and root file system, specify xd:linuxImage="boot/image.ub" while omitting xd:devicetree and xd:ramdisk. The optional xd:sdcard folder contains folders and files that will be added to the root of the SD card image. The optional xd:sdcardMountPath specifies the SD card mount path, which defaults to /mnt if not specified (in the example below, the PetaLinux mount path /media/card is shown).

```

<xd:bootFiles

xd:os="linux"

xd:bif="boot/linux.bif"

xd:readme="boot/generic.readme"

xd:devicetree="boot/devicetree.dtb"

xd:linuxImage="boot/uImage"

xd:ramdisk="boot/ramdisk.image.gz"

xd:sdcard="boot/sdcard"

xd:sdcard="boot/sdcard"

```

For standalone, where no OS is used, the description is:

```

<xd:bootFiles

xd:os="standalone"

xd:bif="boot/standalone.bif"

xd:readme="boot/generic.readme"

xd:sdcard="boot/sdcard"

/>

```

**NOTE:** Note that these elements refer to a Boot Image File (BIF). The BIF file must exist in the location specified.

An example platform BIF file template for a Linux target has the following contents:

```

/* linux */

the_ROM_image:

{

[bootloader]<boot/fsbl.elf>

<bitstream>

<boot/u-boot.elf>

}

```

During system generation, the SDSoC system compiler reads this template and inserts application-specific file names to generate the BIF file. This file is passed to the bootgen utility to create the boot image.

```

/* linux */

the_ROM_image:

{

[bootloader]<path_to_platform>/boot/fsbl.elf

<path_to_generated_bitstream>/<project_name>.elf.bit

<path_to_platform>/boot/u-boot.elf

}

```

An example standalone.bif file has the following contents:

```

/* standalone */

the_ROM_image:

{

[bootloader]<boot/fsbl.elf>

<bitstream>

<elf>

}

```

During system generation, the SDSoC system compiler reads this template and inserts application-specific file names to generate the BIF file. This file is passed to the bootgen utility to create the boot image.

```

/* standalone */

the_ROM_image:

{

[bootloader]<path_to_platform>/boot/fsbl.elf

<path_to_generated_bitstream_directory>/<project_name>.elf.bin

<path_to_generated_application_elf_directory>/<project_name>.elf

}

```

#### Library Files

A platform can optionally include libraries. If you describe the library files using the following format, the SDSoC environment automatically adds the appropriate include and library paths (using the -I and -L switches) when calling the compiler.

```

<xd:libraryFiles

xd:os="linux"

xd:includeDir="arm-xilinx-linux-gnueabi/include"

xd:libDir="arm-xilinx-linux-gnueabi/lib"/>

<xd:libraryFiles

xd:os="standalone"

xd:includeDir="arm-xilinx-eabi/include"

xd:libDir="arm-xilinx-eabi/lib"

xd:bspconfig="arm-xilinx-eabi/lib"

xd:bspconfig="arm-xilinx-eabi/lib"

```

#### Description

The informal schema for xd:libraryFiles is:

| <xd:libraryfiles< th=""><th></th></xd:libraryfiles<> |                                                                                            |

|------------------------------------------------------|--------------------------------------------------------------------------------------------|

| xd:os                                                | Operating system. Valid values: linux, standalone                                          |

| xd:includeDir                                        | Directory passed to compiler using -I.                                                     |

|                                                      | Separate multiple paths with a colon `:' character.                                        |

|                                                      | When sdscc/sds++ compiles source files, the include path                                   |

|                                                      | order is: (1) user paths, (2) platform paths, (3) SDSoC install paths                      |

|                                                      | and (4) Vivado HLS paths (if required).                                                    |

| xd:libDir                                            | Directory paths passed to the linker using -L.                                             |

|                                                      | Separate multiple paths with a colon $`:'$ character. Each path                            |

|                                                      | must be a directory within the platform directory, containing libraries                    |

|                                                      | that can be linked with the user application. The library path                             |

|                                                      | link order is: (1) user specified paths, (2) path to SDSoC-generated                       |

|                                                      | BSP (standalone/FreeRTOS only), (3) platform paths, (4) SDSoC install                      |

|                                                      | paths, and (5) SDSoC-generated project. Do not place standalone                            |

|                                                      | BSP library libxil.a, which sdscc/sds++ generates for a BSP configuration                  |

| xd:libName                                           | file in a directory on the xd:libDir path.<br>Library names passed to the linker using -1. |

| xu. IIDNalle                                         | Separate multiple library names with a colon ':' character.                                |

|                                                      | When specified, sdscc/sds++ automatically adds the -l option                               |

|                                                      | when linking the ELF.                                                                      |

| xd:bspconfig                                         | BSP configuration file (.mss) for standalone/FreeRTOS. When specified,                     |

|                                                      | the platform must also specify an xd:includeDir containing BSP header files.               |

|                                                      | sdscc/sds++ uses this .mss instead of generating a default BSP                             |

|                                                      | configuration file based on the both the platform and hardware                             |

|                                                      | in the PL. Consequently, the .mss file must specify                                        |

|                                                      | drivers required in SDSoC user designs, including the Xilinx                               |

|                                                      | AXI DMA driver (scatter-gather mode). See Generating                                       |

|                                                      | Basic Software Platforms (UG1138) for information about                                    |

|                                                      | BSP configuration files (.mss).                                                            |

| xd:bsprepo                                           | BSP repository folder. When specified,                                                     |

|                                                      | xd:bspconfig must also be specified. sdscc/sds++ adds this folder                          |

|                                                      | to the BSP repository search path used to create a standalone BSP.                         |

|                                                      | Refer to Generating                                                                        |

|                                                      | Basic Software Platforms (UG1138) for information                                          |

| />                                                   | about BSP repositories.                                                                    |

| 1/                                                   |                                                                                            |

#### Pre-Built Hardware Files

A platform can optionally include pre-built hardware files, which the SDSoC environment clones into a project when an application has no hardware functions, rather than rebuilding the bitstream and boot image. This provides fast compilation to run an application software on the target. When a platform provides pre-built hardware files, you can force the bitstream compile using the sdscc-rebuild-hardware option to force the creation of hardware files.

The example below describes pre-built hardware included in the ZC702 platform:

```

<xd:hardware

xd:system="prebuilt"

xd:bitstream="prebuilt/bitstream.bit"

xd:export="prebuilt/export"

xd:hwcf="prebuilt/hwcf"

xd:swcf="prebuilt/swcf"/>

```

#### Description

The informal schema for xd:hardware is:

| <xd:hardware< th=""><th></th></xd:hardware<> |                                                                                               |

|----------------------------------------------|-----------------------------------------------------------------------------------------------|

| xd:system                                    | Identifier associated with predefined hardware; when                                          |

|                                              | the SDSoC environment searches for a pre-built bitstream, it looks for the keyword "prebuilt" |

| xd:bitstream                                 | Path to the bitstream.bit file for the pre-built hardware                                     |

| xd:export                                    | Path to the folder containing SDK-compatible files                                            |

|                                              | created using the Vivado tools export hardware command.                                       |

|                                              | This folder contains the hardware handoff file <platform>.hdf,</platform>                     |

|                                              | for example, zc702.hdf.                                                                       |

| xd:hwcf                                      | Path to the folder containing hardware system                                                 |

|                                              | information files. Files found in this folder                                                 |

|                                              | are partitions.xml and apsys 0.xml.                                                           |

| xd:swcf                                      | Path to the folder containing device registration and                                         |

|                                              | port information files. Files found in this folder                                            |

|                                              | are devreg.c, devreg.h, portinfo.c and portinfo.h.                                            |

| />                                           | -                                                                                             |

The pre-built platform files can be created using the SDSoC system compiler by building a "Hello world" program.

Examples are provided for every base platform in

<sdsoc install directory>/platforms/\*/hardware/prebuilt.

#### **Testing the Platform Hardware Description File**

The SDSoC Environment includes an XML Schema for validating your platform hardware description file. For example, to validate your platform hardware description XML file in an SDSoC terminal, use this command:

```

sds-pf-check <platform>_hw.pfm

```

After putting the hardware platform description file (<platform>\_hw.pfm) and software platform description file (<platform>\_sw.pfm) in the platform directory, you can verify that the SDSoC environment can read the files correctly by executing the following command, which lists all the available platforms. If you see the platform you have created in the displayed list, then the SDSoC environment has found it.

```

> sdscc -sds-pf-list

```

To display more information about your platform, use this command:

> sdscc -sds-pf-info <platform\_name>

### **Vivado Design Suite Project**

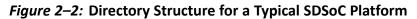

The SDSoC<sup>™</sup> environment uses the Vivado® Design Suite project in the <platform>/vivado directory as a starting point to build an application-specific SoC. The project must include an IP Integrator block diagram and can contain any number of source files. Although nearly any project targeting a Zynq SoC can be the basis for an SDSoC environment project, there are a few constraints described in Hardware Requirements.

File name and location: platforms/<platform>/vivado/<platform>.xpr

Example: platforms/zc702/vivado/zc702.xpr

**NOTE:** You must place the complete project in the same directory as the xpr file.

**IMPORTANT:** You cannot simply copy the files in a Vivado tools project; the Vivado tools manage internal states in a way that might not be preserved through a simple file copy. To make a project clonable, use the Vivado command **File > Archive Project** to create a zip archive. Unzip this archive file into the SDSoC platform directory where the hardware platform resides.

The Vivado tools require **Upgrade IP** for every new version of the Vivado Design Suite. To migrate an SDSoC hardware platform, open the project in the new version of the tools, and then upgrade all IP. Archive the project and then unzip this archive into the SDSoC platform hardware project.

If you encounter IP Locked errors when the SDSoC environment invokes the Vivado tools, it is a result of failing to make the platform clonable.

### **Library Header Files**

If the platform requires application code to #include platform-specific header files, these should reside in a subdirectory of the platform directory pointed to by the xd:includeDir attribute for the corresponding OS in the platform software description file.

For a given xd:includeDir="<relative\_include\_path>" in a platform software description file, the location is:

<platform root directory>/<relative include path>

Example:

For xd:includeDir="arm-xilinx-linux-gnueabi/include":

<sdsoc\_root>/samples/platforms/zc702\_axis\_io/arm-xilinx-linux-gnueabi/include/zc702\_axis\_io.h

To use the header file in application code, use the following line:

#include "zc702\_axis\_io.h"

Use the colon (:) character to separate multiple include paths. For example

xd:includeDir="<relative\_include\_path1>:<relative\_include\_path2>"

in a platform software description file defines a list of two include paths

```

<platform_root_directory>/<relative_include_path1>

<platform_root_directory>/<relative_include_path2>

```

**RECOMMENDED:** If header files are not put in the standard area, users need to point to them using the -I switch in the SDSoC environment compile command. We recommend putting the files in the standard location as described in the platform XML file.

### **Static Libraries**

If the platform requires users to link against static libraries provided in the platform, these should reside in a subdirectory of the platform directory pointed to by the xd:libDir attribute for the corresponding OS in the platform software description file.

For a given xd:libDir="<relative\_lib\_path>" in a platform software description file, the location is:

<platform\_root>/<relative\_lib\_path>

#### Example:

```

For xd:libDir="arm-xilinx-linux-gnueabi/lib":

```

<sdsoc\_root>/samples/platforms/zc702\_axis\_io/arm-xilinx-linux-gnueabi/lib/libzc702\_axis\_io.a

To use the library file, use the following linker switch:

```

-lzc702_axis_io

```

Use the colon : character to separate multiple library paths. For example,

```

xd:libDir="<relative_lib_path1>:<relative_lib_path2>"

```

in a platform software description defines a list of two library paths

```

<platform_root>/<relative_lib_path1>

<platform root>/<relative_lib_path2>

```

**RECOMMENDED:** If static libraries are not put in the standard area, every application needs to point to them using the -L option to the *sdscc* link command. Xilinx recommend putting the files in the standard location as described in the platform software description file.

### **Pre-built Hardware**

A platform can optionally include pre-built configurations to be used directly when you do not specify any hardware functions in an application. In this case, you do not need to wait for a hardware compile of the platform itself to create a bitstream and other required files.

The pre-built hardware should reside in a subdirectory of the platform directory. Data in the subdirectory is pointed to by the xd:bitstream, xd:export, xd:hwcf, and xd:swcf attributes for the corresponding pre-built hardware.

For a given xd:bitsteam="<relative\_lib\_path>/bitstream.bit" in a platform xml,

the location is:

platforms/<platform>/<relative\_lib\_path>/bitstream.bit

- For a given xd:export="<relative\_export\_path>" in a platform xml, the location is:

platforms/<platform>/<relative\_export\_path>

- For a given xd:hwcf="<relative\_hwcf\_path>" in a platform xml, the location is:

platforms/<platform>/<relative\_hwcf\_path>

For a given xd:swcf="<relative\_swcf\_path>" in a platform xml, the location is:

platforms/<platform>/<relative swcf path>

Example:

For xd:bitstream="prebuilt/bitstream.bit":

platforms/zc702/hardware/prebuilt/bitstream.bit

For xd:export="prebuilt/export":

platforms/zc702/hardware/prebuilt/export

contains zc702.hdf

For xd:hwcf="prebuilt/hwcf":

platforms/zc702/hardware/prebuilt/hwcf

containing partitions.xml and apsys 0.xml.

For xd:swcf="prebuilt/swcf":

platforms/zc702/hardware/prebuilt/swcf

containing devreg.c, devreg.h, portinfo.c and portinfo.h.

Pre-built hardware files are automatically used by the SDSoC environment when an application has no hardware functions using the usual flag:

-sds-pf zc702

To force a full Vivado tools bitstream and SD card image compile, use the following sdscc option:

-rebuild-hardware

Files used to populate the platforms/<platform>/hardware/prebuilt folder are found in the \_sds folder after creating the application ELF and bitstream.

bitstream.bit

File found in sds/p0/ipi/<platform>.runs/impl 1/bitstream.bit

export

Files found in \_sds/p0/ipi/<platform>.sdk (<platform>.hdf)

hwcf

Files found in \_sds/.llvm (partitions.xml, apsys\_0.xml)

swcf

Files found in \_sds/swstubs (devreg.c, devreg.h, portinfo.c, portinfo.h)

### **Linux Boot Files**

The SDSoC<sup>™</sup> environment can create an SD card image to boot the Linux operating system on the board. After booting completes, a Linux prompt is available for executing the compiled applications. For this, the SDSoC environment requires several objects as part of the platform including:

- First Stage Boot Loader (FSBL)

- U-Boot

- Device Tree

- Linux Image

- Ramdisk Image

The SDSoC environment uses the Xilinx® bootgen utility program to combine the necessary files with the bitstream into a BOOT.BIN file in a folder called sd\_card. The end-user copies the contents of this folder into the root of an SD card to boot the platform.

**IMPORTANT:** For detailed instructions on how to build the boot files, refer to the Xilinx Wiki at <u>http://wiki.xilinx.com</u>.

### First Stage Boot Loader (FSBL)

The first stage boot loader is responsible for loading the bitstream and configuring the Zynq® architecture Processing System (PS) at boot time.

When the platform project is open in Vivado® Design Suite, click the **File > Export > Export Hardware** menu option. Create a new software project **File > New > Application Project** with name fsbl as you would using the Xilinx SDK. Using the exported Hardware Platform, select the Zynq FSBL application from the list. This creates an FSBL executable.

For more detailed information, see the SDK Help System.

Once you generate the FSBL, you must copy it into a standard location for the SDSoC environment flow.

For the SDSoC system compiler to use an FSBL, a BIF file must point to it (see Boot Files). The file must reside in the <platform root>/boot/fsbl.elf folder.

```

/* linux */

the_ROM_image:

{

[bootloader]<boot/fsbl.elf>

<bitstream>

<boot/u-boot.elf>

}

```

#### Example:

```

samples/platforms/zc702_axis_io/boot/fsbl.elf

```

### U-Boot

Das U-Boot is an open source boot loader. Follow the instructions at <u>wiki.xilinx.com</u> to download U-Boot and configure it for your platform.

For the SDSoC environment to use a U-Boot, a BIF file must point to it (see Boot Files). The file must reside in the <platform root>/boot/fsbl.elf folder.

```

/* linux */

the_ROM_image:

{

[bootloader]<boot/fsbl.elf>

<bitstream>

<boot/u-boot.elf>

}

```

Example: samples/platforms/zc702\_axis\_io/boot/u-boot.elf

### **Device Tree**

The Device Tree is a data structure for describing hardware so that the details do not have to be hard coded in the operating system. This data structure is passed to the operating system at boot time. Use Xilinx SDK to generate the device tree for the platform. Follow the device-tree related instructions at <u>wiki,xilinx.com</u> to download the device tree generator support files, and install them for use with Xilinx SDK. There is one device tree per platform.

The file name and location are defined in the platform xml. Use the xd:devicetree attribute in an xd:bootFiles element. If you are using a unified boot image (.ub file) containing the kernel, devicetree and root file system, do not define the xd:devicetree attribute.

Sample xml description:

```

xd:devicetree="boot/devicetree.dtb"

```

Location: samples/platforms/zc702\_axis\_io/boot/devicetree.dtb

**NOTE:** When a platform exports a clock sourced by a processing\_system7 FCLK\_CLK port, you must modify the standard PetaLinux-generated device tree to enable the clock at boot time, in order to support hardware debugging with the Vivado Internal Logic Analyzer IP core. Use the following command to modify the device tree for your platform to enable the clocks.

fclk-enable = <0xf>;

### Linux Image

A Linux image is required to boot. Xilinx provides single platform-independent pre-built Linux image that works with all the SDSoC platforms supplied by Xilinx.

However, if you want to configure Linux for your own platform, follow the instructions at <u>wiki.xilinx.com</u> to download and build the Linux kernel. Make sure to enable the SDSoC environment APF drivers and the Contiguous Memory Allocator (CMA) when configuring Linux for your platform. Linux kernel build instructions for SDSoC platforms are described in <sdsoc\_root>/<platform>/boot/how-to-build-this-linux-kernel.txt.

The file name and location are defined in the platform xml. Use the xd:linuxImage attribute in an xd:bootFiles element. If you are using a unified boot image (.ub file) containing the kernel, device tree and root file system, define the xd:linuxImage attribute and specify the location of the .ub file, for example xd:linuxImage="boot/image.ub".

#### Sample xml description:

xd:linuxImage="boot/uImage"

Location: samples/platforms/zc702\_axis\_io/boot/uImage

### Ramdisk Image

A ramdisk image is required to boot. A single ramdisk image is included as part of the SDSoC environment install. If you need to modify it or create a new ramdisk, follow the instructions at wiki.xilinx.com.

The file name and location are defined in the platform xml. Use the xd:ramdisk attribute in an xd:bootFiles element. If you are using a unified boot image (.ub file) containing the kernel, device tree and root file system, do not define the xd:ramdisk attribute.

#### Sample xml description:

```

xd:ramdisk="boot/uramdisk.image.gz"

```

Location: samples/platforms/zc702\_axis\_io/boot/uramdisk.image.gz

### **Using PetaLinux to Create Linux Boot Files**

It is possible to generate all the Linux boot files using PetaLinux as shown in <u>PetaLinux Tools</u> <u>Documentation: Workflow Tutorial (UG1156)</u>. The overall workflow while using PetaLinux is the same, but there are a few additional steps for generating Linux boot files for use with the SDSoC environment. Because of this, we have provided a BSP for ZC702 that is configured for use with the SDSoC environment.

If your platform clock sources include an FCLK\_CLK port from a processing\_system7 IP block, you must modify the device tree as described in Device Tree

To build a PetaLinux image for ZC702 that can be used with the SDSoC environment, follow these steps.

1. Create a new PetaLinux project using the supplied BSP.

\$ petalinux-create -t project /path/to/Xilinx-ZC702-SDSoC-2016.1.bsp

- 2. Build the project.

- \$ petalinux-build

- 3. Wrap the generated kernel and rootfs with a U-Boot header.

\$ petalinux-package --image -c kernel --format uImage

4. Rename device tree BLOB and ramdisk.

\$ mv images/linux/system.dtb images/linux/devicetree.dtb

\$ mv images/linux/urootfs.cpio.gz images/linux/uramdisk.image.gz

5. The final output products are located under ./images/linux and are ready to be copied to an SD card.

The ZC702 BSP was derived from the default BSP provided with PetaLinux by making the following changes.

- 1. Run petalinux-config -c kernel to launch the menuconfig system.

- a. Select Kernel Features > Contiguous Memory Allocator [ON].

- b. Select **Device Drivers > Generic Driver Options > DMA Contiguous Memory Allocator [ON]**.

- c. Select Device Drivers > Generic Driver Options > Size in Mega Bytes [256].

- d. Select Device Drivers > Staging drivers [ON] > Xilinx APF Accelerator driver [ON] > Xilinx APF DMA engines support [ON].

- 2. Open the

<project-root>/subsystems/linux/configs/device-tree/system-top.dts file and append the following lines of code:

```

&clkc {

fclk-enable = <0xf>;

};

/ {

xlnk {

compatible = "xlnx,xlnk-1.0";

clock-names = "xclk0", "xclk1", "xclk2", "xclk3";

clocks = <&clkc 15>, <&clkc 16>, <&clkc 17>, <&clkc 18>;

};

};

```

- 3. Run petalinux-config -c rootfs, to launch the menuconfig system

- 4. Select Filesystem Packages.

- 5. Select **base**.

- a. Select external-xilinx-toolchain > libstdc++6

- b. Select tcf-agent > tcf-agent

- 6. Run the petalinux-build command, which builds the project and generates the file named image.ub inside the <project-root>/images/linux folder, which has the kernel, device tree, and file system packaged inside.

### **Standalone Boot Files**

If no OS is required, the end-user can create a boot image that automatically executes the generated executable.

### First Stage Boot Loader (FSBL)

The first stage boot loader is responsible for loading the bitstream and configuring the Zynq® architecture Processing System (PS) at boot time.

When the platform project is open in Vivado® Design Suite, click the **File > Export > Export Hardware** menu option. Create a new software project **File > New > Application Project** with name fsbl as you would using the Xilinx SDK. Using the exported Hardware Platform, select the Zynq FSBL application from the list. This creates an FSBL executable.

For more detailed information, see the SDK Help System.

Once you generate the FSBL, you must copy it into a standard location for the SDSoC environment flow.

For the SDSoC system compiler to use an FSBL, a BIF file must point to it (see Boot Files). The file must reside in the <platform\_root>/boot/fsbl.elf folder.

```

/* linux */

the_ROM_image:

{

[bootloader]<boot/fsbl.elf>

<boot/u-boot.elf>

}

```

#### Example:

samples/platforms/zc702\_axis\_io/boot/fsbl.elf

### Executable

For the SDSoC environment to use an executable in a boot image, a BIF file must point to it (see Boot Files).

```

/* standalone */

the_ROM_image:

{

[bootloader]<boot/fsbl.elf>

<bitstream>

<elf>

}

```

The SDSoC environment automatically inserts the generated bitstream and ELF files.

### **Platform Sample Applications**

A platform can optionally include sample application templates to demonstrate the usage of the platform.

Sample applications must reside in the samples directory of a platform. The file that describes the applications to SDSoC is called template.xml and it resides inside the samples directory.

The template.xml file uses a very simple format. Here is an example for the zc702\_led sample platform.

```

<?xml version="1.0" encoding="UTF-8"?>

<manifest:Manifest xmi:version="2.0"

xmlns:xmi="http://www.omg.org/XMI"

xmlns:manifest="http://www.xilinx.com/manifest">

<template location="arraycopy" name="Array copy"

description="Simple test application">

<supports>

<and>

<os name="Linux"/>

</and>

</supports>

<accelerator name="arraycopy" location="arraycopy.cpp"/>

</template>

<template location="arraycopy sa" name="Array copy"

description="Simple test application">

<supports>

<and>

<os name="Standalone"/>

</and>

</supports>

<accelerator name="arraycopy" location="arraycopy.cpp"/>

</template>

</manifest:Manifest>

```

The first line defines the format of the file to be xml and is mandatory:

<?xml version="1.0" encoding="UTF-8"?>

A <manifest:Manifest> xml element is required as a container for all application templates:

#### **Template Element**

A <template> element can have multipe attributes:

| Attribute   | Description                                                |  |

|-------------|------------------------------------------------------------|--|

| location    | Relative path to the template application                  |  |

| name        | Application name displayed in the SDSoC environment        |  |

| description | Application description displayed in the SDSoC environment |  |

#### Example:

<template location="myapp" name="My App" description="Sample application">

The <template> element can have multiple other xml sub-elements:

| Element      | Description                                                                    |  |

|--------------|--------------------------------------------------------------------------------|--|

| supports     | Boolean function that defines the matching template                            |  |

| includepaths | Paths relative to the application to be added to the compiler as $-I$ flags    |  |

| librarypaths | Paths relative to the application to be added to the linker as $-L$ flags      |  |

| libraries    | Platform libraries to be linked against using linker -1 flags                  |  |

| exclude      | Directories or files to exclude from copying into the SDSoC project            |  |

| system       | Application project settings for the system, for example the data motion clock |  |