Embedded Systems Software Design Lab Workbook

embd-sw-2016.3-wkb-lab-rev1

# **Embedded Systems Software Design Lab Workbook 2016.3**

© Copyright 2016 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, UltraScale, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. Cortex is a registered trademark of ARM in the EU and other countries. All other trademarks are the property of their respective owners.

#### DISCLAIMER

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort. including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: http://www.xilinx.com/warranty.htm#critapps. All other trademarks are the property of their respective owners.

# Lab FAQ

- Where can I get the files for the labs?

- www.xilinx.com/training/downloads.htm

- These are original files and do not contain any work that you may have performed.

- Labs were developed using version 2016.3 of the tools. Later versions may work and will likely require you to update various pieces of IP. See the "Updating IP" topic in the Lab Reference Guide for instructions on how to update IP (Vivado Design Suite Operations > Vivado IP Integrator Operations > Updating IP).

- What if I cannot answer a question in the lab?

- Do your best! The questions are meant to stimulate thought, not to test your knowledge. After you have pondered a question you can find the answer at the end of each lab.

- Where can I get more detailed information on a topic?

- The Lab Reference Guide is a collection of "how to" topics for commonly performed tasks categorized by tool (Vivado Design Suite, Vivado Analyzer, SDK, etc.) and subdivided into major areas within the tool.

- The *Lab Reference Guide* is available from the lab files download as well as from www.xilinx.com/training/downloads.htm.

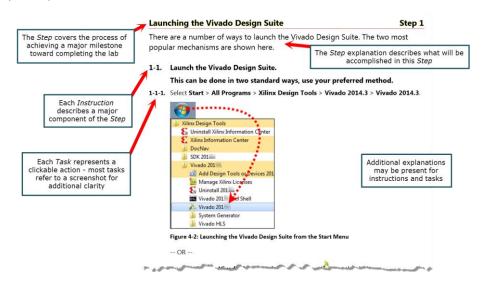

- How do the instructions work?

- The instructions are provided in layers:

- Steps these are the major/broadest aspects of solving the problem that the lab poses (X).

- Instructions these represent the significant instructions towards solving the issue outlined by the step (X-X).

- Tasks these are the finest granularity items that (when combined with the other tasks) solve the instruction they are subordinate to. Every task is a "clickable" event (X-X-X).

# **Table of Contents**

| Lab 1:  | Exploring the Architecture of the Zynq-7000 All Programmable SoC | 3   |

|---------|------------------------------------------------------------------|-----|

| Lab 2:  | Exploring the Architecture of the MicroBlaze Processor           | 17  |

| Lab 3:  | Driving the SDK Tool                                             | 39  |

| Lab 4:  | System Debugger                                                  | 66  |

| Lab 5:  | Application Development                                          | 97  |

| Lab 6:  | File Systems                                                     | 123 |

| Lab 7:  | Linker Script                                                    | 145 |

| Lab 8:  | Software Interrupts                                              | 175 |

| Lab 9:  | Linux Application Development                                    | 197 |

| Lab 10: | Boot Loading from Flash Memory                                   | 219 |

| Lab 11: | SDK Tool Profiling                                               | 243 |

| Lab 12: | Writing a Device Driver                                          | 278 |

# Lab 1: Exploring the Architecture of the Zynq-7000 All Programmable SoC

2016.3

# **Abstract**

This introduction to the basic process of instantiating and customizing the processor system (PS) of the Zynq®-7000 All Programmable SoC family of parts illustrates the process of customizing the PS. While not every aspect of customization is covered, the processes provided here can be extended to all aspects of customization.

# **Objectives**

After completing this lab, you will be able to:

- Instantiate a processor system

- Customize a processor system

- Run the Block Automation tool for a processor system

# Introduction

This lab introduces you to the basic process of managing the processing system block in the Zynq-7000 All Programmable SoC family of devices. Included in management is the instantiation of the PS, re-customization, and finally running the Block Automation tool.

The PS is a complex subsystem and an exhaustive investigation of every aspect of this subsystem is beyond the scope of this lab. Only some of the more popular customization are illustrated here with the hope that you will gain familiarity with how these options are organized and that you can quickly find whatever aspect of customization you desire to modify.

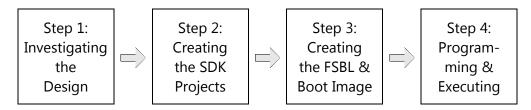

# **General Flow**

Getting Started Step 1

As this is a hardware lab focusing on how the Cortex-A9 processor of the Zynq-7000 AP SoC can be configured, all your work will be done with the Vivado Design Suite IP integrator (IPI).

You will begin by launching the Vivado Design Suite, then loading a helper Tcl script to properly configure the project and quickly get you to the IPI tool. If you need to refresh your memory regarding the details of project creation or the mechanics of using the IPI tool, refer to the "Driving the IPI Tool" topic cluster.

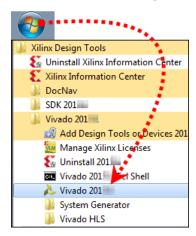

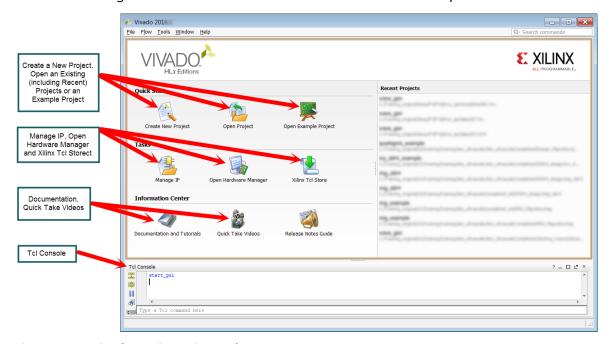

There are a number of ways to launch the Vivado Design Suite. The two most popular mechanisms are shown here.

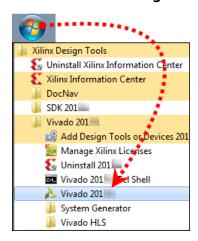

# 1-1. Launch the Vivado Design Suite.

This can be done in two standard ways, use your preferred method.

1-1-1. Select Start > All Programs > Xilinx Design Tools > Vivado 2016.3 > Vivado 2016.3.

Figure 1-1: Launching the Vivado Design Suite from the Start Menu

-- OR --

Double-click the **Vivado Design Suite** shortcut icon ( on the desktop.

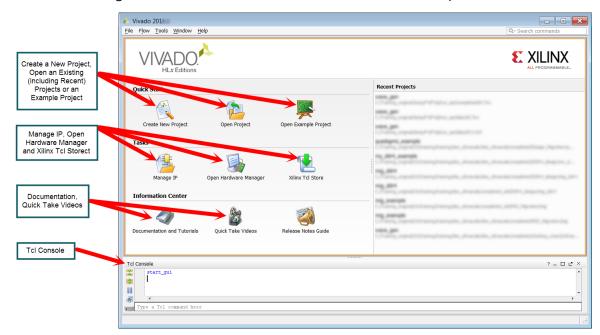

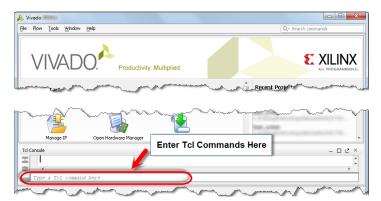

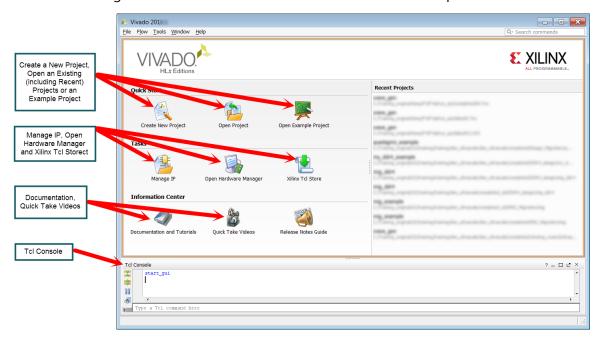

The Vivado Design Suite opens to the Welcome window. From the Welcome window you can create a new project, open an existing project, or enter Tcl commands directly into the Vivado Design Suite as well as access documentation and examples.

Figure 1-2: Vivado Design Suite Welcome Screen

With the Vivado Design Suite now open, you will load a helper Tcl script and run it to configure the project and get you to the important part of this lab—working with the processor.

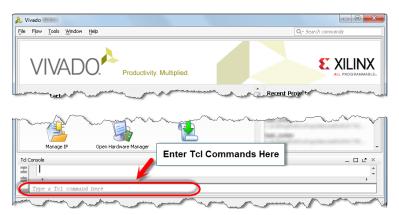

The Vivado Design Suite offers both GUI and scripted control. Scripted control takes the form of Tcl commands. These Tcl commands can be entered directly into the tool one at a time, or an entire Tcl script can be loaded and executed.

# 1-2. Run a Tcl script.

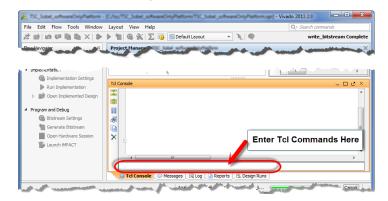

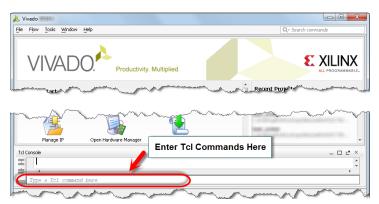

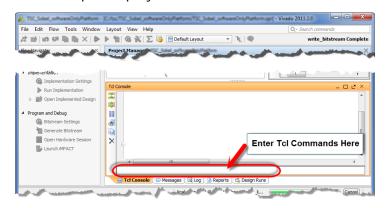

# **1-2-1.** Locate the Tcl command line entry.

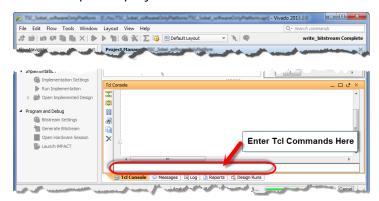

The command line entry can be found either on the Welcome page prior to a project being opened, or once a project has been opened.

From the Welcome screen:

Figure 1-3: Accessing the Tcl Console from the Getting Started Page

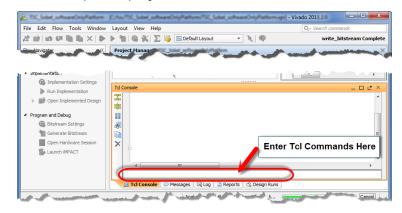

From an opened project:

Figure 1-4: Entering Commands into the Tcl Console from an Open Project

The default directory for the Tcl environment is nested within the Xilinx installation directory. This placement, however, is often disadvantageous. In most cases, you will want to navigate to a more useful path. To do this, use the cd command to change directory to the user directory.

**1-2-2.** Change the current working directory to where the Tcl script is located by entering:

# cd C:\training\ArchZynq7000 Overview\support

Remember that the Tcl environment is based on Linux and requires the '/' character to delimit hierarchical paths.

**1-2-3.** Verify that you are now where you want to be by entering the following into the Tcl command line:

#### pwd

The current working directory is displayed. If you are not where you want to be, use the cd command to change to C:\training\ArchZynq7000 Overview\support.

**1-2-4.** Enter the following Tcl command:

# source exploreZynq7000 completer.tcl

The Tcl script is run as though you typed each command included in the Tcl script into the Tcl command line. You can follow the execution of the script and monitor for any errors or warnings in the Tcl Console.

With the Tcl script now loaded, you will run the *createProject* and *createBlockDesign* procs to build the Vivado Design Suite project and create an appropriately named block design in which you will perform the remainder of this lab.

# 1-3. Run the *createProject* and *createBlockDesign* procs.

- **1-3-1.** Enter the following into the Tcl command line to create the Vivado Design Suite project: createProject

- **1-3-2.** Enter the following into the Tcl command line to create the block design in which you will build your processor system:

createBlockDesign "Zyng7KembdDsgn"

# Adding and Customizing the Zynq-7000 AP SoC Processor

Step 2

With the block diagram canvas open, you will now add and customize a Zynq-7000 AP SoC processor.

# 2-1. Add a ZYNQ7 Processing System to the IP Integrator canvas.

If you do not recall how to perform this task, refer to the "Adding a Processor to the Block Design" section under IP Integrator Operations in the *Lab Reference Guide*.

Remember that adding a processor IP is just like adding any other type of IP to the canvas. You can also review the "Driving the IPI Tool" topic cluster for a guided example.

| Question 1                                                                                          |

|-----------------------------------------------------------------------------------------------------|

| What information does the wizard provide?                                                           |

|                                                                                                     |

|                                                                                                     |

| Question 2                                                                                          |

| How does configuring the PS of the Zynq-7000 AP SoC differ from configuring a MicroBlaze processor? |

|                                                                                                     |

|                                                                                                     |

The Zynq All Programmable PS contains a large number of customizable features. The following instructions will illustrate how to access various sections of the Zynq All Programmable PS, not necessarily indicating which settings to configure.

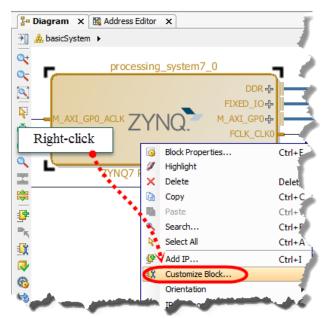

# 2-2. Access the Re-customization dialog box.

# 2-2-1. Double-click the **Zynq PS** icon.

-- OR --

Right-click the **Zynq PS** icon and select **Customize Block**.

Figure 1-5: Opening the Re-customization Dialog Box for the Zynq All Programmable SoC PS

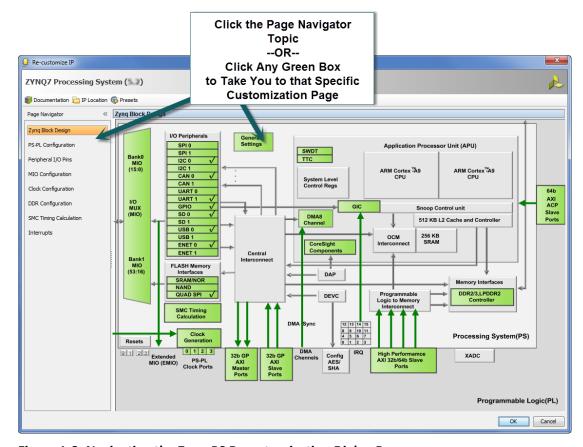

The Re-customization dialog box opens to reveal the Zyng block design.

# 2-3. Import board-specific settings.

If you are using an evaluation board, you may want to load the settings for this board as it will contain many of the parameters specific to that board (such as DDR memory timing parameters, enabled peripherals supported by that board, etc.)

You can also create a .bd file for your custom board if you want and import those settings.

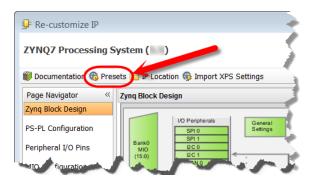

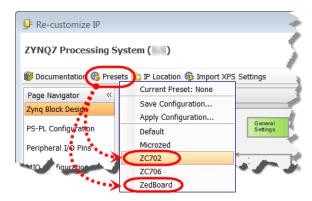

#### 2-3-1. Click Presets.

Figure 1-6: Accessing the Presets Button

# **2-3-2.** Select the template for **ZedBoard**.

All the Xilinx boards that support the device that was selected during the project creation are shown under the System Template (Presets) drop-down list. Even if you selected the part by board, you have the opportunity to select a different board that has the same part on it.

Figure 1-7: Selecting a Preset Template (ZedBoard and ZC702 Shown as Examples)

The next instruction provides you with general guidance as to how to customize various aspects of the PS. At the end of this instruction you will be provided with specific guidance regarding how you are to customize the PS.

# 2-4. Select the page or specific block to re-customize.

**2-4-1.** Click the topic in the Page Navigator or any green (active) box from the Zynq Block Diagram.

Along the left are the navigational tabs that you will use to access different groups of parameters.

Figure 1-8: Navigating the Zynq PS Recustomization Dialog Box

- PS-PL Configuration: This page contains all the signals that cross the PS-PL boundary.

These signals are broken down further into:

- General: Contains default baud rates for the UARTs, FTM Trace buffer settings,

PS-PL cross triggering enables, enables for the clock triggers, and reset.

- DMA Controller: Contains enables for the four peripheral request interfaces.

- GP Master AXI Interface: Enables/disables access to the GP Master AXI Interfaces to the PL.

- GP Slave AXI Interface: Enables/disables access to the GP Slave AXI Interfaces from the PL.

- HP Slave AXI Interface: Enables/disables access to the GP Slave AXI Interfaces from the PL and sets the port width.

- ACP Slave AXI Interface: Enables/disables access to the ACP Slave AXI Interface from the PL.

- o Peripheral I/O Pins

- MIO Configuration

- Clock Configuration

- DDR Configuration

- SMC Timing Calculation

- Interrupts

The following is how your system should be configured:

- Use the ZC702 or Zed preset

- Disable the following features:

- All peripherals except as listed below (accessible through either the Peripheral I/O Pins or the MIO configuration or Block Diagram > I/O Peripherals)

- ➤ UART 1

- ➤ QSPI

- Enable the following features:

- HP Slave AXI Interface > S\_AXI\_HP0 interface

- QSPI (enabled by default through the preset)

- UART1 (enabled by default through the preset)

- **2-4-2.** Configure the PS according to the list above.

- **2-4-3.** Click **OK** to accept the configuration and return to the IPI canvas.

Remember that you can re-configure the processor at any time. However, use caution as you may need to re-run Designer Assistance to handle any changes you make.

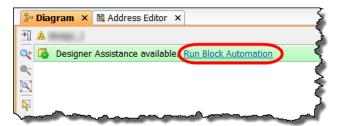

Many IP blocks are supported by the Designer Assistance feature for automating the configuration of an IP block as well as block-specific connections. This is referred to as Block Automation and allows designers to quickly configure new IP blocks for common use cases.

# 2-5. Use Block Automation to automate the configuration of the recently instantiated IP.

**2-5-1.** Click **Run Block Automation** from the Designer Assistance information bar.

Figure 1-9: Designer Assistance Offering Block Automation

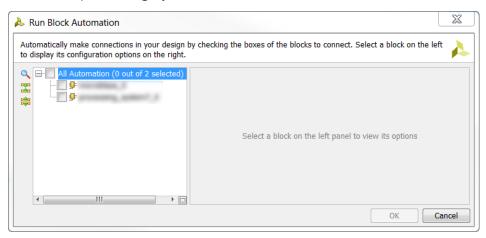

This opens a Run Block Automation dialog box listing all the IP currently in the design eligible for block automation. IPs are listed in a hierarchy on the left and any options associated with a particular automation will be shown in the right pane whenever an IP instance is selected in the left pane.

- **2-5-2.** Click the **Expand All** icon (**(\$)**) to ensure that the list of available automations is fully visible.

- **2-5-3.** Select either the top-level **All Automation** check box or individual blocks as listed below. Unless otherwise indicated within the block list, maintain default automation options for all blocks.

- Blocks: processing\_system7\_0

Figure 1-10: Run Block Automation Dialog Box

Note the various options that are selectable for the PS.

# **Question 3**

Do any of these options look familiar?

- **2-5-4.** Deselect the **Apply Board Preset** option to avoid overwriting the current PS settings.

- The Cross Trigger In and Out selections are used in co-debugging to enable the processor(s) to cause the debug logic (ILAs) in the PL to trigger and to have the trigger signal generated by the debug logic (ILAs) cause the software to pause (a la breakpoint).

- **2-5-5.** Click **OK** to run the selected automation.

| Question 4                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| What does the Block Automation do?                                                                                                                                                                                   |

|                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                      |

| At this point, the PS has connections to external memory (DDR), has its own internal memory for booting, and has a collection of peripherals available for I/O. As is, this could operate with no further additions. |

| Question 5                                                                                                                                                                                                           |

| What happens to the unconnected port to the processing system?                                                                                                                                                       |

|                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                      |

# **Summary**

You just completed the basic tasks of instantiating the processing system of a Zynq-7000 AP SoC, configuring it, and using the Block Automation tool to connect the DDR and fixed I/O to the outside world.

# **Answers**

1. What information does the wizard provide?

The opening page of the wizard provides two methods for locating the aspect of the processing system that can be modified. The Page Navigator (on the left side of the wizard) provides a textual list of the various configurable areas, whereas the Zynq Block Design graphic enables you to quickly locate a configurable aspect by clicking any of the green blocks.

Along the top menu, you can retrieve documentation for this processor, load a preset (pre-configurations for various boards including DDR settings, Flash configuration, etc.), and other less frequently used options.

2. How does configuring the PS of the Zynq-7000 AP SoC differ from configuring a MicroBlaze processor?

The MicroBlaze processor is a softcore processor and the various configurations will impact overall performance, the number and type of resources used, and maximum clock frequency.

The Zynq AP SoC's processing system is dedicated silicon and, while peripherals, clocks, and some connections can be configured, the maximum frequency, performance, and consumed resources is fixed and cannot be changed.

3. Do any of these options look familiar?

The Apply Board Preset option is a duplicate of the process that you performed inside the Re-customization window. If you leave the Apply Board Preset option selected at this stage, it will re-configure the PS to the default board settings and you will have to re-customize the PS again.

4. What does the Block Automation do?

The Block Automation makes the connections to the DDR and the fixed I/O. These are the dedicated pins of the PS. Because they are dedicated, they do not require any constraints.

Remember that the fixed I/O is controlled via the MUI and can be dynamically reconfigured.

5. What happens to the unconnected port to the processing system?

The unused ports (even though they were defined) connect between the PS and PL. If there is no logic in the PL, then these ports simply *dangle* and are not used.

One should be careful, though, not to drive AXI transactions out the master AXI general-purpose port because, since there is no *receiving* AXI logic, the port will hang and likely crash the system.

# Lab 2: Exploring the Architecture of the MicroBlaze Processor

2016.3

#### **Abstract**

Some of the configurable options in the MicroBlaze<sup>™</sup> processor are introduced in this lab. The student will learn how to instantiate and configure the MicroBlaze processor and use Designer Assistance to complete a design.

# **Objectives**

After completing this lab, you will be able to:

- Instantiate the MicroBlaze processor

- Customize the MicroBlaze processor

- Invoke the Design Automation tools to add support logic to the design

# Introduction

Once you have completed the "Driving the IPI Tool" topic cluster (which illustrates how the Vivado® IP integrator tool is used to create and manipulate IP blocks), you can begin to create a MicroBlaze processor design.

Here you will instantiate a MicroBlaze processor and explore different customizations, both predefined and user specific. Once the MicroBlaze processor is configured, you will run the Block Automation tool to add in optional supporting logic, such as clocks and resets, interrupts, memory, etc. Next you will use the Connection Automation tool to connect the remaining pieces of IP. Finally, you will add a UART peripheral and connect it to the system.

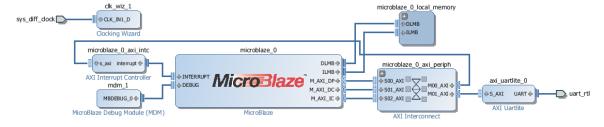

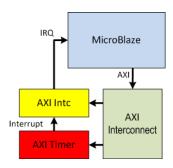

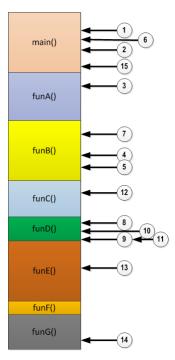

The following figure shows the high-level view of the design that you will build.

Figure 2-1: Block Diagram of the MicroBlaze Processor Design for this Lab

# **General Flow**

# Getting Started Step 1

As this is a hardware lab focusing on how the MicroBlaze processor can be configured, all your work will be done with the Vivado Design Suite IP integrator (IPI).

You will begin by launching the Vivado Design Suite, then loading a helper Tcl script to properly configure the project and quickly get you to the the IPI tool. If you need to refresh your memory regarding the details of project creation or the mechanics of using the IPI tool, refer to the "Driving the IPI Tool" topic cluster.

There are a number of ways to launch the Vivado Design Suite. The two most popular mechanisms are shown here.

# 1-1. Launch the Vivado Design Suite.

This can be done in two standard ways, use your preferred method.

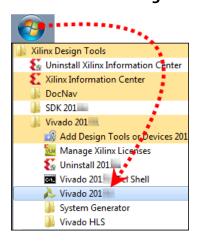

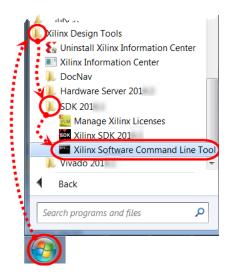

1-1-1. Select Start > All Programs > Xilinx Design Tools > Vivado 2016.3 > Vivado 2016.3.

Figure 2-2: Launching the Vivado Design Suite from the Start Menu

-- OR --

Double-click the **Vivado Design Suite** shortcut icon ( on the desktop.

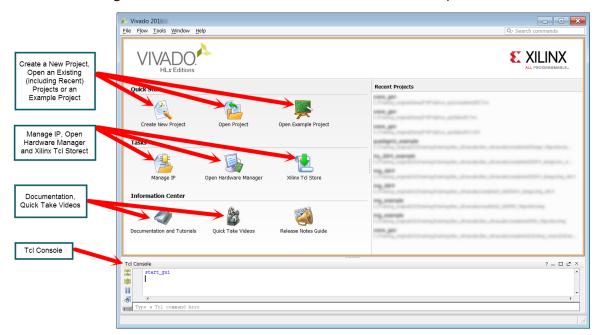

The Vivado Design Suite opens to the Welcome window. From the Welcome window you can create a new project, open an existing project, or enter Tcl commands directly into the Vivado Design Suite as well as access documentation and examples.

Figure 2-3: Vivado Design Suite Welcome Screen

With the Vivado Design Suite now open, you will load a helper Tcl script and run it to configure the project and get you to the important part of this lab—working with the MicroBlaze processor.

The Vivado Design Suite offers both GUI and scripted control. Scripted control takes the form of Tcl commands. These Tcl commands can be entered directly into the tool one at a time, or an entire Tcl script can be loaded and executed.

# 1-2. Run a Tcl script.

# **1-2-1.** Locate the Tcl command line entry.

The command line entry can be found either on the Welcome page prior to a project being opened, or once a project has been opened.

From the Welcome screen:

Figure 2-4: Accessing the Tcl Console from the Getting Started Page

From an opened project:

Figure 2-5: Entering Commands into the Tcl Console from an Open Project

The default directory for the Tcl environment is nested within the Xilinx installation directory. This placement, however, is often disadvantageous. In most cases, you will want to navigate to a more useful path. To do this, use the cd command to change directory to the user directory.

**1-2-2.** Change the current working directory to where the Tcl script is located by entering:

# cd C:\training\ArchMicroBlaze Overview\support

Remember that the Tcl environment is based on Linux and requires the '/' character to delimit hierarchical paths.

**1-2-3.** Verify that you are now where you want to be by entering the following into the Tcl command line:

#### pwd

The current working directory is displayed. If you are not where you want to be, use the cd command to change to C:\training\ArchMicroBlaze Overview\support.

**1-2-4.** Enter the following Tcl command:

# source exploreMB completer.tcl

The Tcl script is run as though you typed each command included in the Tcl script into the Tcl command line. You can follow the execution of the script and monitor for any errors or warnings in the Tcl Console.

With the Tcl script now loaded, you will run the *createProject* and *createBlockDesign* procs to build the Vivado Design Suite project and create an appropriately named block design in which you will perform the remainder of this lab.

# 1-3. Run the *createProject* and *createBlockDesign* procs.

- **1-3-1.** Enter the following into the Tcl command line to create the Vivado Design Suite project: createProject

- **1-3-2.** Enter the following into the Tcl command line to create the block design in which you will build your MicroBlaze processor system:

createBlockDesign

# Adding and Customizing the MicroBlaze Processor

Step 2

With the block diagram canvas open, you will now add and customize a MicroBlaze processor.

# 2-1. Add a MicroBlaze to the IP Integrator canvas.

If you do not recall how to perform this task, refer to the "Adding a Processor to the Block Design" section under IP Integrator Operations in the *Lab Reference Guide*.

Remember that adding a processor IP is just like adding any other type of IP to the canvas. You can also review the "Driving the IPI Tool" topic cluster for a guided example.

Next you will experiment with several different configurations to see how the MicroBlaze processor is realized in the FPGA/PL.

# 2-2. Open the MicroBlaze processor's Re-customization dialog box.

**2-2-1.** Double-click the **MicroBlaze** IP to open the Re-customization dialog box.

Alternatively, you can right-click the **MicroBlaze** IP and select **Customize Block**.

The MicroBlaze Configuration Wizard opens.

# Question 1

| What information does the Resources tab provide? |  |  |  |  |  |

|--------------------------------------------------|--|--|--|--|--|

|                                                  |  |  |  |  |  |

|                                                  |  |  |  |  |  |

|                                                  |  |  |  |  |  |

|                                                  |  |  |  |  |  |

|                                                  |  |  |  |  |  |

# Question 2

Fill out the Default configuration in the table below.

As you investigate different configurations, you will add information to this table so that you can quickly see the tradeoffs between performance, area, and frequency.

| Configuration Name  | Frequency | Area | Performance |

|---------------------|-----------|------|-------------|

| Default             |           |      |             |

| Minimum Area        |           |      |             |

| Maximum Performance |           |      |             |

| Maximum Frequency   |           |      |             |

| Linux with MMU      |           |      |             |

| Low-End Linux with  |           |      |             |

| Typical             |           |      |             |

#### **Configurations Table**

Consider the following scenario: You are building a system on a small FPGA or Zynq® All Programmable SoC device. An accelerator (the most critical portion of this design) occupies a large portion of the total fabric/PL.

It is decided that you must add a MicroBlaze processor to this design for housekeeping tasks (such as user interface, communications, power monitoring, etc.) but not for computations.

# **Question 3**

| Given the above scenario, what configuration from the Predefined Configurations section would you choose and why? |

|-------------------------------------------------------------------------------------------------------------------|

|                                                                                                                   |

|                                                                                                                   |

|                                                                                                                   |

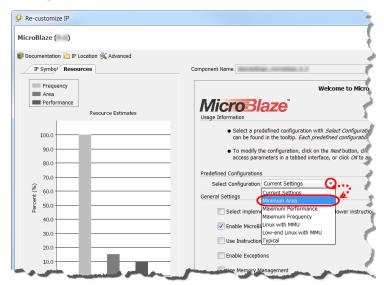

# 2-3. Select the Minimum Area configuration.

**2-3-1.** Select **Minimum Area** from the Select Configuration drop-down list from the Predefined Configurations section.

Figure 2-6: Selecting the Minimum Area Configuration

# **Question 4**

Add the Frequency, Area, and Performance numbers to the Configurations table for the Minimum Area configuration.

As it turns out, there is a MicroBlaze processor in the accelerator portion of the design mentioned above. This particular MicroBlaze processor is responsible for preparing the data for the accelerator and throughput is paramount.

# **Question 5**

For this scenario, what configuration might you select and why?

# 2-4. Select the Maximum Performance configuration.

**2-4-1.** Select **Maximum Performance** from the Select Configuration drop-down list from the Predefined Configurations section.

# **Question 6**

Add the Frequency, Area, and Performance numbers to the Configurations table for the Maximum Performance configuration.

- 2-5. Select each of the remaining configurations and enter the values for the Frequency, Area, and Performance columns into the Configurations table.

- **2-5-1.** Repeat the previous instruction but this time selecting the next pre-defined configuration from the Select Configuration drop-down list.

# **Question 7**

Add the Frequency, Area, and Performance numbers to the Configurations table for each of the remaining configurations.

# **Question 8**

| Did you notice any changes to the General Settings section when the different configurations were selected? |

|-------------------------------------------------------------------------------------------------------------|

|                                                                                                             |

|                                                                                                             |

| Question 9                                                                                                  |

| Where can you find an explanation for these options?                                                        |

|                                                                                                             |

|                                                                                                             |

You should now have the Typical predefined configuration selected.

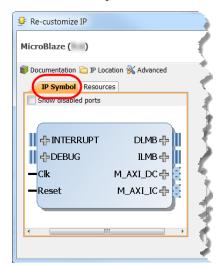

**2-5-2.** View the ports of the MicroBlaze processor to see what access points the MicroBlaze processor has to connect to the rest of the system.

# 2-6. Use the IP Symbol tab to view the graphical representation of the MicroBlaze processor in its current configuration.

**2-6-1.** Select the **IP Symbol** tab.

Figureb 2-7: Viewing the Graphical Representation of the Current Configuration of the MicroBlaze Processor

**2-6-2.** Click the '+' sign in the Interrupt interface to see the signals that comprise that interface.

Figure 2-8: Expanded Interrupt Interface

This will show you the individual ports that comprise the Interrupt interface. You can explore other interfaces if you want.

**2-6-3.** Click the '-' sign next to the Interrupt interface to collapse the interface back to a single connection.

# **Question 10**

When might the IP symbol in the IP Symbol tab change?

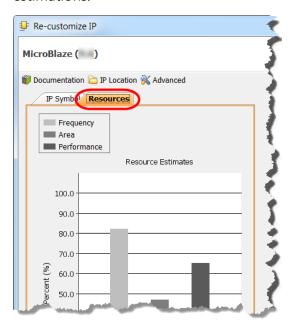

- **2-6-4.** Click **Next** to advance to the next page of the re-customization.

- **2-6-5.** Select the **Resources** tab to see how your choices affect the resources and performance estimations.

Figure 2-9: Selecting the Resources Tab During Re-customization of the MicroBlaze Processor

For the sake of this example, you can assume that the code will have sections requiring significant numeric processing of floating point numbers.

**2-6-6.** Select the **EXTENDED** mode for the FPU.

# **Question 11**

| How does one know when to use the different settings and options?                     |

|---------------------------------------------------------------------------------------|

|                                                                                       |

|                                                                                       |

|                                                                                       |

| Question 12                                                                           |

| How does selecting the FPU Extended mode change resource utilization and performance? |

**2-6-7.** Click **Next** to advance to the page which customizes exception handling.

Since this design pre-supposes a lot of floating point activity, it makes sense to enable the FPU exceptions.

**2-6-8.** Select the **Enable Floating Point Unit Exceptions** option to enable these exceptions.

Figure 2-10: Enambling the FPU Exceptions

# **Question 13**

How does enabling these exceptions affect the resource estimates?

**2-6-9.** Click **Next** to advance to the Cache configuration page.

Here you can enable or disable the instruction and/or data caches and control other parameters. This system will work acceptably without changing any of these parameters.

**2-6-10.** Click **Next** to advance to the Debug configuration page.

Because the MicroBlaze processor (and its associated support logic) is implemented in fabric/programmable logic, changes to the debug support can have significant effect on the resource estimates—particularly area.

**2-6-11.** Click **Next** to advance to the Buses page, the final page of the wizard.

Here you can enable the AXI and ACE interfaces, designate the number of streaming licks, and enable the trace bus interface (for debugging).

The local memory bus (LMB) interfaces are already enabled as part of the Typical configuration and are used to connect to block RAMs to provide the MicroBlaze processor with low-latency, user-manageable memory.

Note that the caches connect to the MicroBlaze processor via the M\_AXI\_DC and M\_AXI\_IC ports.

**2-6-12.** Click **OK** to accept the configuration and return to the IPI canvas.

Remember that you can re-configure the MicroBlaze processor at any time. However, use caution as you may need to re-run Designer Assistance to handle any changes you make.

# **Building a System around the MicroBlaze Processor**

Step 3

With the MicroBlaze processor now configured, it must be connected to supporting logic, including (but not limited to):

- Cache memory

- Clock

- Reset

- Interrupt controller

- Debug logic (MicroBlaze Debug Module MDM)

- Local memory

You will now use Designer Assistance to run block automation.

3-1. Run block automation to build the supporting logic for the MicroBlaze processor.

While many pieces of IP will simply be connected when block automation is run, the MicroBlaze processor is a complex piece of IP and requires additional information so that block automation can assemble the properly configured system.

**3-1-1.** Click the **Run Block Automation** hyperlink in the information bar to launch the run bLock automation.

Figure 2-11: Launching the Run Block Automation for the MicroBlaze Processor

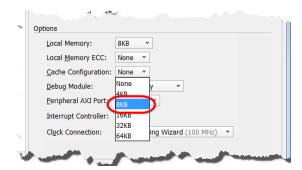

Run Block Automation Automatically make connections in your design by checking the boxes of the blocks to connect. Select a block on the left to display its configuration options on the right. All Automation (1 out of 1 selected) Description MicroBlaze connection automation generates local memory of selected size, and caches can be configured. MicroBlaze Debug Module, Peripheral AXI interconnect, Interrupt Controller, a clock source, Processor System Reset are also added and connected as needed. Instance: /microblaze\_0 Options Local Memory: 8KB ▼ Local Memory ECC: None ▼ Cache Configuration: None \* Debug Module: Debug Only Peripheral AXI Port: Enabled • Interrupt Controller: Clock Connection: New Clocking Wizard (100 MHz) ? OK Cancel

Note the current configuration as shown in the figure below.

Figure 2-12: Default Settings for Run Block Automation for the MicroBlaze Processor

The MicroBlaze processor's Re-configuration Wizard does not communicate with the Run Block Automation tool.

**3-1-2.** Select **8KB** from the Cache Configuration drop-down list to change the cache configuration for each side.

Figure 2-13: Selecting an 8KB Cache

- **3-1-3.** Select the **Interrupt Controller** option to add an interrupt controller to the system.

- **3-1-4.** Click **OK** to accept the options and run the Block Automation tool.

# **Question 14**

What gets built?

While this system is perfectly adequate for responding to interrupts and performing basic processing, there a formal I/O channel does not exist.

## 3-2. Add the IP listed below to the block design.

If you do not recall how to perform this task, refer to the "Adding IP to an IP Integrator Block Design" section under IP Integrator Operations in the *Lab Reference Guide*.

#### AXI UARTlite for basic text I/O

## 3-3. Customize the IP according to the table below.

If you do not recall how to perform this task, refer to the "Customizing IP" section under IP Integrator Operations in the *Lab Reference Guide*.

| Baud Rate | 19200     |

|-----------|-----------|

| Data Bits | 8         |

| Parity    | No Parity |

You may note that there are no connections to the UART lite, nor to the Clocking Wizard, nor to the concat IP (which concatenates individual bits to form an input into the interrupt controller).

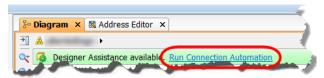

#### 3-4. Run the Connection Automation tool to make the next set of connections.

**3-4-1.** Click the **Run Connection Automation** link in the status bar of the block design's Diagram tab.

Figure 2-14: Launching Run Connection Automation

The Run Connection Automation dialog box opens and invites you to identify the IP that you want to run the connection automation for.

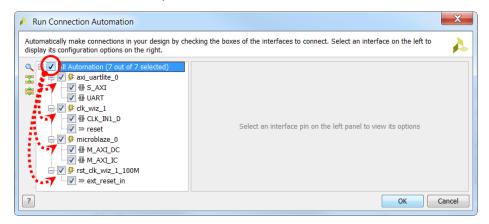

## **3-4-2.** Select the **All Automation** option.

This will cause all the options to be selected.

Figure 2-15: Selecting the All Automation Option

- **3-4-3.** Click **OK** to run the Connection Automation tool.

- **3-4-4.** [Optional] Click the **Regenerate Layout** icon ( ) in the left-hand vertical toolbar to redraw the current system.

Generally, this will cause the system to be redrawn with inputs on the left-hand side of the canvas and outputs on the right-hand side.

## **Question 15**

Are there any unconnected inputs and/or outputs?

3-5. Remove the microblaze\_o\_xlconcat IP from the design and connect the interrupt output of the AXI Uartlite into the AXI Interrupt Controller's input.

The purpose of this IP is to collect multiple interrupts and merge them into a single bus for the AXI Interrupt Controller. Since there is only one interrupt signal (from the UART), this IP is no longer needed.

- **3-5-1.** Select the microblaze\_0\_xlconcat IP.

- **3-5-2.** Press **<Del>** to delete the selected item.

Note that this also removes any nets connected to this IP.

**3-5-3.** Click-drag a connection from the axi\_uartlist\_0 interrupt port to the microblaze\_0\_axi\_intc.intr[0:0] port.

- 3-6. Validate the design to catch any connection and address map errors.

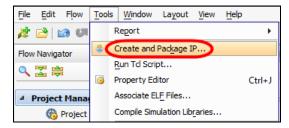

- **3-6-1.** Select **Tools** > **Validate Design**.

Any issues are displayed in the Console window.

- **3-6-2.** Look for any errors—there should be none.

- 3-6-3. Click **OK**.

| 0   | stion | 16 |

|-----|-------|----|

| Que | SUUII | ΤO |

| Is this now a complete system? |  |  |

|--------------------------------|--|--|

|                                |  |  |

|                                |  |  |

|                                |  |  |

## **Summary**

You just completed developing a MicroBlaze processor-based embedded design. You explored the MicroBlaze processor's Re-customization Wizard and the Run Block Automation options for rapidly constructing a viable system. A UART was also added to this system to extend its capabilities. You could have continued to add peripherals and memories in the same basic fashion that the UART was added.

#### **Answers**

1. What information does the Resources tab provide?

The Resources Tab shows a bar chart indicating the relative performance of the MicroBlaze processor as configured by the current settings in the configuration wizard compared to the maximum frequency that the device can run compared to the amount of area that the processor will occupy in the FPGA/PL.

The default settings show that this configuration will run at the fastest clock rate ( $f_{max}$ ) possible for any configuration of the MicroBlaze processor. Additionally the settings show that the performance is about 1/10th of the highest performing configuration of the MicroBlaze processor. Finally, the settings show that it will take up about 12% of the area of the largest MicroBlaze processor configuration.

2. Fill out the Default configuration in the table below.

| Configuration Name | Frequency | Area | Performance |  |

|--------------------|-----------|------|-------------|--|

| Default            | 100%      | 13%  | 10%         |  |

3. Given the above scenario, what configuration from the Predefined Configurations section would you choose and why??

The best choice would be the Minimum Area configuration so that it has the best chance of fitting into the remaining logic. Since this MicroBlaze processor is only performing housekeeping chores, performance and frequency are secondary concerns to that of area.

Even if the rest of the logic is running at a higher clock speed, this MicroBlaze processor can take its clock from one of the many clock dividers (PLLs) on the device and run at a lower speed than the other IP on the device.

4. Add the Frequency, Area, and Performance numbers to the Configurations table for the Minimum Area configuration.

| Configuration Name | Frequency | Area | Performance |

|--------------------|-----------|------|-------------|

| Default            | 100%      | 13%  | 10%         |

| Minimum Area       | 87%       | 9%   | 10%         |

5. For this scenario, what configuration might you select and why?

Since throughput (performance) is the most important factor, the Maximum Performance configuration will likely be the best choice.

6. Add the Frequency, Area, and Performance numbers to the Configurations table for the Maximum Performance configuration.

| Configuration Name  | Configuration Name Frequency |     | Performance |

|---------------------|------------------------------|-----|-------------|

| Default             | 100%                         | 13% | 10%         |

| Minimum Area        | 87%                          | 9%  | 10%         |

| Maximum Performance | 61%                          | 61% | 100%        |

7. Add the Frequency, Area, and Performance numbers to the Configurations table for each of the remaining configurations.

| Configuration Name        | Frequency | Area | Performance |

|---------------------------|-----------|------|-------------|

| Default                   | 100%      | 13%  | 10%         |

| Minimum Area              | 87%       | 9%   | 10%         |

| Maximum Performance       | 61%       | 61%  | 100%        |

| Maximum Frequency         | 100%      | 13%  | 10%         |

| Linux with MMU            | 58%       | 57%  | 71%         |

| Low-End Linux with<br>MMU | 61%       | 47%  | 57%         |

| Typical                   | 68%       | 32%  | 61%         |

8. Did you notice any changes to the General Settings section when the different configurations were selected?

The options in the General Settings section enable you to modify the predefined configurations to better suit your needs.

9. Where can you find an explanation for these options?

Vivado Design Suite User Guide: Embedded Processor Hardware Design (UG898), Chapter 4.

Appendix A (Performance and Resource Utilization) of the *MicroBlaze Processor Reference Guide* (UG984) also contains actual frequencies and LUT utilizations for the different families.

10. When might the IP symbol in the IP Symbol tab change?

Any configuration that changes the number or types of ports will cause the IP symbol to be updated to show the new ports. The General Settings > Enable Discrete Ports option makes a number of the control and sense ports available.

Similarly, the Show Disabled Ports option shows all of the possible ports on the MicroBlaze processor (a superset of all configurations). The active ports are listed in black and the disabled ports are shown in gray.

11. How does one know when to use the different settings and options?

It is generally a good rule to use one of the pre-defined configurations as a starting point. Then based on the system constraints (such as limited resources or clocking speeds) or code constraints (heavy use of floating point numbers, integer multiplication and division, etc.) the MicroBlaze processor can be tailored to meet specific goals.

Before experimenting with these options, be sure to read the *MicroBlaze Processor Reference Guide* (UG984).

12. How does selecting the FPU Extended mode change resource utilization and performance?

Prior to the enabling of the FPU, the frequency was about 81%, area about 32%, and performance was at about 61%.

Afterwards, the frequency remains the same at about 81%; however, the area increases to about 48% and the performance increases to about 65%.

An interesting point to think about: If your code does not perform any floating point computations, your system's overall performance will not change. However, if your system is performing a lot of floating point computations, then the system's actual performance may be significantly higher. Refer to the "Amdahl's Law" topic cluster to better understand how accelerating one part of the code affects the entire system's performance.

13. How does enabling these exceptions affect the resource estimates?

Frequency is reduced from about 81% to about 65%. Neither area nor performance changes significantly.

## 14. What gets built?

The Run Block Automation tool adds and connects the following IP to the system:

- Cocking Wizard: Provides a 100-MHz clock to the MicroBlaze processor system.

- Processor System Reset: Manages both internal and external signals to reset the system.

It produces five resets (of which one is not used): One for the peripherals, one for the

interconnect controller, one for the bus structure (and is used by the local memory), and

one for the processor.

- MicroBlaze Debug Module: Connects to the chip's BSCAN (JTAG) chain and provides debugging support for the MicroBlaze processor.

- Interrupt Controller: Manages interrupts from various hardware sources and produces an interrupt signal to the MicroBlaze processor.

- AXI Interconnect: An AXI switch that enables various AXI masters (in this case, the MicroBlaze processor) to connect to a number of slave device or peripherals (in this case, the Interrupt Controller IP).

- Local Memory: A collection of block RAMs that house local instruction and data. Small applications can be run completely from this local memory.

## 15. Are there any unconnected inputs and/or outputs?

Yes. the concat IP (which collects interrupts and provides them not as single signals, but as a bus to the Interrupt Controller IP) wants two interrupts and the AXI Uartlite has an unconnected output.

#### 16. Is this now a complete system?

Yes, with one significant consideration. The MicroBlaze processor was configured to use caches. These AXI cache lines are run into the AXI Interconnect; however, there are no memory devices attached to the AXI Interconnect, which renders the cache connections useless!

You can optionally add block RAMs to the AXI Interconnect for the caches. Even so, caching is beneficial only when there is a slower memory, such as DDR. You are better off removing the caching capability of the MicroBlaze processor and enlarging the block RAMs attached to the local memory bus (LMB).

If there is a shortage of block RAM (that is, not enough block RAM to hold data and instructions), you would need to instantiate a MIG (Memory Interface Generator) to connect to off-chip DDR memory and instantiate block RAMs for cache.

Even as is, this design could work. Just as any FPGA/SoC/MPSoC design requires when there are signals entering or leaving the logic/PL, constraints are required to properly map clock, reset, and communication signals in and out of the device.

# Lab 3: Driving the SDK Tool 2016.3

## **Abstract**

This lab introduces you to the basic operations for SDK. Concepts such as project creation, adding existing source code to an application, compilation and linking, and downloading are covered. Numerous other labs focus on other aspects of the SDK tools.

## **Objectives**

After completing this lab, you will be able to:

- Create an SDK workspace

- Create the three basic types of projects typically required for application development

- Navigate application source code

- Produce and download an ELF to a hardware platform

## Introduction

SDK is a powerful and complex tool. Knowing how to navigate its basic capabilities will make software development a much easier task.

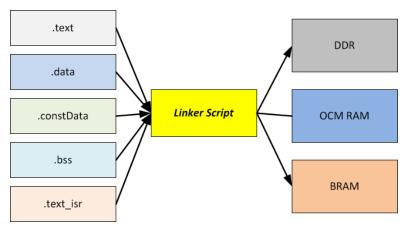

First, you must understand a few basic SDK concepts, starting with the workspace. The workspace is simply a location (usually a directory) that contains not only all of the projects (each in its own subdirectory), but also a few SDK files that help SDK remember user settings and how projects relate to each other.

Next is the concept of the project. A project is a collection of related files for a certain type of thing. Some projects that SDK intrinsically knows about and that you will use in this lab: the hardware platform specification, board support package, and application.

Hardware Platform Description from Vivado Design Suite (.hdf)

Hardware Platform Specification Project

Source Code

Application Project

Compiler Options

Linker Script

Compiler/Linker

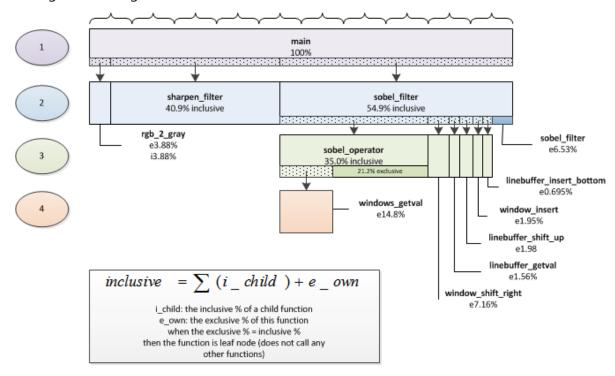

The following figure illustrates the relationships among these three primary projects:

Figure 3-1: Relationships Among the Three Primary Project Types

You will begin by creating a new workspace and, within that workspace, one of each of the commonly used projects.

As the diagram suggests, you will begin by importing a hardware description file (HDF) which was created with the Vivado® Design Suite that will be used to create the hardware platform specification project. Next you will create an application project (and, as part of the process, you will generate a board support package based on the hardware platform specification project).

**ELF File**

With the three projects created, you will add provided source code to the application project and compile, link, and load it to generate an ELF (executable load format) file. Since the provided source code contains some errors, you will correct them and recompile. With the errors corrected, the resulting ELF file can then be downloaded onto the board and run.

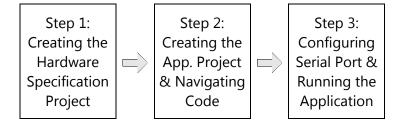

## **General Flow**

## **Launching SDK and Creating the Hardware Specification Project**

Step 1

You will begin this lab by open the SDK tool, identifying its workspace (where the projects will be kept on disk), and creating a hardware specification project that describes the hardware system that the software will be running on from a file provided to you which was exported from the Vivado Design Suite.

## 1-1. Launch the SDK tool and set the workspace.

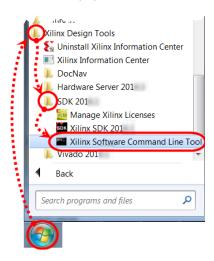

1-1-1. Select Start > All Programs > Xilinx Design Tools > SDK 2016.3 > Xilinx SDK 2016.3 to launch the tool.

Alternatively, you can launch the tool from its desktop shortcut, if available.

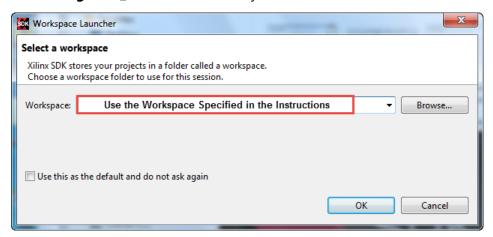

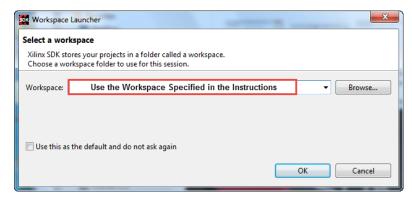

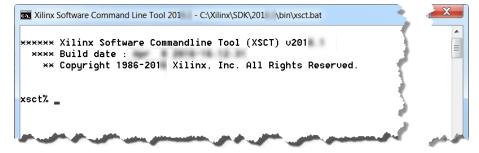

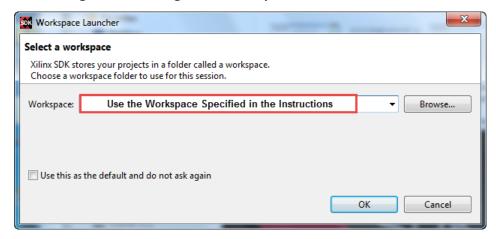

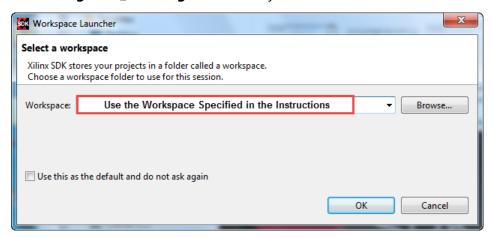

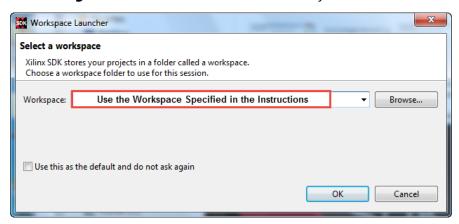

The Workspace Launcher opens after a moment.

The SDK tool creates a workspace environment that initially only contains a thin structure that tracks tool settings and maintains the SDK tool log file. In SDK, as projects are added, this workspace will update to include hardware projects, BSPs, and your software applications. Workspaces can be switched from within the SDK tool (select **File** > **Switch Workspace**).

If it becomes necessary to move a software application to another location or computer, use the import and export features. Manually copying files is not recommended as workspace files are set to use absolute path names and this will cause the tool to become unstable.

The default location for the SDK software workspace (when launching from within the Vivado® Design Suite) is the root directory of your hardware project; however, a long path name can lead to problems on Windows-based machines. There is no default location for the tool projects. Placing your project at the root level or one hierarchical level below helps keep the path names as short as possible and is recommended.

Many of the Xilinx labs do not follow this guidance as it is important to keep a predictable structure through the various courses and labs. These labs have been tested to ensure that path name lengths do not cause problems.

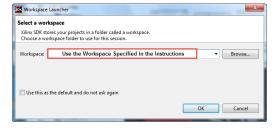

**1-1-2.** Enter **C:\training\SDK\_Driver\lab** into the Workspace field or use the Browse button when the Workspace Launcher opens.

Note that when you use the Browse button, you will need to select the **C:\training\SDK\_Driver\lab** directory and click **OK**.

Figure 3-2: Setting Up the Workspace Environment Path

**1-1-3.** Click **OK** to close the Workspace Launcher dialog box and open the new workspace.

A workspace location and hardware platform are created when the **Export Hardware Design for SDK** command is performed from the Vivado Design Suite (or they can be created manually). While not a requirement, it is a good idea to keep the related files together.

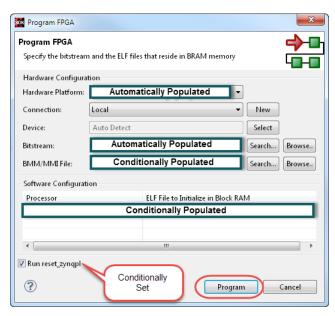

Note that SDK must associate with a hardware system that has been previously exported so that an appropriate software platform or board support package can be built. However, the SDSoC™ development environment can take advantage of available platforms (for ZC702/ZedBoard). The hardware platform can be created for your custom hardware.

Usually, a platform provider builds the platform hardware using the Vivado Design Suite and IP integrator. For more information on platform creation, refer to the "SDSoC Platform Creation" topic cluster.

When the SDK tool is launched on its own, you must manually identify where you want the workspace and create (or import) the necessary hardware description to begin developing an application.

**1-1-4.** Close the **Welcome** tab if it appears.

This will give you more room to view your project. You may also want to maximize the SDK window, as there will be a lot to see.

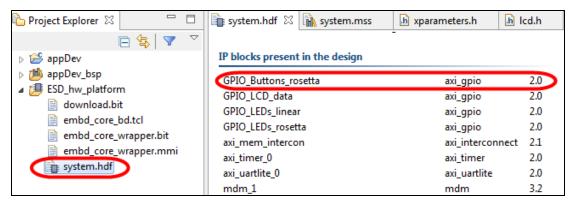

The hardware platform specification contains a thorough description of the hardware design: what types of processors are present, active peripherals in the PS and PL for Zynq® All Programmable SoC-based systems or a list of all peripherals for a non-Zynq All Programmable SoC system, a full system memory map, etc. Based on this description, software such as the board support package (BSP) and application can be tailored to the hardware.

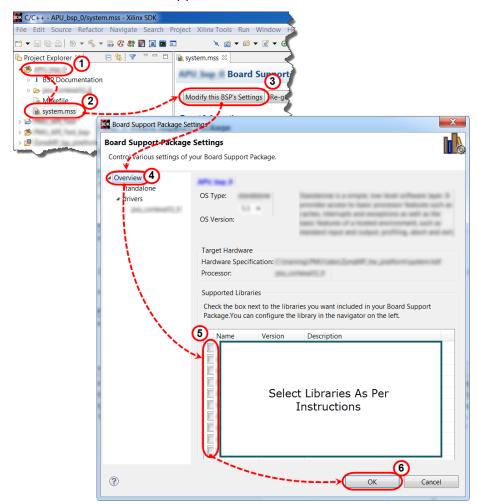

## 1-2. Create the hardware platform specification.

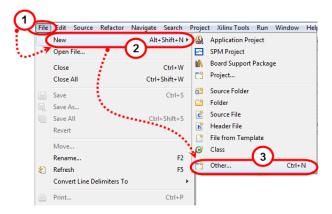

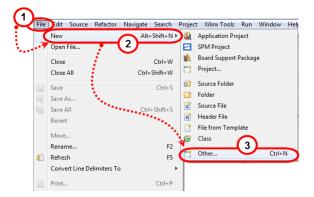

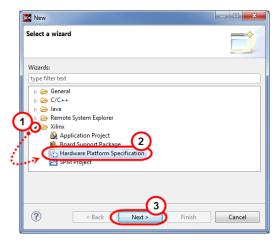

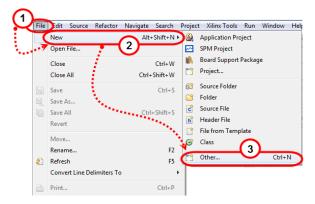

**1-2-1.** Select **File** (1) > **New** (2) > **Other** (3) to see the Xilinx-specific options.

Figure 3-3: Accessing the New Wizards

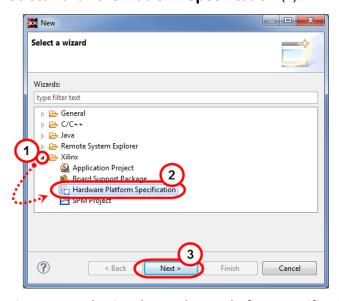

The Select a Wizard dialog box opens. Here you can select one of many different wizards.

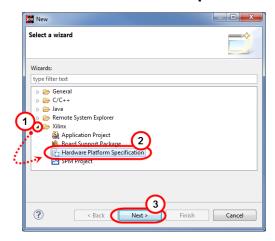

- **1-2-2.** Expand the **Xilinx** folder (1).

- 1-2-3. Select Hardware Platform Specification (2).

Figure 3-4: Selecting the Hardware Platform Specification Wizard

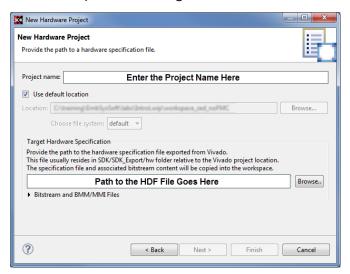

1-2-4. Click **Next** to open the New Hardware Project dialog box (3).

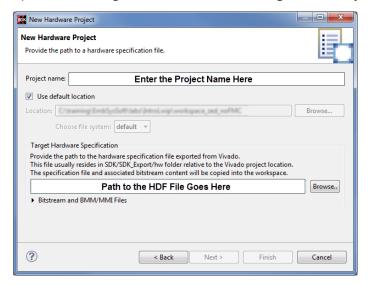

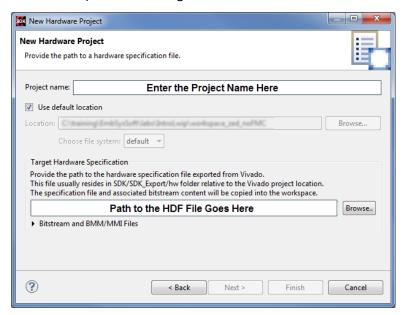

The New Hardware Project dialog box opens. Here you will be able to specify a project name and the hardware description file that was exported by the Vivado Design Suite.

- **1-2-5.** Enter **SDKintro\_hw** in the *Project name* field.

- **1-2-6.** Browse to the *C:\training\SDK\_Driver\support* directory under the Target Hardware Specification region and select the **blkdsgn\_[ZC702 | Zed]\_[A9 | MicroBlaze].hdf** file.

Figure 3-5: New Hardware Project Dialog Box

**1-2-7.** Click **Finish** to create the new hardware project.

## **Creating the Application Project and Navigating Code**

Step 2

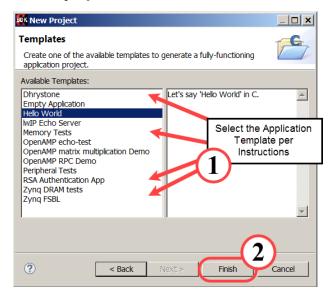

With the SDK tool open and the hardware description imported, you will now create a new application and, as part of creating the new application, you will create a board support package with the default settings.

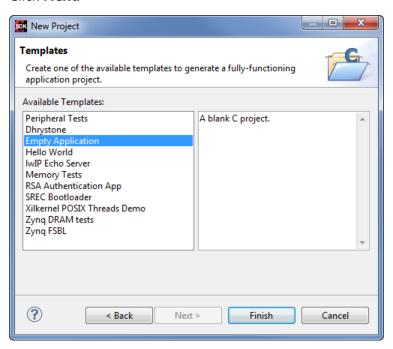

While there are a number of templates available during the creation of an application project, you will use the Empty Project template and import the provided source code files.

Using the Application Project Wizard is a quick way to set up a C or C++ software application project that targets an existing processor and OS platform (Standalone or Linux). You can automatically generate the board support package (BSP) or select an existing one. Based on the dialog box choices, the appropriate tool chain is selected for pre-processing, compiling, assembling, and linking.

## 2-1. Create a new C/C++ application project named *SDKintro\_app*. Use the board support package named *default\_bsp*.

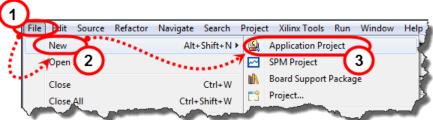

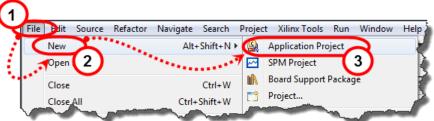

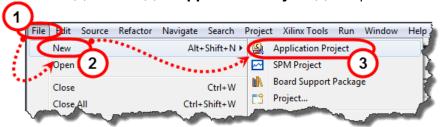

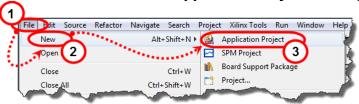

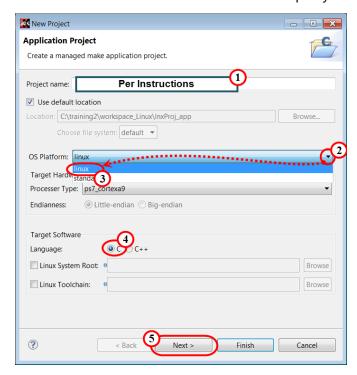

**2-1-1.** Select **File** (1) > **New** (2) > **Application Project** (3) to open the New Project dialog box.

Figure 3-6: Creating an Application Project

- **2-1-2.** Enter **SDKintro\_app** as the project name.

- **2-1-3.** Ensure that you have **SDKintro\_hw** selected from the Hardware Platform drop-down list as the SDK tool can manage multiple platforms within a single workspace.

- This will populate the Processor drop-down list accordingly.

- **2-1-4.** Ensure that **ps7\_cortexa9\_0 or microblaze\_0** is selected from the Processor drop-down list.

- **2-1-5.** Ensure that **standalone** is selected from the OS Platform drop-down list.

**2-1-6.** Select **Use Existing** and choose an existing BSP from the drop-down list if you have already created a BSP for this hardware platform; otherwise, select **Create New** and enter the name for the BSP as **default\_bsp**.

Figure 3-7: Entering Application Project Information

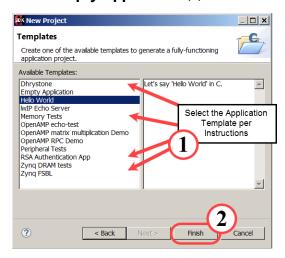

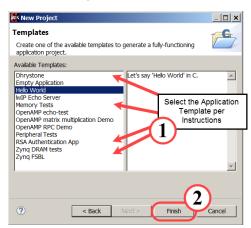

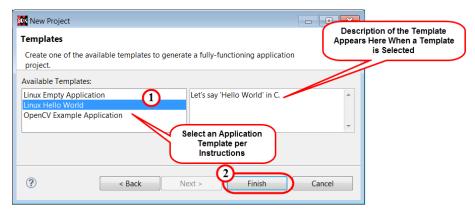

- **2-1-7.** Click **Next** to select the template for this application.

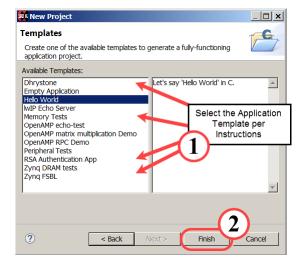

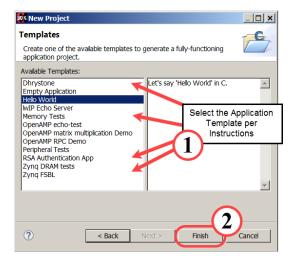

- 2-1-8. Select Empty Application (1).

Figureb 3-8: Selecting an Application Template (Selection in Figure May Not Match Instructions)

**2-1-9.** Click **Finish** to create the new project (2).

As the project is created, the new BSP is compiled and any sources from the templates are also compiled. The creation of the new project usually takes less than a minute.

The application framework is generated and now it is time to load the provided source files.

It is common practice to add existing resource files (\*.c, \*.h, \*.cpp, etc.) to a software project. The Eclipse framework requires this operation to be performed as an import function.

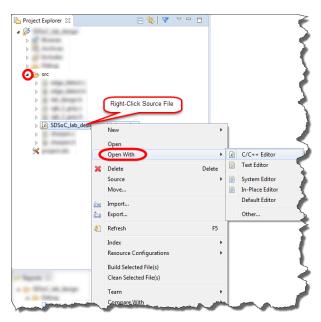

2-2. Add SDKintro\_main.c, hardware\_support.c, hardware\_support.h, LED\_drivers.c, LED\_drivers.h, platform.c, platform.h, platform\_config.h, serialPort\_helper.c, serialPort\_helper.h, utils\_print.c, and utils\_print.h to the application.

The preferred method for importing sources is shown here.

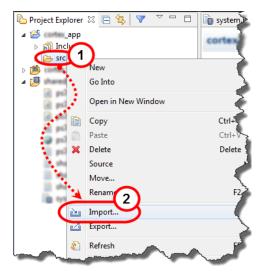

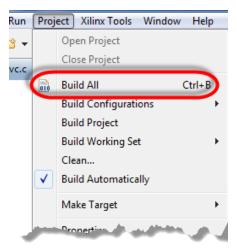

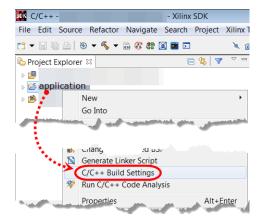

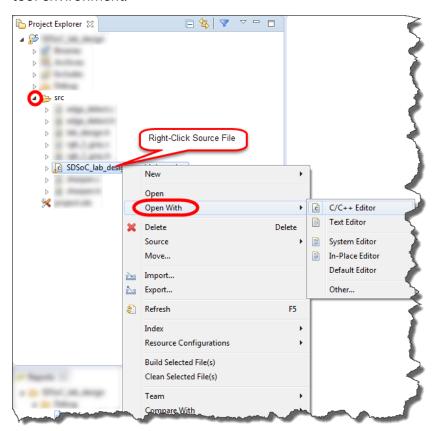

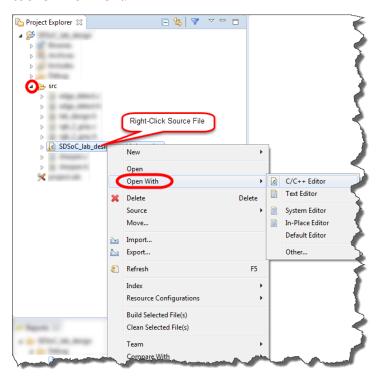

- **2-2-1.** Expand the project named **SDKintro\_app** > **src** using the Project Explorer.

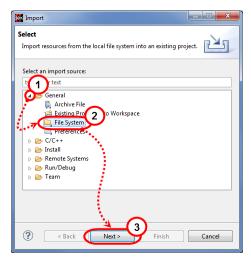

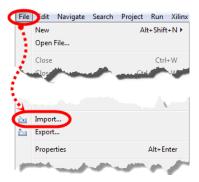

- **2-2-2.** Right-click the desired destination directory in the project that you want to place the resource files (typically the src directory) (1).

- **2-2-3.** Select **Import** to open the Import Wizard (2).

Figure 3-9: Importing a Resource File

The Import Wizard dialog box opens.

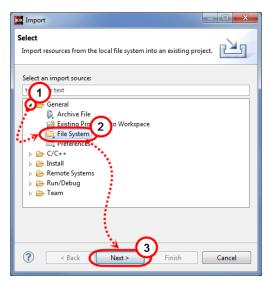

- **2-2-4.** Expand **General** (1).

- **2-2-5.** Select **File System** as you will be selecting individual files directly from the file system (2).

Figure 3-10: Selecting File System

- **2-2-6.** Click **Next** to advance to specifying the files to import (3).

- **2-2-7.** Browse to *C*:\training\SDK\_Driver\support in the From directory field.

- 2-2-8. Select the file(s) by checking the box beside SDKintro\_main.c, hardware\_support.c, hardware\_support.h, LED\_drivers.c, LED\_drivers.h, platform.c, platform.h, platform\_config.h, serialPort\_helper.c, serialPort\_helper.h, utils\_print.c, and utils\_print.h.

Figure 3-11: Selecting Resource Files

The *Into folder* directory will default to the location selected when you engaged the import function, but you can click **Browse** to change this location.

#### **2-2-9.** Click **Finish** to import the selected files and close the wizard.

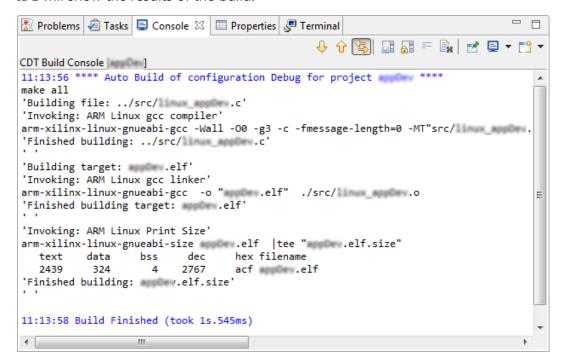

**Note:** If the workspace has the automatic build option enabled, the project will automatically build with the new resource files. The Console view at the bottom of the IDE will show the results of the build.

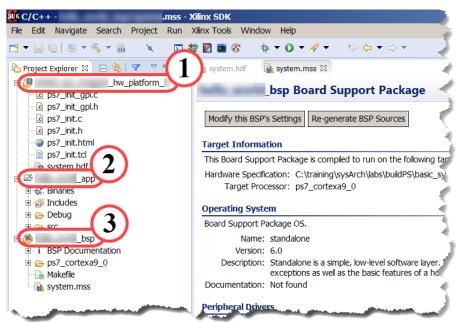

The Project Explorer tab shows a tree structure of the various projects in this workspace. Each entity is its own project; that is, the hardware platform specification is a complete project and contains the XML description of the hardware and other necessary hardware files (usually including a bitstream).

The BSP is another project that is dependent on the hardware platform specification and contains various libraries, including device drivers for the standalone configuration. The BSP project is dependent upon a hardware platform project.

Finally, the application becomes yet another project and contains the source files, linker script, compiler options, etc. necessary for running the software. The application project is dependent upon a BSP project.

Multiple projects of any type can exist in the workspace. For this lab, *SDKintro\_app* is the application, the *SDKintro\_app\_bsp* project is the BSP that contains all of the supporting software that bridges the hardware to the application software, and the *SDKintro\_hw* project is the description of the hardware platform.

Figure 3-12: Project Explorer Tab

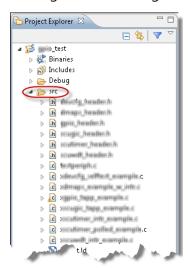

**2-2-10.** Expand **SDKintro\_app** > **src** to see all of the source files that are part of this project by clicking the ▷ or ⊞ sign next to src.

Figure 3-13: Expanding the Application Sources Structure

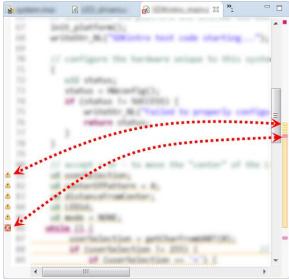

With the new sources added to the project, the SDK tool will automatically compile all the files in the project. Since errors was deliberately introduced into the source code, your next task is to locate and correct these errors.

2-3. Locate the first error and correct it.

There are several ways to locate errors. You will use one method to locate and correct this first error and another process to locate and correct the second error.

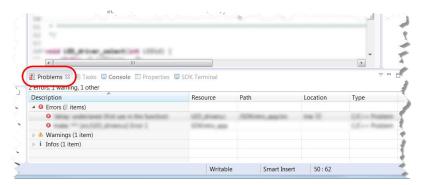

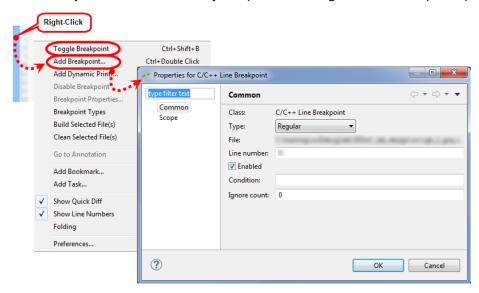

2-3-1. Locate the **Problems** tab.

Figure 3-14: Locating the Problems Tab

This tab is found at the bottom of the workspace.

**2-3-2.** Double-click the first error '*delay*' *undeclared (first use in this function)* to both open the file that contains this error and identify the line where the error occurred.

Notice the two small icons in the margin ( and ). These indicate errors and warnings.

**2-3-3.** Hover the mouse over each of the icons to activate the pop-up message describing what the warning and error are.

Figure 3-15: Accessing the Pop-Up Description for the Warning and Error

The error icon shows that something in this line is not defined. The description in the Problems tab clarifies this and tells you that 'delay' has not been declared.

| Question 1                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------|

| What action might you take to resolve this issue?                                                                       |

|                                                                                                                         |

|                                                                                                                         |

| Certain types of problems can <i>propagate</i> from an error or warning to others.                                      |

| Question 2                                                                                                              |

| What is the best way to investigate and correct this error?                                                             |

|                                                                                                                         |

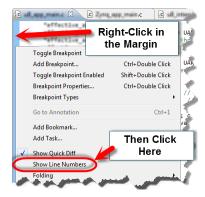

|                                                                                                                         |

| Question 3                                                                                                              |

| Unfortunately, the default for the SDK editor is to have line numbering turned off. How can you turn on line numbering? |

|                                                                                                                         |

|                                                                                                                         |

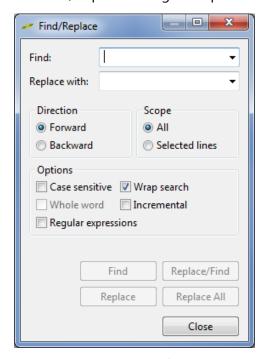

- **2-3-4.** Change **dely** to **delay** on the line prior to the error (on or about line 49).

- **2-3-5.** Select **File** > **Save** (or press <**Ctrl** + **S**>) to save your changes.

Saving the file also causes the rebuilding of the file. This is a customizable feature and can be disabled.

## **Question 4**

What happened as a result of the recompilation of the file? **Hint:** Look at the Problems tab.

2-4. Locate and correct the second error.

While you could follow the same procedure described in the previous instruction, you will use this second error to explore an alternate means of performing the same task. One method is just as good as the other—this will simply become your preference.

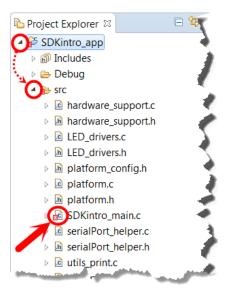

- **2-4-1.** Expand **SDKintro\_app** > **src** under the Project Explorer tab.

- **2-4-2.** Locate the file icon with an error marker (🖆).

Figure 3-16: Locating a Source File Containing an Error

**2-4-3.** Double-click the file name to open it in the editor.

**2-4-4.** Look closely at the right margin to notice a series of small red and yellow rectangles.

Figure 3-17: Mapping Error and Warning Icons to the Error and Warning Navigation Bar

## **Question 5**

What do you think these small red and yellow rectangles mean?

**2-4-5.** Click the topmost red rectangle in the right margin to change the view to show the offending line of code.

Visual inspection quickly shows that the closing parenthesis was omitted from the *while* statement.

**2-4-6.** Insert the closing parenthesis on (or about) line 86 so that it appears as follows:

## **Question 6**

What happens as soon as you add the closing parenthesis?

**2-4-7.** Select **File** > **Save** (or press <**Ctrl** + **S**>) to save the code to preserve your changes and recompile the source code.

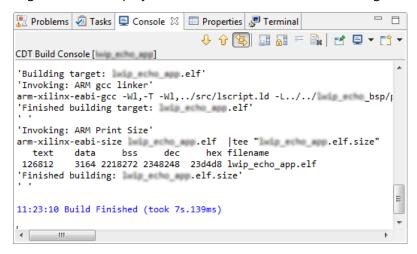

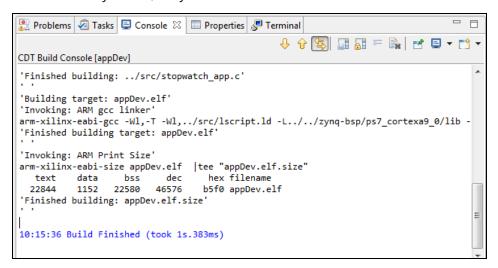

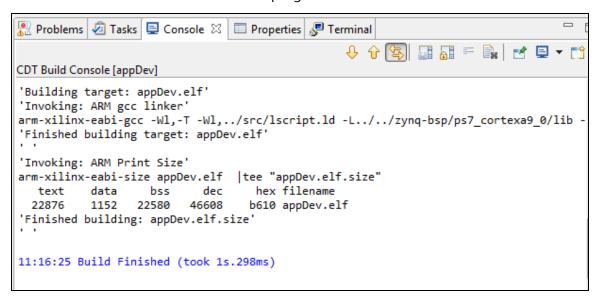

A successful build will show no errors in the Problems tab (although there might be warnings) and is indicated in the Console tab when the sizes of all of the program segments are displayed before the *Build Finished* message.

Figure 3-18: Successful Software Application Build (Your File Names and Sizes Will Vary)

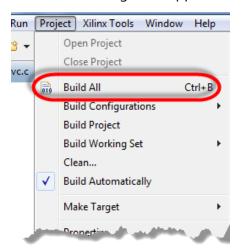

Sometimes you want to confirm that everything has built properly and you want to "force" everything to be rebuilt.

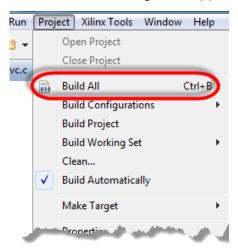

## 2-5. Force a recompilation of your entire project.

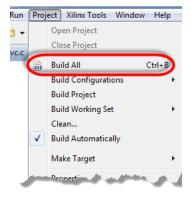

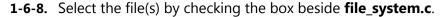

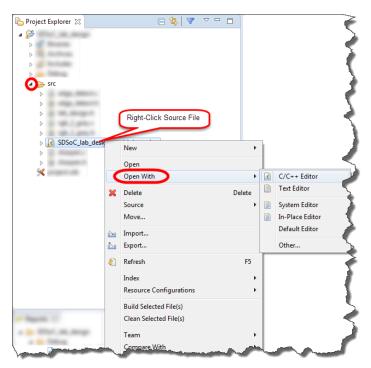

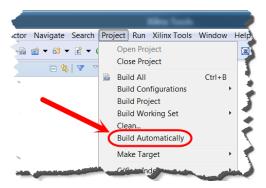

**2-5-1.** Select **Project** > **Build All** to rebuild the entire project.

You will be able to monitor the progress in the Console tab and in a pop-up status bar.

The Outline tab (view) is the result of the tools scanning the source code and mapping where a number of different elements are located. These elements include:

- #define

- #include

- Global variable declarations

- Function definitions

This list is filterable so that searching can be simplified for large and complex sources.

| 2-6. | Use the Outline view to answer the following questions. |

|------|---------------------------------------------------------|

| Ques | tion 7                                                  |

| How do you use the Outline view?                                                                               |

|----------------------------------------------------------------------------------------------------------------|

|                                                                                                                |

|                                                                                                                |

| Question 8                                                                                                     |

| What line number does the LED_driver_select(int) function begin on? (Located in LED_drivers.c)                 |

|                                                                                                                |

|                                                                                                                |

| Question 9                                                                                                     |

| What happens if you click a different source tab?                                                              |

|                                                                                                                |

|                                                                                                                |

| <b>2-6-1.</b> Select the <b>SDKintro_main.c</b> source to to make it active.                                   |

| 2-6-2. Using the Outline view, locate the include for <i>utils_print.h</i> .                                   |

| <b>2-6-3.</b> Select <b>utils_print.h</b> in the Outline view to locate the <i>include</i> in the source file. |

| Question 10                                                                                                    |

| What is the easiest way to open <i>utils_print.h</i> ?                                                         |

|                                                                                                                |

|                                                                                                                |

| Question 11                       |  |  |

|-----------------------------------|--|--|

| What else turns into a hyperlink? |  |  |

|                                   |  |  |

|                                   |  |  |

|                                   |  |  |

## **Configuring the Serial Port and Running the Application**

Step 3

You will now take the final step and download the ELF file to the hardware and monitor the output of the system.

Begin by powering up the board and initiating a serial communications session.

## 3-1. Apply power to the board.

- **3-1-1.** Switch the board to OFF to clear memory if your board is powered on and has a power slide switch; otherwise, remove the power cable.

- **3-1-2.** Ensure that you have a correctly imaged SD card if you are using the MicroBlaze™ processor.

The correct SD card images are available from *C*:\training\SDK\_Driver\support\

TransUartPins48-49\_BootImage\[ZC702 | ZED]. Copy the BOOT.bin to the root of the SD card.

**3-1-3. MicroBlaze processor users only:** Insert the SD card into the development board.

This will configure the PS with a special application to allow UART communications with the MicroBlaze processor through the PS.

**Note**: You may have to change the jumper/switch settings to support JTAG programming. Many devices, such as the Zynq®-7000 family support JTAG fallback if the jumpers/switches are set to SD card and no card is present. Other families, such as the Zynq UltraScale+™ family, need to be specifically configured to boot from JTAG or SD Card. Refer to the lab setup guide for your board for details.

**3-1-4.** Slide the switch on your board to the ON position if it has one (as shown in the lab setup guide for your board); otherwise, plug the power cable in.

You will need to verify the proper connections and open a terminal window on the PC to monitor the output of the application. You may need to change the assigned COM port based on your computer's configuration.

3-2. If you are not certain on how to properly connect your board to the PC and power it up, refer to the Board-Specific Tasks section in the *Lab Reference Guide*.

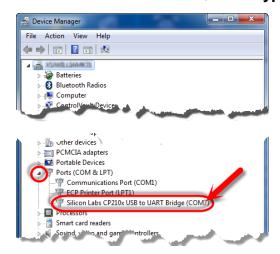

If you do not recall how to determine the COM port that is connected to the board, refer to the "Determining the COM Port Assigned by the USB Driver" topic under the Board, OS, COM, and IP Address Tasks section in the *Lab Reference Guide*.

If you need further assistance with either of these tasks, ask your instructor.

The SDK terminal is an interface that only supports serial port/UART communications. The more general Terminal tab is able to support other formats, such as SSH and Telnet.

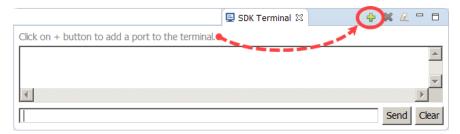

- 3-3. Locate the SDK Terminal tab. Generally this tab is found in the same panel as the console.

- **3-3-1.** Select **Window** > **Show View** > **Other** > **Xilinx** > **SDK Terminal** to open the SDK Terminal tab if it is not currently visible.

This tab typically opens in the same window as the console.

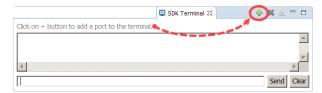

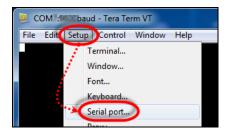

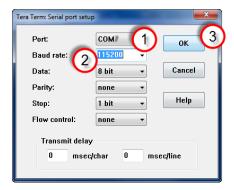

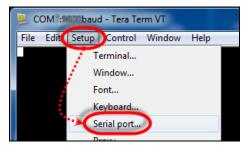

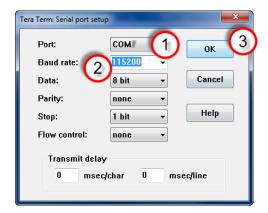

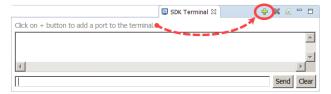

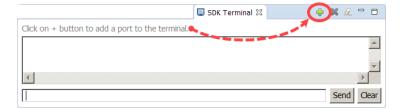

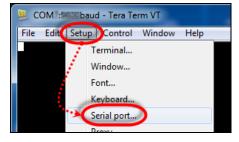

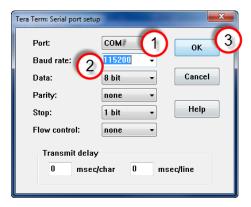

## 3-4. Configure the SDK Terminal.

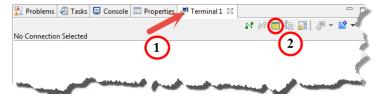

**3-4-1.** Click the green '+' sign to open the Connect to Serial Port dialog box.

Figure 3-19: Adding/Associating a Port to the Terminal

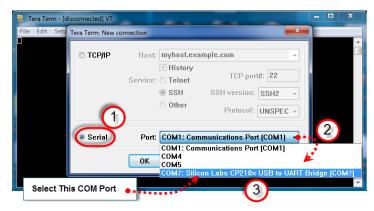

A pop-up appears asking you to configure the settings for the serial port.

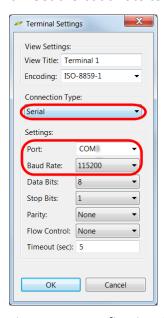

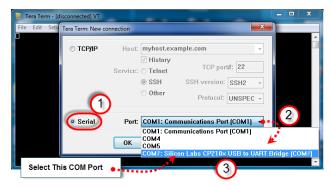

**3-4-2.** Select the serial port that is connected to the device you want to communicate with (1).

This is the port number associated with the Serial Port/USB connection from your board. This is often the highest-numbered com port, but not always. Your board must be powered on in order to see this port.

- **3-4-3.** Set the baud rate to **115200** (2).

- **3-4-4.** Leave the other settings at their defaults.

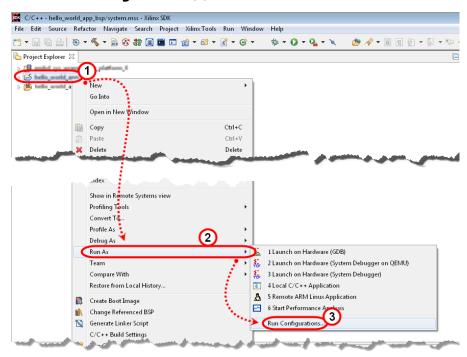

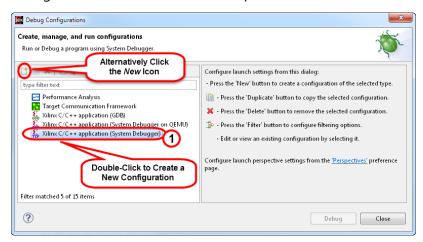

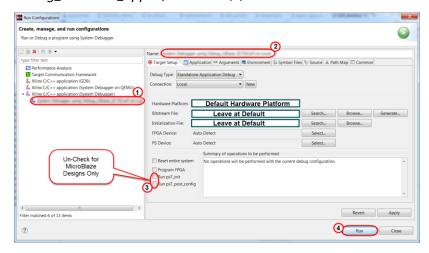

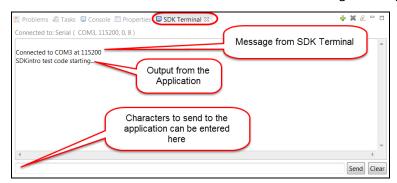

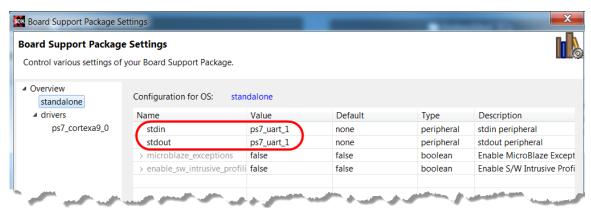

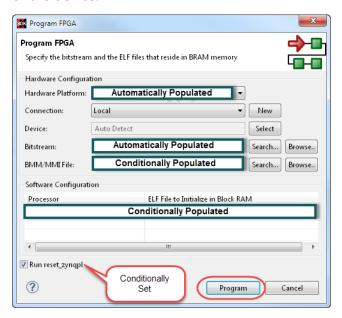

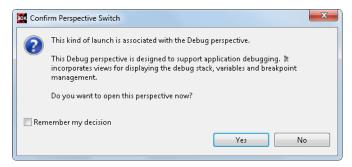

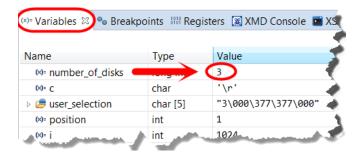

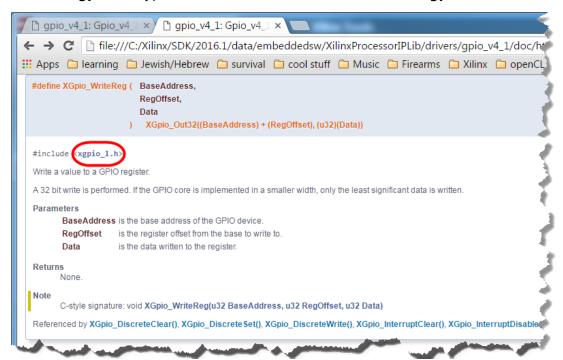

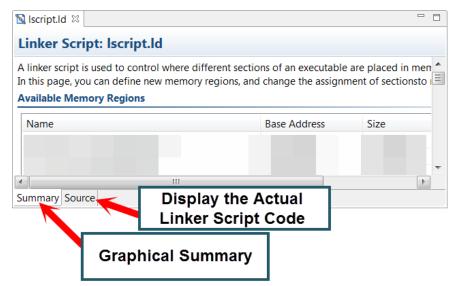

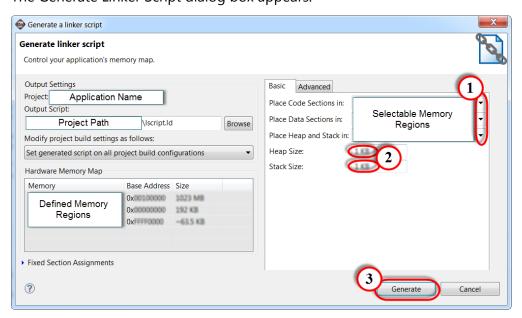

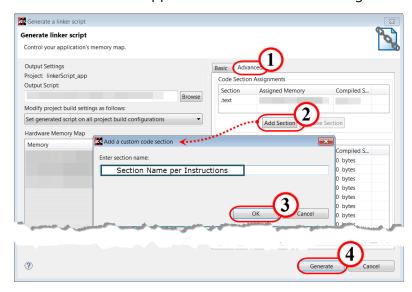

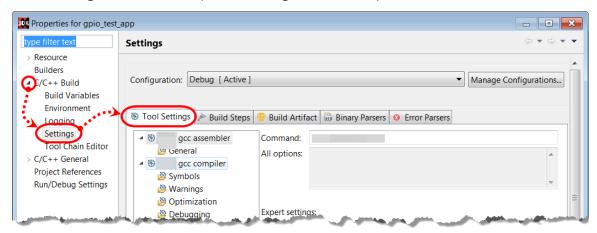

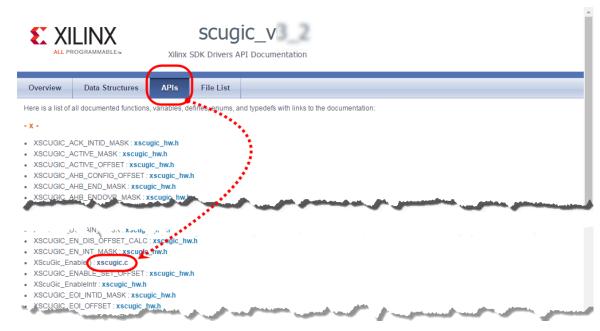

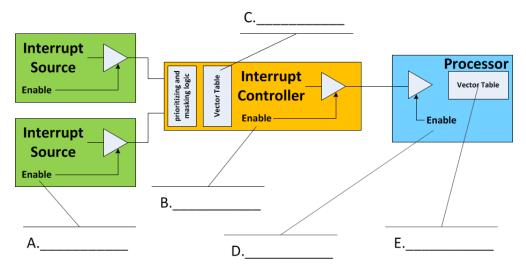

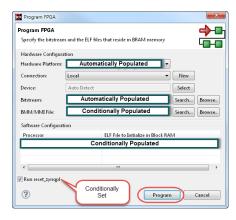

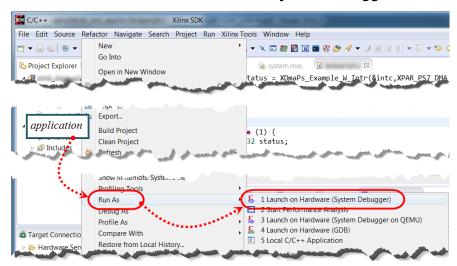

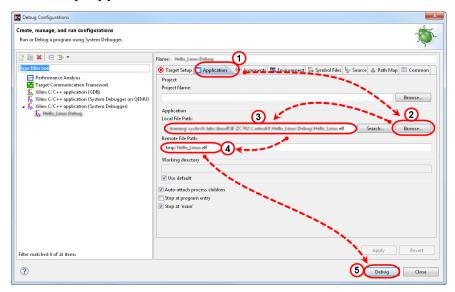

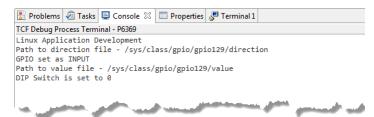

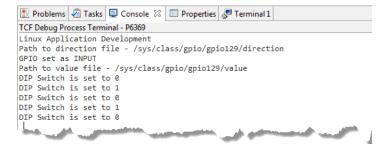

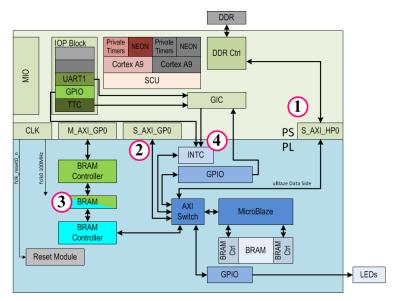

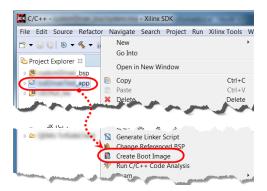

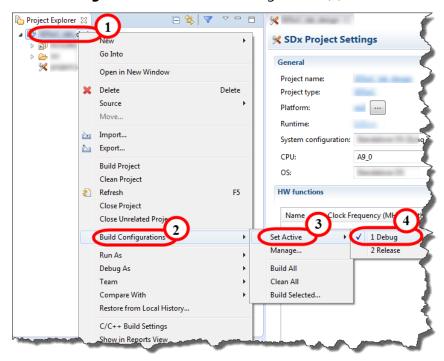

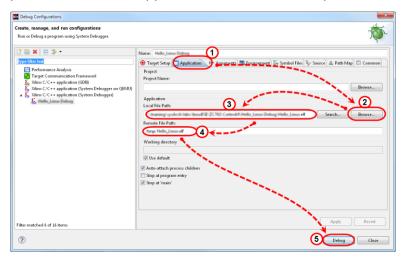

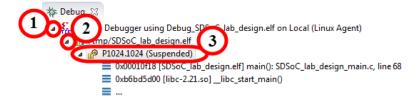

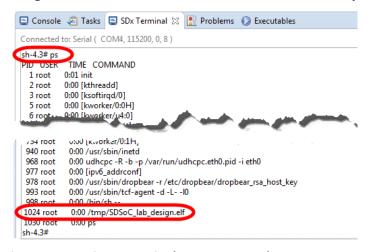

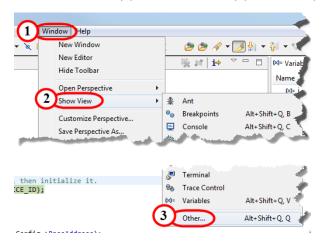

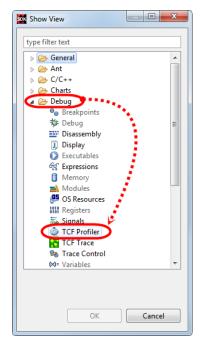

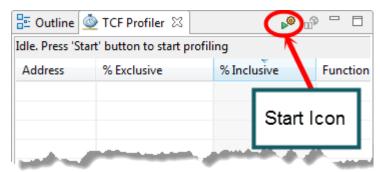

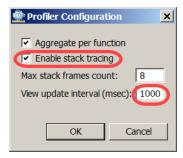

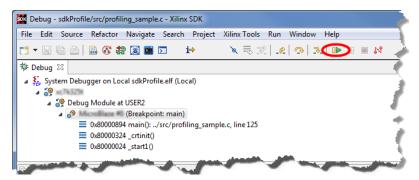

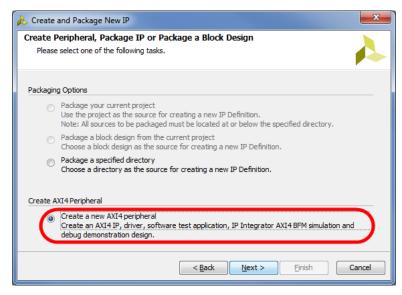

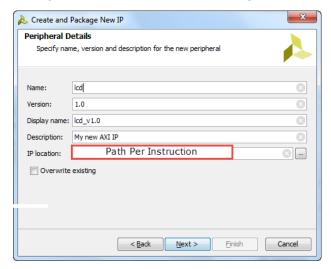

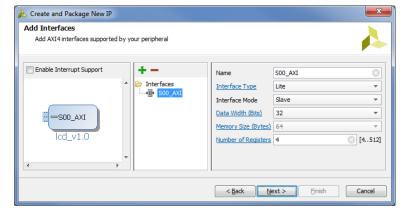

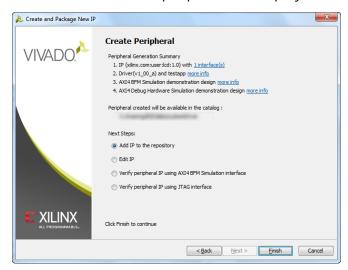

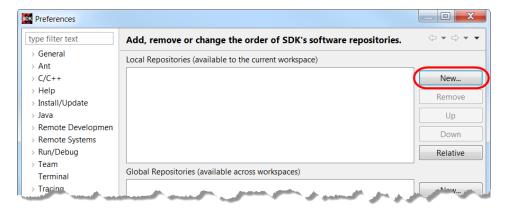

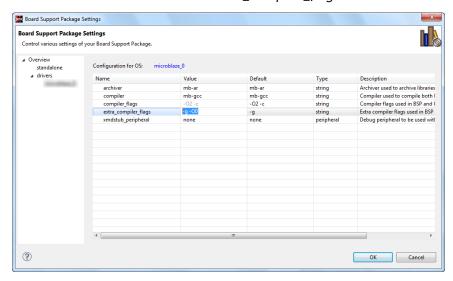

Figure 3-20: Configuring the SDK Terminal