Overview

Emulation and prototyping with adaptive SoCs and FPGAs enable fast and accurate SoC system modeling and verification as well as accelerated software and firmware development.

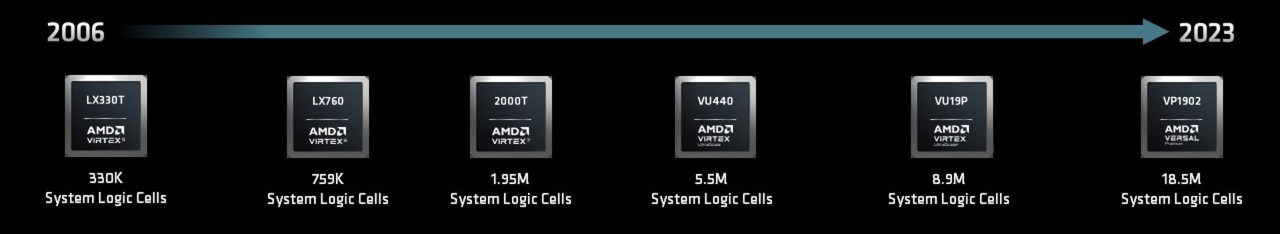

AMD has a proven track record of leading the industry in emulation and prototyping solutions for over 17 years.

Six Generations of Leadership in Hardware-Assisted Verification

Industry’s Highest Capacity Adaptive SoC

- AMD has delivered six generations of the world’s largest adaptive SoC1

- Enables industry solutions with up to 2X the capacity2 and 2X the performance3 compared to prior generations

Advanced Design Visibility and Debug Capability

- Enhanced debug hardware capabilities to shorten design verification cycles

- Continued investment in debug tools and IP for performant design visibility

Compile Tools Built for Emulation and Prototyping

- Vivado™ ML machine learning enhanced reporting and iterative design runs help maximize developer productivity

- Vivado next-generation place-and-route features scale to ever larger FPGAs with significant improvements to QoR and compile time

applications

Emulation and Enterprise Prototyping

Enables large, high-performance emulation and enterprise prototyping platforms

- High capacity for large ASICs

- Simulation acceleration

- Software stack and system validation

- Cloud deployment

Traditional and Desktop Prototyping

Provides an extensive debug and IP ecosystem for traditional, desktop, and IP prototyping

- IP block and subsystem prototyping

- In-circuit peripheral validation

- Firmware development and test

- Digital twins

featured product

Versal™ Premium VP1902 Device: World’s Largest Adaptive SoC4

- 2X higher logic density2 compared to the Virtex™ UltraScale+™ VU19P device

- 2X aggregate I/O bandwidth5 and 2.3X transceiver bandwidth6 for scalability

- Reduced I/O latency and two-by-two SLR array for improved system performance

- Based on AMD internal analysis, May 2023. (VER-009)

- Based on AMD internal analysis in May 2023, comparing the number of system logic cells of the Versal Premium VP1902 device versus the Virtex UltraScale+ VU19P device. (VER-001)

- Based on AMD internal system clock performance analysis in May 2023, comparing the Versal Premium VP1902 device to the Virtex UltraScale+ VU19P device across a range of design sizes and cut nets. (VER-006)

- Based on AMD internal analysis in May 2023 with a 6-input LUT count to compare the Versal Premium VP1902 device versus the Intel Stratix 10 GX 10M FPGA. (VER-002)

- Based on AMD Labs testing using an A6865 package to simulate the XPIO data rate performance of an AMD Versal Premium VP1902 device versus the published data rate of an AMD Virtex UltraScale+ VU19P FPGA. Actual results will vary. (VER-003)

- Based on AMD Labs calculation in May 2023 of aggregate transceiver bandwidth of a Versal Premium VP1902 device B6865 package versus a Virtex UltraScale+ VU19P device B3824 package, assuming GTY/GTYPs running at 32G and GTMs running at 56G. (VER-005)