高位設計

高位設計フローの特長

ここでは、高位設計を効率化するための Vivado™ ML 機能について簡単に説明します。タブをクリックすると、各機能の説明を表示できます。

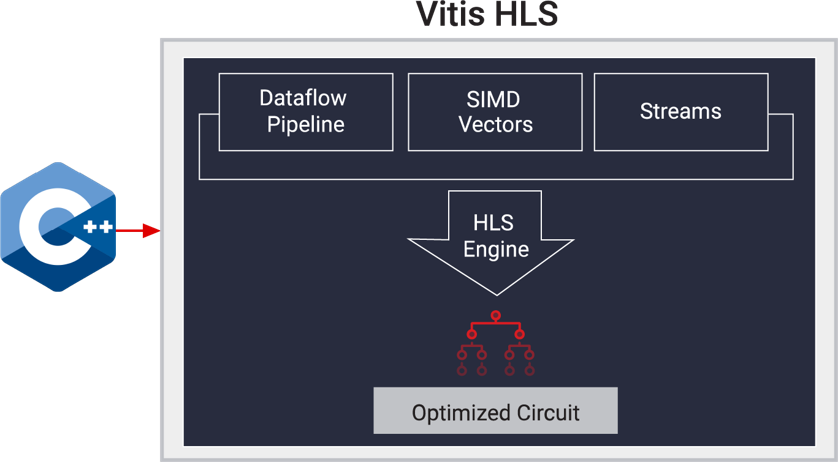

Vitis 高位合成 (HLS) ツール

近年、AI、ワイヤレス、医療、防衛、および民生用アプリケーションで使用されている高度なアルゴリズムは、従来に比べてはるかに高機能化されています。すべての Vivado Edition の無償アップグレードに含まれている Vitis™ 高位合成により、移植可能な C++ 仕様を RTL を作成せずに直接 AMD デバイスをターゲットにできます。Vitis HLS ツールは、Vitis と Vivado の両方の設計環境をサポートしているため、ソフトウェアおよびハードウェアの設計者は効率的にカーネルや IP を設計できます。

- アルゴリズム記述、データ型の仕様 (整数、固定小数点、浮動小数点)、およびインターフェイス (FIFO、メモリ、AXI4) の抽象化

- 任意精度データ型、ストリーム、およびベクトル化されたデータ型のビルトイン サポートを提供する広範なライブラリ

- 指示子で駆動される、アーキテクチャを認識した合成機能を使用することで高 QoR を実現

- 手作業でコード化した RTL に匹敵する QoR を迅速に生み出す

- C/C++ テストベンチ シミュレーションを使用する迅速な検証、自動の VHDL/Verilog シミュレーションおよびテスト ベンチ生成

- AMD のオンチップ メモリ、DSP エレメント (浮動小数点タイプを含む) を自動的に使用

ライブラリ

Vitis HLS ツールには、次のライブラリが含まれています。

| 名称 | 説明 |

|---|---|

任意精度データ型 |

整数および固定小数点 (ap_int.h) タイプ |

HLS ストリーム |

ストリーミング データ構造用のモデル。最高のパフォーマンスとエリアの達成を目的とする (hls_stream.h) |

ベクトル型 |

ベクトル化された型と演算 (hls_vector.h)、任意精度型を含む |

HLS Math |

標準 C (math.h) および C++ (cmath.h) Math ライブラリの合成をサポート。 浮動小数点型と固定小数点型の関数をサポート: abs、atan、atanf、atan2、atan2、ceil、ceilf、copysign、copysignf、cos、cosf、coshf、expf、fabs、fabsf、floorf、fmax、fmin、logf、fpclassify、isfinite、isinf、isnan、isnormal、log、log10、modf、modff、recip、recipf、round、rsqrt、rsqrtf、1/sqrt、signbit、sin、sincos、sincosf、sinf、sinhf、sqrt、tan、tanf、trunc |

Vitis HLS ツールは、Github で入手できるパフォーマンスに最適化された Vitis ライブラリもサポートしています。これらのライブラリを利用することで既存のアプリケーションに最小限のコード変更を加えるだけで (場合によっては変更を加えずに)、すぐに高速化を実現できます。一般的な Vitis アクセラレーション ライブラリには、高度な計算、統計、線形代数、および DSP などがあり、幅広いアプリケーションに役立つ重要な機能を提供します。これらのライブラリは、OpenCV を使用したビジョンや画像処理、数理ファイナンス、データベース、データ分析、データ圧縮などのワークロードを高速化します。

詳細は、Vitis HLS のサイトをご覧ください。

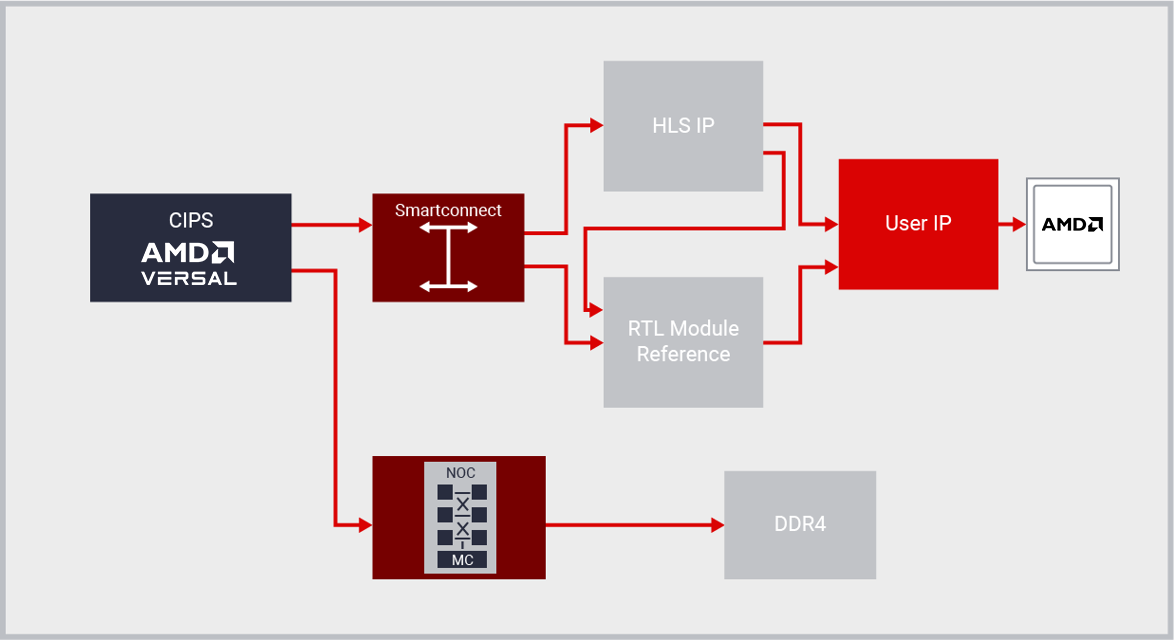

IP インテグレーター

Vivado™ ML エディションは、業界初のプラグアンドプレイ IP を使用する統合設計環境を提供し、その IP インテグレーター機能を活用することによって、RTL デザインの限界を超える優れた生産性をもたらします。

Vivado IP インテグレーターは、グラフィカルおよび Tcl ベースで、検証しながら開発を進めることができるデザイン開発フローを提供します。この機能は、主要 IP インターフェイスの自動接続、ワンクリックでの IP サブシステム生成、リアルタイム DRC、インターフェイス変更伝搬、そして高性能デバッグ機能の併用をサポートする、デバイスとプラットフォームに対応できる対話型の環境です。

設計者は、IP 間の接続を実行する際に信号レベルの抽象化ではなく、インターフェイス レベルで対応できるため、生産性が劇的に向上します。多くの場合、AXI4 インターフェイス規格を使用しますが、IP インテグレーターでは、その他にもさまざまなインターフェイスがサポートされています。

インターフェイス レベルで作業を進められるため、設計チームは、Vitis HLS や Model Composer、AMD SmartCore™、LogiCORE™ IP、アライアンス メンバー IP、またはユーザー独自が開発した IP を利用する複雑なシステムをすばやく組み立てることができます。Vivado の IP インテグレーターおよび HLS 機能を組み合わせて利用することによって、RTL デザインより最大 15 倍の開発コスト削減が可能です。

Vivado IP インテグレーターの主な機能と利点

- IP インテグレーターの階層的サブシステムをデザインにシームレスに統合

- IP インテグレーター デザインをすばやく統合して再利用のためにパッケージ化

- グラフィカルおよび Tcl ベースのデザイン フローをサポート

- 迅速なシミュレーションおよび複数のデザイン ビューでクロスプロービングが可能

- プロセッサを使用するデザインおよびプロセッサなしのデザインをサポート

- アルゴリズムの統合 (Vivado HLS および Model Composer) および RTL レベル IP の統合

- DSP、ビデオ、アナログ、エンベデッド、コネクティビティ、およびロジックの組み合わせ

- DFX フロー ベースのプロジェクトをサポート

- デザイン アセンブリ中に複雑なインターフェイス レベルの接続に対して DRC を実行

- 一般的な設計エラーの検証および修正

- 相互接続された IP へパラメーターを自動的に伝搬

- システム レベルの最適化

- 自動化された設計アシスト機能

- ブロック デザイン コンテナーを用いたチームベースの設計により、再利用性とモジュール設計を実現

- ソース ファイルと生成ファイルを分けることでリビジョン管理が改善

- 2 つのブロック デザインを比較するための Block Design Diff ツール

Vitis 高位合成と Vitis Model Composer を使用する C ベースの IP 生成

AMD のプログラマブル ソリューション向け ESL (電子システム レベル) デザイン ツールの Vivado では、C、C++、SystemC 用の Vitis™ 高位合成を提供しております。DSP 用の Vitis Model Composer をアドオンで購入可能です。これらのソリューションでは、高級言語で記述された IP 仕様を VHDL や Verilog に直接合成できるため、IP の検証時間が 100 倍以上高速化し、RTL 変換は最大 4 倍高速化します。密接に統合されたツールは、個々に、または Vivado ML で使用される再利用可能な IP と組み合わせて利用できます。

Dynamic Function eXchange (DFX)

DFX とは特定のロジック ブロックを動的に変更する機能であり、その他のロジックの動作を続けながら、パーシャル プログラム イメージをダウンロードできます。AMD DFX テクノロジでは、オンザフライで機能を変更できるため、すべてのリンクを再び設定して確立する必要がなくなり、FPGA および SoC の柔軟性を最大限に活用できるようになります。これは、プラットフォーム ベースのデザイン フローの設計で有効です。Dynamic Function eXchange を使用することで、デバイス数を少なくしたり、小規模デバイスへ移行でき、消費電力の削減とシステム強化が可能になります。必要なときにいつでも必要な機能をロードできるため、シリコンをより効果的に使用できます。

Dynamic Function eXchange ソフトウェア

FPGA または SoC 全体の動作を継続したまま、一部分をリコンフィギュレーションするために、Vivado™ Design Suite ソフトウェア ツールが機能のロックを解除します。この最新ソリューションは、Vivado Design Suite の優れたインプリメンテーション機能を利用して、リコンフィギュレーション可能なデザインの構築にかかる負担を軽減します。ユーザーは、Tcl ベースの非プロジェクト フロー、または RTL/IP ベースのプロジェクト フローを使用してデザインを実装できます。Vivado IP インテグレーター (IPI) のデザイン サポートにより、置き換え可能なブロック デザインを使用してデザインをセグメント化し、ブロック デザイン コンテナーを使用することで DFX が可能になります。Vivado IDE 内では、RTL および IP ベースのプロジェクト モードがサポートされており、基本的なフローの詳細は自動的に管理されます。設計フローのエントリ ポイントには、Vitis™ 統合開発環境 (IDE) の HLS で処理される高水準言語が使用されます。ダイナミック領域を低次領域に細分化できる Nested DFX (UltraScale™ および UltraScale+™) や、インプリメンテーション ツール フローを効率化してランタイムを大幅に向上させる抽象化シェル (UltraScale+ および Versal™) などの高度なフロー機能も利用できます。

設計者が DFX デザインをより迅速かつ簡単に構築できるように、4 つのコアを提供しています。Dynamic Function eXchange Controller は、ハードウェア ベースのコンフィギュレーション コントローラーであり、トリガーやアービトレーションからビットストリーム作成やエラー処理に至るまで、AMD FPGA 内のリコンフィギュレーションに関するすべての側面を管理できます。Dynamic Function eXchange Decoupler は、DFX Controller またはその他のカスタマー コントローラーと併用され、リコンフィギュレーションされるダイナミック領域を安全に分離できます。Dynamic Function eXchange AXI Shutdown Manager は、リコンフィギャラブル パーティションを安全に再構成できるように AXI インターフェイス上のアクティビティを中断します。Dynamic Function eXchange Bitstream Monitor は、パーシャル ビットストリームをデバッグおよび監視することによって、バージョンやターゲットの互換性を確保します。

Vivado Design Suite の最新バージョンでは、Versal デバイス向けの DFX サポートが提供されています。サポートされるデバイスは、今後新しいデバイスが追加されるとさらに拡充します。UltraScale+ デバイスのサポートには、プロダクション ステータスのすべてのデバイスが含まれ、新しいデバイスがリリースされるとサポートも拡充します。UltraScale™ デバイスのサポートは完了しており、Vivado Design Suite の最新バージョンでビットストリーム生成まで可能です。ほとんどの 7 シリーズと Zynq™ 7000 デバイス (最小デバイスを除く) は Dynamic Function eXchange に対応していますが、一部の Artix™ 7 デバイスとすべての Spartan™ 7 デバイスは対応していません。詳細は、『Vivado Design Suite ユーザー ガイド: Dynamic Function eXchange』 (UG909) の付録 A 「サポートされるデバイス」を参照してください。

UltraScale アーキテクチャでは、Dynamic Function eXchange (DFX) 技術で新たな進化をもたらし、ほとんどすべての FPGA リソース タイプ (I/O、ギガビット トランシーバー、クロッキング ネットワークなど) のリコンフィギュレーションを可能にしました。UltraScale+ アーキテクチャでは、ビットストリーム転送を強化し、リコンフィギュレーション モードを拡張することによりさらなる機能改善を実現しました。最近では、Versal アーキテクチャのサポートが進み、ソフトウェア ベースのリコンフィギュレーション管理、リコンフィギャラブルな NoC (ネットワーク オン チップ)、共有メモリ アクセス、フロアプランの精度と効率化が追加されています。

大学教授および研究員の方は、AMD ユニバーシティ プログラムから各バージョンの Vivado ソフトウェア ライセンスを入手可能です。すべての Vivado Edition には Dynamic Function eXchange が含まれていますが、古いバージョン (2019 よりも前) では DFX ライセンスが必要になります。ライセンス取得に必要な要件および手続きの詳細は、aup@amd.com まで電子メールでお問い合わせください。

主な機能と利点

- Vivado IDE は、HDL からビットストリーム生成までの Tcl ベースの非プロジェクト フローと RTL および IP インテグレーター プロジェクト モードをサポート

- スタティック/リコンフィギャラブル モジュールのデータベースを効率的に管理

- 不完全なモジュールを削除できるブラック ボックス ビットストリームをサポート

- ユーザーがリコンフィギャラブル モジュール イメージの転送を管理する

- モジュールが追加/削除される間、メモリ内でスタティック デザインをオープンにする

- フロアプラン機能で、リコンフィギュレーションされるリソースを判断

- ツールがパーティション インターフェイスを自動管理 (オーバーヘッドが不要)

- デザイン ルール チェック (DRC) がデザイン構造やコンフィギュレーションを検証

- 標準のタイミング クロージャ技術が適用される

- バージョン 2019.1 以降、Vivado WePack Edition を含むすべての Vivado Design Suite エディションに Dynamic Function eXchange 機能が追加費用なしで含まれている

- Versal デバイスのサポートは既に含まれており、今後さらに拡充する

- 7 シリーズのすべてのデバイスがサポートされているわけではない

リソース

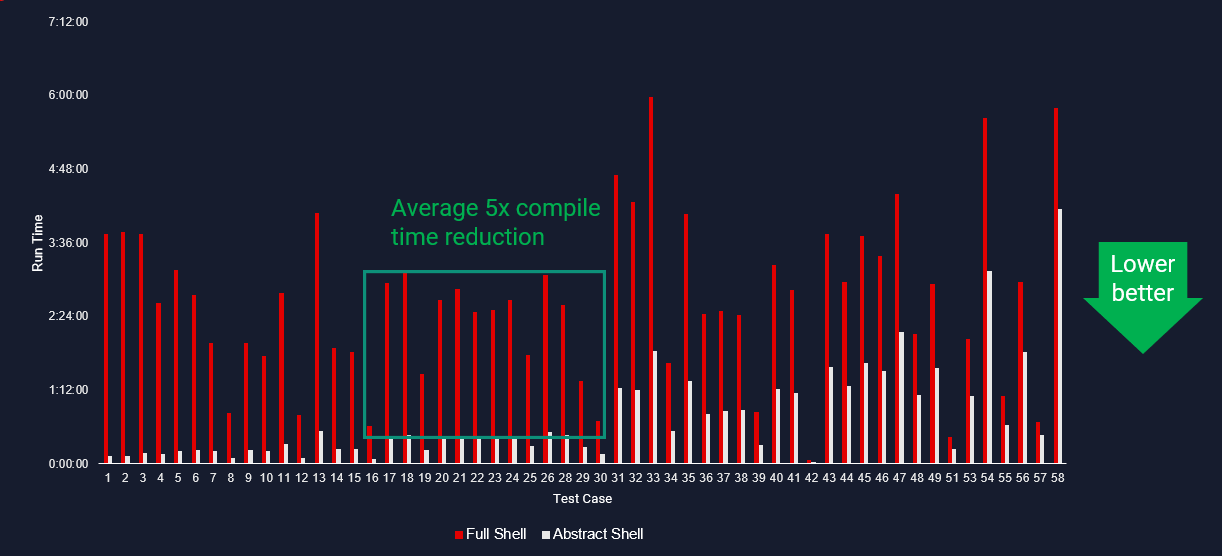

抽象化シェルを使用した高速コンパイル

抽象化シェルは、複雑で大規模なデザインのコンパイルを高速化する新しい技術です。デザイン内のリコンフィギャラブル モジュールを指定して個別にコンパイル可能です。修正が必要な部分のみを選択して再コンパイルできるため、デザイン全体を再コンパイルする必要がありません。

この機能により、従来のコンパイルと比較して、平均 5 倍、最大 17 倍のコンパイル時間短縮が可能になります。またデザイン内の複数モジュールを指定して、同時にコンパイルすることも可能です。

抽象化シェルの利点

- 各リコンフィギャラブル モジュールのコンパイル実行時間およびメモリ使用率を削減

- 複数のリコンフィギャラブル パーティションがある場合、すべてのリコンフィギャラブル モジュールを同時に実行

- スタティック デザイン内の機密情報をすべて隠す

- スタティック デザイン内の IP のライセンス チェックを回避

- 複数のチームでリコンフィギャラブル パーティションを分担し、デザインのコラボレーションが可能

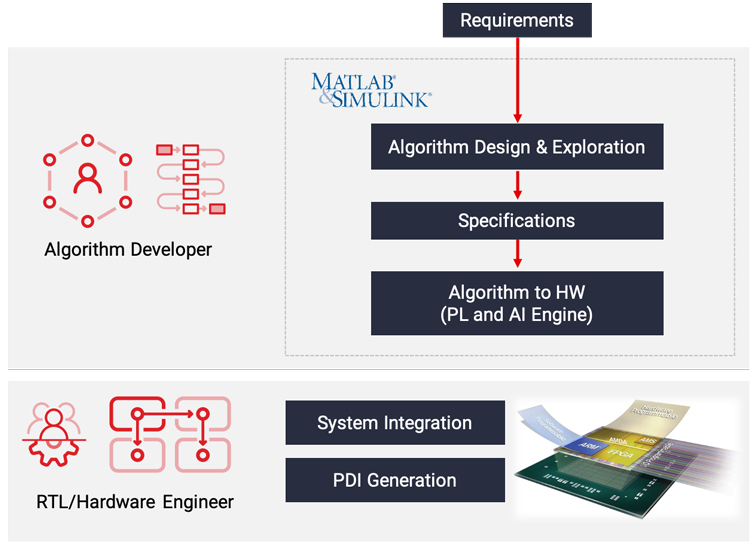

Vitis Model Composer

Vitis™ Model Composer は、MathWorks MATLAB® および Simulink® 環境内での効率的なデザイン探索を可能にするモデルベースの設計ツールで、自動コード生成機能により AMD のデバイスをベースとする迅速な製品化をサポートします。アルゴリズムを設計し、それらをパフォーマンス重視で最適化されたブロックを使用して反復し、システム レベル シミュレーションで論理的に正しいかどうかを検証できます。Vitis Model Composer は、自動最適化機能によってデザインをプロダクション品質のインプリメンテーションに変換します。このツールには、200 を超える HDL、HLS、AI エンジン (AIE) ブロックを含むライブラリが含まれており、AMD デバイスでのアルゴリズムの設計および実装を可能にします。また、カスタムの HDL、HLS、AI エンジン コードをブロックとしてツールにインポートすることも可能です。Vitis Model Composer には、2020.2 以降、スタンドアロン ツールとして提供廃止となった AMD の System Generator for DSP の機能がすべて含まれています。

Vitis Model Composer では、次のことが可能になります。

- AI エンジンとプログラマブル ロジックをターゲットとする最適化されたブロックを使用してデザインを作成する。

- シミュレーション結果を視覚化して分析し、MALTAB® および Simulink® を使用して生成されたゴールデン リファレンスと出力を比較する。

- AI エンジン ブロックとプログラマブル ロジック (HLS、HDL) ブロックの協調シミュレーションをシームレスに実行する。

- デザインのコード (AI エンジンのデータフロー グラフ、RTL、HLS C++) とテストベンチを自動生成する。

- カスタマイズした HLS、AI エンジン、RTL コードをブロックとしてインポートする。

*注記:

Vitis Model Composer は、Vivado ML のすべてのエディションでアドオン ライセンスとして購入できます。

ダウンロードと購入についての詳細は、Vitis Model Composer をご覧ください。

主な特長

- 高位記述: アルゴリズムを中心とする機能重視の構築ブロックを利用することで、簡単にデザインを模索できるようになります。

- ベクトルと行列をサポート: フレーム ベースのアルゴリズム設計が可能になるため、実装のために中間の低レベル モデルに移行する時間と労力を削減できます。

- アプリケーション特定ライブラリ: パフォーマンスに最適化されたコンピューター ビジョン、演算、および線形代数ライブラリが、AMD のデバイス上でのシミュレーションおよび高性能実装用ブロックとして提供されています。

- カスタム ブロックとして合成可能な C/C++ ブロックをインポート: シミュレーションやコード生成のために独自のカスタム ブロックを作成できるため、差別化されたアルゴリズム設計が柔軟になります。

- Simulink とのシームレスな統合: Simulink 製品ファミリのブロックと直接接続することで、システム レベルのモデリングやシミュレーションが可能になり、Simulink のグラフィカル環境のスティミュラス生成やデータ視覚化機能をフルに活用できます。

- 整数、浮動/固定小数点をサポート: Simulink でサポートされている浮動小数点/整数データ型および Vivado HLS でサポートされている固定/半精度データ型をサポートしています。

- 自動最適化: Simulink 内でアルゴリズム仕様を分析し、自動最適化を実行してマイクロアーキテクチャに変換します。スループットが最適化され、ブロック RAM の使用率が削減し、ブロックの同時実行が可能になります。

- IP 作成が迅速化: シミュレーション可能なデザインを Vivado IP インテグレーターで使用できる RTL IP パッケージに変換することで、プラグアンドプレイ IP 統合設計環境を活用して複雑なデザインに対応できます。

- System Generator for DSP の利用: Model Composer の使いやすさとシミュレーション速度の利点を生かして、一部のデザインの合成済み RTL を新しいカスタム ブロックとして既存の System Generator for DSP デザインにエクスポートします。

- Vivado HLS へエクスポート: シミュレーションで出力されるテスト ベクターの記録など、アルゴリズムのさらなる最適化に必要なものをすべて自動生成し、アルゴリズムの設計/シミュレーション/検証用の Simulink グラフィカル環境と Vivado HLS 間を関連付ける高度な機能です。

- RTL インターフェイスにマッピングするためのユーザー インターフェイス: 実装用にサポートされている RTL インターフェイス (AXI4-Lite、AXI4-Stream、AXI4-Stream Video、FIFO、ブロック RAM) やビデオ フォーマット (AXI4-Stream Video) にユーザー デザインの入力や出力をマッピングするための使いやすいグラフィカル インターフェイスです。

- テストベンチの自動生成: シミュレーションからテスト ベクターを自動記録し、実行可能なデザインと生成されたコードの機能的な同等性を検証するためのテスト ベンチを自動生成します。

資料

機能カテゴリやワークロードで目的の資料を検索および条件検索

ビデオ

ビデオの検索および条件検索