- Devices

- FPGAs & 3D ICs

- Artix UltraScale+ FPGA Family

Artix™ UltraScale+™ FPGA Family

Cost- and Power-Optimized FPGAs with Exceptional Performance/Watt

Product Advantage

Artix™ UltraScale+™ devices are cost-optimized FPGAs based on an advanced, production-proven 16nm architecture for exceptional performance/watt. Devices are enhanced with packaging innovation for ultra-compact form factor and compute density.

With up to 16Gb/s transceivers for advanced protocols and the highest FPGA DSP performance against competitive FPGA products, Artix UltraScale+ FPGAs match I/O bandwidth to compute to help maximize system performance for cost-sensitive and low-power applications in machine vision, networking, 4K broadcast, and a range of Industrial IoT and edge markets.

Key Features & Benefits

Ultra-Compact Packaging

Artix UltraScale+ FPGAs are the industry’s only FPGA available in Integrated Fan-Out (InFO) for small form factor packaging. 70% smaller and 73% thinner than chip-scale packaging, Artix UltraScale+ FPGAs with InFO packaging deliver leading compute density, including serial I/O bandwidth and DSP compute/mm2. InFO packaging also improves thermal and power distribution, flight times, and signal integrity.

Serial I/O Performance

Artix UltraScale+ FPGAs offer up to 16Gb/s transceivers for advanced and emerging protocols in networking, video, and vision. Standards support includes PCIe® Gen4, 10GE Vision, CoaXPress 2.1, and 12G-SDI. The production-proven transceiver architecture includes power optimizations over 7 series FPGAs and equalization technology for optimal signal integrity.

DSP Compute

Advanced FPGA DSP architecture in a cost-optimized device, Artix UltraScale+ DSP slices are optimized for both fixed- and floating-point computation, supporting diverse forms of compute for image and video processing, real-time control, wireless processing, and AI inference. The family offers 2.3X DSP compute compared to Artix 7 FPGAs and at least 2X DSP compute compared to competing FPGA offerings.

Safety and Security Features

Multi-level security features help Artix UltraScale+ FPGAs maintain cybersecurity and IP protection. The architecture provides RSA-2048 Authentication, NIST-certified AES-CGM Decryption, DPA countermeasures, anti-tamper configuration, security monitor IP to adapt as security threats change across the product’s lifecycle.

MIPI and LVDS Performance

A cost-optimized FPGA in the industry that offers up to 2.5Gb/s of MIPI performance, the Artix UltraScale+ family supports advanced camera sensor capture and display. Complete MIPI IP and reference design solutions are also available here. The family’s LVDS performance also enables a range of other protocols including SLVS-EC (for CMOS image sensors).

Scalability

Production-proven UltraScale architecture built on TSMC’s 16nm low power FinFET process, allows scalability to Kintex™ UltraScale+ and Virtex™ UltraScale+ families. Developers can leverage the same IP, tool flow, and ecosystem to preserve design investment enabling a reusable platform across a multi-product portfolio.

Artix UltraScale+ FPGA Matches I/O Bandwidth and Compute Density

for Next-Generation, Ultra-Compact, Cost-Sensitive Applications

Machine Vision

With high DSP compute density in its class enabled by InFO small form factor packaging, the Artix™ UltraScale+™ FPGA offers high-speed image processing and video pre-processing for factory automation. 12Gb/s and 16Gb/s line rates ensure support for the latest connectivity standards, including 10GigE Vision and CoaXPress 2.1 in the camera or at the frame grabber, as well as PCIe® Gen3 and Gen4* for high speed x86 CPU communication. High performance SLVS-EC v2.0, MIPI, and sub-LVDS support the latest sensor technology, beyond 150-megapixel resolution. A MicroBlaze™ processor in FPGA fabric enables system management for a robust embedded vision camera.

4K UHD Video Converters (SDI to HDMI)

Artix UltraScale+ FPGA in InFO packaging (11.5x9.5mm) can efficiently implement broadcast-quality 4K60 UHD video pipelines for space-constrained applications, such as mini-converters, cameras, and KVM. Massively parallel DSP ensures scalable real-time video processing for multiple AV channels in a single device, and high-performance connectivity enables bridging between SDI, HDMI, DisplayPort, and 1Gb/10Gb Ethernet for live 4K AV-over-IP streaming.

Secure Networking

Artix UltraScale+ FPGAs are a great fit for cost-optimized Nx10G or 25G systems, enabled by 12Gb/s and 16Gb/s transceivers and optimal transceiver count. A common architecture across mid-range and high-end UltraScale+ families allows developers to scale for 100G and 400G systems. The FPGA family is also ideal for bridging for Nx100G systems. Its programmable I/O and PCIe® Gen3/Gen4 provide flexible connectivity and system control across network processing units, and its multi-level security features–including bitstream encryption and DPA counter-measures–provide IP protection and advanced safeguards against network intrusion and cyber attacks.

Product Table

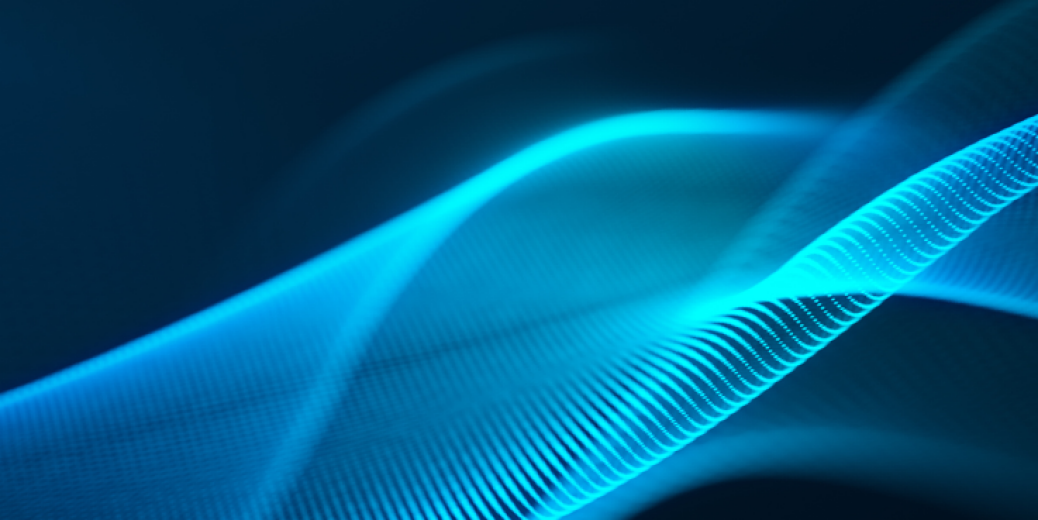

| AU7P | AU10P | AU15P | AU20P | AU25P | |

| System Logic Cells (K) | 82 | 96 | 170 | 238 | 308 |

| DSP Slices | 216 | 400 | 576 | 900 | 1200 |

| Total RAM (Mb)* | 4.9 | 4.5 | 7.6 | 10.2 | 15.2 |

| Transceivers (16.375Gb/s or 12.5Gb/s) |

4 | 12 | 12 | 12 | 12 |

| I/O | 248 | 228 | 228 | 228 | 304 |

* Total RAM= Maximum Distributed RAM + Total Block RAM

Documentation

Get Started

Early Access Program

Artix™ UltraScale+™ FPGAs are now in production and available in public tools. Leverage the resources below to learn more about design tools and design methodologies for the UltraScale™ architecture. If you have a project and are interested in device pricing and availability, contact your sales representative or visit the Contact Sales Form.

Video Tutorials

Video tutorials guide the user through the steps to compile, modify, build, and debug AMD FPGAs.

Training Courses

AMD hands-on FPGA and design training provides the knowledge you need to begin designing right away. For the entire catalog of courses, see here.

Popular Resources

Design advisories provide answers for the most common issues.