### Support Across The Board™

### **Bringing Products to Life.**

At Avnet Electronics Marketing, support across the board is much more than a tagline for us. From design to delivery – we are deeply committed to driving maximum efficiency throughout the product lifecycle.

### The Challenge

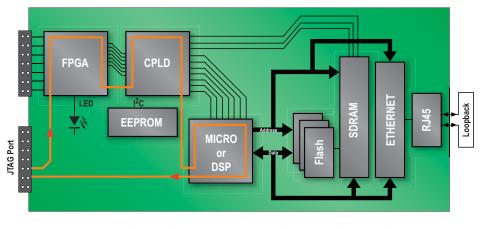

When the world's largest FPGA maker Xilinx was mounting the launch of its latest Spartan<sup>™</sup>-3 Generation family of low-cost FPGAs, the company wanted to ensure designers would have everything they need to compete in the highly competitive high-volume market. Xilinx turned to longtime partner Avnet to lend its technical expertise in creating a complete solution.

### The Solution

Avnet spent countless engineering hours alongside Xilinx — developing a comprehensive solution of starter kits, development boards, and Speedway™ educational workshops. With Xilinx® Spartan-3 Generation FPGAs and Avnet's support across the board, designers have access to all they need to save up to 50 percent in total system cost over competing FPGAs.

Visit www.em.avnet.com/xilinxspartan3kits to learn more about Spartan-3 solutions and to purchase a Spartan-3A evaluation kit for only \$39!

Accelerating Your Success\*\*

## Save days to weeks on your next FPGA debug cycle

### **Agilent Logic Analyzers**

Up to 1.2 GHz timing, 667 MHz state, and 256 M deep memory

0R

### **Agilent Mixed Signal Oscilloscopes**

4 scope channels + 16 timing channels

### **Agilent FPGA Dynamic Probe**

Application software to increase visibility inside your FPGA

### Fastest FPGA Debug Available

- Perform real-time functional and parametric debug that time-correlates internal FPGA activity with the surrounding system

- · Change internal FPGA probe points in seconds without design changes

- Get fast serial bus decode for I<sup>2</sup>C, SPI, CAN/LIN and RS-232/UART

Start saving time now. Download FREE application information. www.agilent.com/find/fpgatools

### Xcell journal

PUBLISHER

Mike Santarini mike.santarini@xilinx.com 408-879-5270

EDITOR

Charmaine Cooper Hussain

ART DIRECTOR

Scott Blair

DESIGN/PRODUCTION

Teie, Gelwicks & Associates 1-800-493-5551

**ADVERTISING SALES**

Dan Teie 1-800-493-5551 xcelladsales@aol.com

INTERNATIONAL

Melissa Zhang, Asia Pacific melissa.zhang@xilinx.com

Christelle Moraga, Europe/ Middle East/Africa christelle.moraga@xilinx.com

Yumi Homura, Japan yumi.homura@xilinx.com

SUBSCRIPTIONS

All Inquiries www.xcellpublications.com

REPRINT ORDERS

1-800-493-5551

www.xilinx.com/xcell/

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 Phone: 408-559-7778 FAX: 408-879-4780 www.xilinx.com/xcell/

© 2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx Logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilinx makes no warranties, express, implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against Xilinx for any loss, damage, or expense guest thereby.

### Xcell to New Heights

### Xcell Wants You!

Welcome to the new version of *Xcell Journal*. I'm Mike Santarini, *Xcell*'s new publisher. I joined Xilinx in March of this year after working 13 years as an editor covering the EDA, FPGA, ASIC, IP, and memory industries for EE trade publications *EDN*, *EE Times*, and *Integrated System Design*.

I've dedicated my entire professional career to keeping the IC and systems design communities informed of new design developments and challenges. Now I'm bringing that mission to the everexpanding Xilinx<sup>®</sup> user community. When Xilinx approached me for this job, I jumped at the chance.

Over the last 25 years, FPGAs have evolved from their glue logic beginnings to become a fundamental element of just about every digital design project. Indeed, today FPGAs boast multimillion-gate counts, MPUs, DSPs, and embedded functionality, and are starting to play a more central role in the world's most advanced products.

Even if FPGAs are not in your end product, chances are you've used at least one FPGA to develop that product. And what's beautiful about FPGAs – and at the same time a bit daunting – is their versatility. You can use them for any number of applications, but perhaps what's undermarketed is the "field-programmable" part of FPGAs. Yes, FPGAs are reprogrammable, meaning that you can change your design in the lab and even reuse the chips for other design projects. But you can also change the logic of your design in the field – after you've deployed your product.

The "FP" makes FPGAs the building blocks, Erector Set, Legos, ball of clay – you pick the analogy – of electronic design. We provide the renewable canvas (silicon) and the brushes and paint (tools and IP); you create the masterpieces. And as an editor walking through your gallery for the last 14 years, what beautiful, diverse and wonderful works of art you are creating. You are literally changing the world.

In my role as publisher here at *Xcell Journal*, I want to help you develop those masterpieces by keeping you informed of what the extremely hard-working folks at Xilinx are developing and what your peers are doing as well.

As you give this issue a read, you'll notice a number of new sections and a broad range of content, reflecting FPGA versatility. You'll notice that each issue contains a cover story examining the high-level challenges of a given application area. From there, the content becomes progressively more technical: from application articles that will appear in regularly featured sections, to how-to articles, to walkthroughs from our FAE staff. And to break it up a bit, we'll also profile one of our customers and take a look at new tool, IP, and board offerings from our growing list of partners.

This issue is a first of many steps to make *Xcell Journal* a technical Xilinx user community magazine. To reach its true potential, *Xcell Journal* needs your help; I encourage all of you to submit articles. Even if you are a bit pen-shy, I'll work with you to get your content in the magazine and out to your peers.

I hope you enjoy reading this issue of *Xcell* – a lot of people worked very hard to make this publication what it is. I'm hoping you will also pitch in to help it become what it can be. Please feel free to send me your articles and feedback to make *Xcell* excel to new heights.

Mike Santarini Publisher

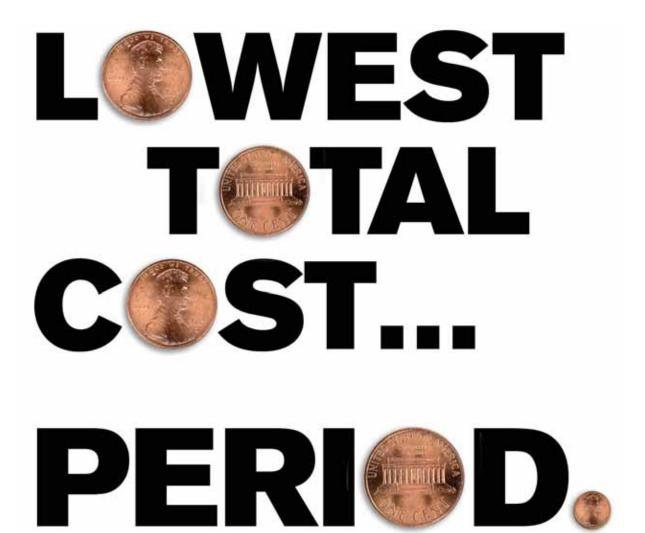

### **GET UP TO 50% LOWER COST**

Xilinx Spartan<sup>™</sup>-3 Generation devices are the only low-cost FPGA family to cut your total cost by half... and we can prove it! We offer the industry's widest range of devices, most comprehensive IP library (8x the nearest competitor!), a huge selection of development boards and we've minimized the need for external components.

Visit us at www.xilinx.com/spartan to download our free ISE™ WebPACK™ design tools and start your Spartan-3 design today. You too can experience the lowest total cost. Period.

The World's Most Widely Adopted Low-Cost FPGAS

### VIEWPOINTS

Letter from the Publisher *Xcell* to New Heights...4

**Xpert Opinion** What Role Will FPGAs Play in the Picocell Base Station Market?...14

**Xpectations** "Persona-Based Design": Tailoring our Flows to Your Needs...62

### XCELLENCE BY DESIGN APPLICATION FEATURES

**Xcellence in Automotive & ISM** Exploring and Prototyping Designs for Biomedical Applications...**18**

**Xcellence in A&D** Taking Designs to New Heights with Space-Grade Virtex-4QV FPGAs...22

Xcellence in New Applications

CERN Scientists Use Virtex-4 FPGAs

for Big Bang Research...28

### XCELLENCE IN COMMUNICATIONS

### THE XILINX XPERIENCE

**Xperts Corner** Using the JTAG Chain for Accurate System and Intra-Die Power and Thermal Analysis...32

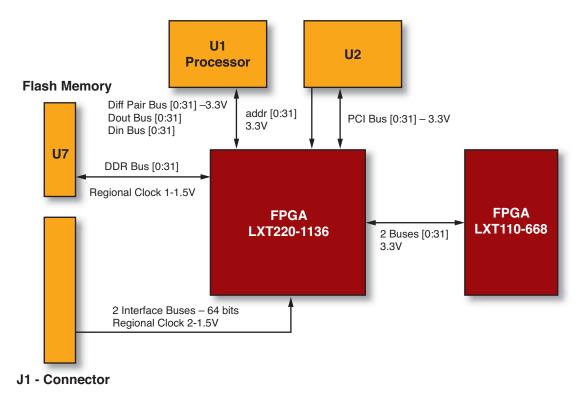

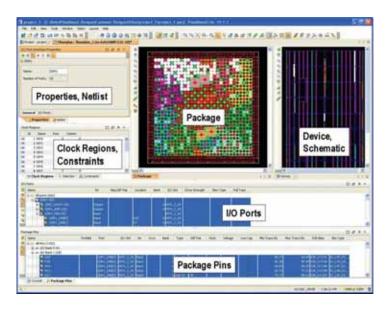

**Xplanation: FPGA 101** Solving FPGA I/O Pin Assignment Challenges...**38**

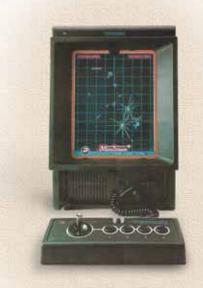

**Xperiment** Replacing Obsolete Video Game Circuits with Xilinx CPLDs...42

**Ask FAE-X** Identifying and Solving Timing Problems in Xilinx FPGA Designs...46

**Profiles of Xcellence** Ixia CEO Atul Bhatnagar: Calm in the Storm...**54**

### XTRA XTRA

**Xamples...** A mix of new and popular application notes...**50**

Are You Xperienced?

The Path to Successful Design...51

**Xcuse Us** The latest Xilinx tool updates and patches as of June 30, 2008...**52**

**Tools of Xcellence** What does Synopsys's acquisition of Synplicity hold for Xilinx customers? Aldec releases Active-HDL and ALINT code coverage tool.

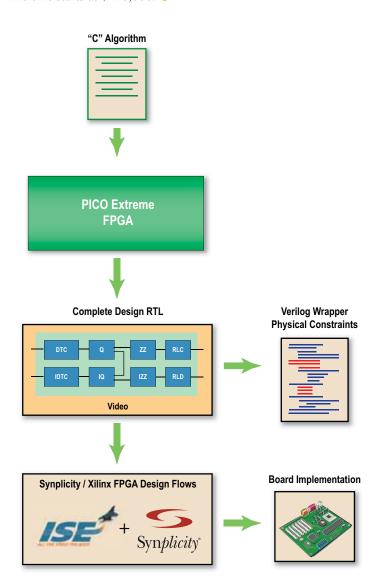

Synfora spins PICO Extreme FPGA...58

Selection Guides...63

by Mike Santarini Publisher, *Xcell Journal* Xilinx, Inc. mike.santarini@xilinx.com

The impending convergence of third-generation (3G) CDMA2000 and WCDMA/GSM wireless network standards into the 4G LTE (Long Term Evolution) wireless network standard presents developers of next-generation base stations with a bit of a challenge. How do you create a next-generation base station that will support current 3G communication standards as well as next-generation standards, and perhaps go the extra mile to outpace your competition and offer a solution that can accommodate whatever successive standard(s) the communications industry picks after LTE?

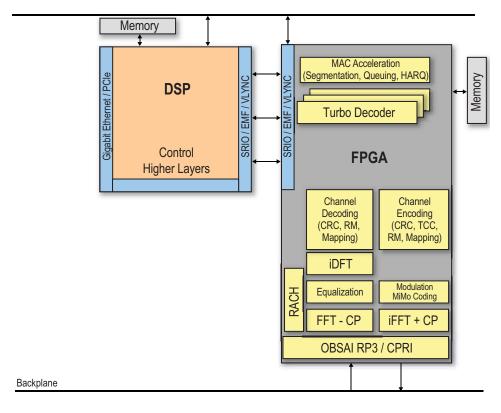

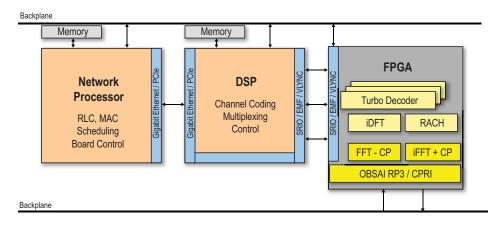

Stepping up to this challenge, many design groups are now in the process of creating multimode (also known as multi-standard) base stations that will support 3G and 4G standards – perhaps multiple variants of these standards – while being flexible enough to adapt to any changes that may arise in the design specifications or even the wireless standards the design targets. Many are giving FPGAs a more central role in multimode base station design (see Figure 1).

### The Promise of 4G: LTE and WiMAX

LTE promises to bring wireless customers data rates of 100 Mbps or higher, which is a 10x improvement in performance over current 3G networks. This data-rate increase paves the way for carriers and mobile handset makers to offer customers more advanced features on their respective networks and mobile devices, such as mobile TV, advanced video, and even gaming in addition to Internet, e-mail, and voice.

This means that mobile device makers will be able to sell more advanced phones to carriers, while carriers will be able to offer more expensive mobile phone plans and increase their average revenue per user (ARPU).

But of course, carriers must install a wireless network infrastructure before all that can happen.

Currently, 70% of the world uses GSM-based networks (in particular 3G WCDMA), while North America and South Korea primarily use 3G CDMA2000 networks. Carriers in Japan are scheduled to conduct a trial run later this year of the Orthogonal Frequency Division Multiple Access (OFDM) modulation scheme underlying LTE, essentially kicking off LTE adoption.

Manuel Uhm, senior marketing manager for the Wireless business at Xilinx, notes that carriers currently employing CDMA2000 networks will likely move to LTE as well, because Qualcomm's proposal for a follow-on to CDMA2000, UMB, didn't gain industry support.

Indeed, one of those CDMA2000 carriers, Verizon, recently announced that it will be installing LTE in the 700-MHz spectrum in North America. It recently won the 700-MHz spectrum in a Federal Communications Commision auction.

Still, the industry doesn't expect LTE to be in large-scale deployment until the 2012 time frame, so many wireless carriers shopping for next-generation base stations will be looking for hardware that will allow them to offer customers support for their current networks while providing an upgrade path to a faster 4G wireless network. Simultaneously, they will want to minimize the operational expenses of each system and the entire network, including reducing the base station power and thus utility costs.

Although CDMA2000 and WCDMA seem likely to converge on LTE, it's uncertain whether the rest of the world will also adopt LTE networks. Carriers in some countries are embracing data-centric networks such as WiMAX and WiBro (South Korea), which carriers can enhance to carry voice over packet. WiMAX and WiBro will compete with LTE.

But Loring Wirbel, director of *EE Times*' market intelligence unit and longtime communications editor, points out that LTE and WiMAX standards are very similar – reportedly 80% percent of the baseband functionality is the same – which opens the door for base station vendors to attempt to build one base station that can support 4G standards while still supporting legacy 3G networks.

But even if the world converges on LTE, it isn't likely to be the last network carriers

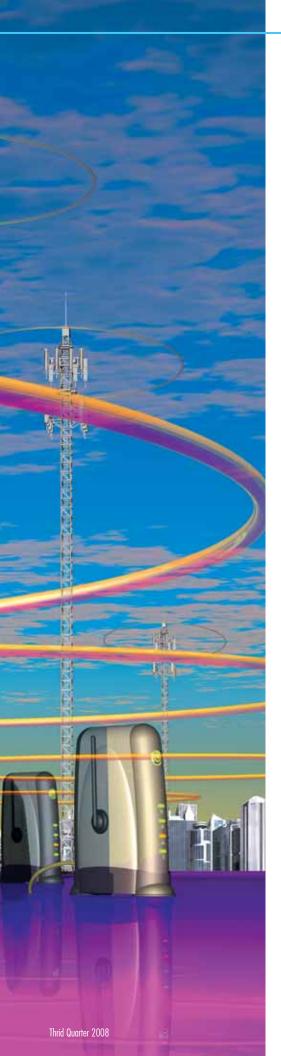

Figure 1 – Xilinx LTE baseband reference design

install. "WCDMA was supposed to be the convergence of air interface standards, but that wasn't the case," Uhm noted.

Indeed, if history is any indication of future behavior, it likely means that as soon as LTE gets established, some new need – be it network performance, new functionality/services, or even something political – will spur the need for a 5G solution, or perhaps an intermittent tweak to extend the life of LTE.

In fact, the industry is already laying the groundwork for 5G networks such as LTE advanced, even though the 3GPP (the international body that defines GSM network standards, including LTE) hasn't fully completed its definition of LTE, and the industry is only starting to roll out LTE equipment.

This uncertainty – which network will be best, what standard will really materialize (and in what form), and what new applications will it need to support – has to make carriers a bit more apt to hedge their bets and lean toward systems that are more adaptable, more expandable, and easily and ultimately less expensively modified to suit changes in 4G standards. In short, next-generation base stations need to be flexible, though to what degree is debatable.

### Undefined Standards and Multimode Opportunity

Because the 3GPP has yet to fully define the standard, companies building base stations today, especially those trying to be first to market, must build flexibility into their designs. The question is: how much flexibility?

Traditionally, flexibility has come in the form of sending out maintenance crews to replace entire cards in each base station and then tweaking the software running on those cards. But carriers shopping for 4G are looking for a greater degree of flexibility.

Indeed, wireless network standards (and wireless networks for that matter) comprise two fundamental layers: hardware (PHY) and software. The PHY layer, or physical layer, defines the performance and functionality requirements of the hardware the network will need to support the standard. The software layer defines the functionality that various software applications will need in order to adhere to the basic network standard.

Carriers can add software and even enhanced hardware (above and beyond the basic PHY and software requirements of the standard) to woo customers to their particular network. But with 4G, many believe base stations need to be more flexible than ever.

Some are anticipating that this will be the era where the industry produces the Holy Grail in base station technology: soft-

## [uncertainty] has to make carriers a bit more apt to hedge their bets and lean toward systems that are more adaptable, more expandable, and easily and ultimately less expensively modified to suit changes in 4G standards. In short, next-generation base stations need to be flexible...

ware defined radio (SDR), in which one system can support every standard simply by software reprogramming the base station hardware on the fly to adapt to any incoming signals.

Wirbel noted that in the dawning of the 3G era, several startups offered specialty chips with programmable logic cores and hard-wired high-performance blocks. These devices, however, "were insanely hard to program and insanely expensive." SDR has yet to fully deliver on its Holy Grail vision, but some vendors are starting to produce innovative SDR subsystems using commercial FPGAs. Perhaps sometime in the near future those subsystems will debut in base stations.

Still, some analysts (Wirbel among them) are not easily convinced that next-generation base stations will truly be as expandable and as multimode as many developers in the market predict (or hope).

"4G promises to make life easier than 3G, because what they want to do is harmonize WiMAX and LTE into one set of standards that both support OFDM. Then it's just a little software shim as to whether it supports WiMAX or LTE at the end of the day," Wirbel said. "At the same time, they have to support all of the RF chains and baseband issues for GSM and CDMA2000. At some point, you've got to make decisions about what to support or your base station becomes too complex."

"What happens in the RF component is just as important as the baseband. It's not the glamour part necessarily," said Gabriel Brown, Heavy Reading's senior analyst, who specializes in the wireless market. "You could in theory have multimode, upgradable baseband, but it doesn't really do you any good if you don't have the whole RF chain with either the right power output or bandwidth or frequency. Quite often you don't; this point gets glossed over quite often.

"Yes, it's software and it is upgradable, but you need to have the RF chain to support it. When folks typically say things are upgradable, they usually mean that it's upgradable within the same technology stream. For example, you can upgrade from WCDMA to HSPA to HSPA+ on the same baseband hardware by upgrading the software. But the idea of jumping from generations of technologies with different modulations is a bit of nirvana – it isn't really how things work."

### Battle at the Heart of the Base Station

At the heart of a base station's hardware is a series of electronic systems that control much of the wireless network functions. Traditionally, these systems have mainly comprised ASICs/ASSPs and standard products such as DSPs. But those technologies are limited in how design groups can modify them to suit late changes in standards or even upgrade the hardware in the field.

Therefore, as base station vendors begin designing 4G base stations that must support the as-yet-not-fully defined LTE standard while also supporting 3G networks, they are increasingly giving FPGA technology a more prominent role in controlling those systems.

"If you looked in a base station five years ago, you wouldn't find many FPGAs," Uhm said. "Today they are a prominent part of the radio and channel cards." One of the reasons, Uhm added, is that FPGAs fulfill the need for base station designs to be much more flexible than in the past.

To make changes to traditional 3G base stations, companies typically had few options. They could try to implement a software patch to rectify a problem in software or a shortcoming in hardware, but doing that often slows down the hardware and thus the overall computation of the base

station, which if anything in the emerging days of LTE needs to be faster. Or they could send a technician out to the site to physically replace a defective or older PCB containing those devices with a newer one (and possibly add a software patch as well).

If there's a drastic change, like the need to support an extra standard, carriers may have to install new base stations, much like AT&T did a few years ago when it moved from GSM to WCDMA. Of course, sending out technicians to sites around the world to swap out hardware and program software – on top of mountains, on top of buildings, on the edges of cliffs – adds great maintenance costs to a carrier's network. Adding new base stations and securing leasing for those sites is exponentially more expensive.

"Base station vendors would love to sell carriers a network of base stations for each of the standards, but carriers can't afford to do forklift upgrades anymore," Uhm said. "They are looking for the flexibility to add new revenue-generating services, higher data rates, lower power, lower maintenance costs, and of course, a great price."

Analysts point out that many years ago, base stations cost around \$250,000, but new base stations will likely be in the \$15,000 to \$25,000 range. They note that the unit price of base station hardware is only a fraction of the overall cost, and that leasing space and maintenance costs can be exponentially higher than the base station itself.

What's more, if a base station needs to support multiple standards, designers typically have to create an ASIC and associated PCB for each of those standards, as well as extra circuitry to negotiate how those boards will interact with the existing antennae.

In particular, ASICs are increasingly more expensive at relatively low volumes (and at volumes typical for the base station market) and are difficult to produce on

Third Quarter 2008 Xcell Journal 11

leading-edge processes, making them increasingly less attractive for the macrocell, microcell, and picocell base station markets.

A single 65-nm ASIC mask runs around \$1.5 million, and a 45-nm mask is double that. Adding EDA and IP costs tacks a few million more onto design costs. ASSPs are similarly expensive for silicon vendors, complicated to produce, and typically modifiable only on a software level. Given the choice of ASICs, ASSPs, or DSPs, DSPs are the most versatile for base station applications and will likely maintain a secure position in 4G base stations. But only the software is modifiable, limiting flexibility if designers want to make changes to their designs in the field.

"When the issue was just GSM vs. CDMA for voice, it was best to do everything in DSP. But when people started adding data services such as EDGE and HSDPA, it really made a lot more sense to look at an FPGA solution," Wirbel said. "That transition started to take place around 2002 or 2003."

It's for all of these reasons that designers are starting to give FPGAs a more central role in the era of multimode base stations. Some are even making FPGAs the primary devices for software defined radio implementations of multimode base stations.

"FPGAs add another level of flexibility and performance to a base station that ASICs, ASSPs, and DSPs cannot, enabling operators to increase ARPU by adding new bandwidth-intensive applications," Uhm said. "FPGAs are attractive for multimode base stations because they have a mix of reconfigurable resources for high-performance signal processing."

Joe Byrne, a senior analyst with the Linley Group, notes that one reason the FPGA is looking more attractive in the base station market is because LTE employs OFDM modulation. "The downstream modulation scheme in LTE is OFDM, which is a different scheme than WCDMA," Byrne said. "It's conceivable that next-generation base stations will essentially be one piece of equipment with two different processing modules: one that does the legacy protocol and another that does the new protocol.

But I think the opportunity is to create equipment that does both, and for that you need something that is programmable. The programmability can come from FPGAs or something with more traditional software programmability, such as a DSP.

"The thing with OFDM is that instead of being a signal carrier, there are a lot of signals conveyed on a lot of carriers in parallel. That means the processing

has to be done in parallel. So from an FPGA perspective, if you have these thousands of carriers to process, you can take your big FPGA and partition it into these processing units in parallel and do the processing of each carrier. That is something that an FPGA would be well suited for, instead of doing it in sequence.

"There's an opportunity for doing it with a logic-based approach, such as an FPGA, as opposed to a software-based

### **Base Station 101**

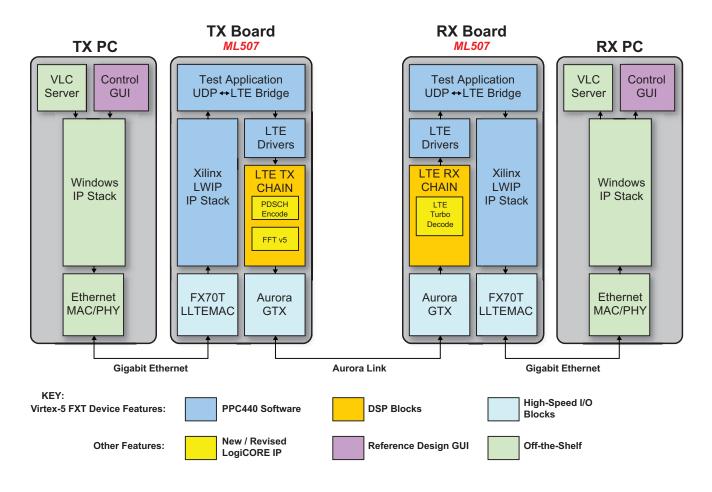

To date, wireless network carriers have traditionally employed two types of base stations (commonly referred to as cells). The first is the macrocell (see Figure 1), which usually consists of a tall tower with transmit and receive radio antennae at the top of the tower (receive is usually at the very top).

These antennae run signals, through fiber-optic cable, down the tower to electronics systems traditionally located at the base. The electronic systems coordinate the transmit and receive functions up to the antennae, negotiate coverage

with other base stations, and transmit call data to the rest of the network as customers move from one base station's coverage area to another, racking up billable minutes. Macrocells typically have large coverage areas; carriers deploy them in rural areas or along long stretches of highway.

The second type of traditional base station is called a microcell. Wireless carriers typically deploy these in densely populated areas like cities. The coverage area of a microcell is smaller than the coverage area of macrocell, but a cluster of microcells allows more people to access their carrier's wireless network.

In recent years, the industry has produced two other types of base stations: the picocell and femtocell. The picocell is for smaller, even more densely populated areas such as airports, conference centers, and sporting venues. The femtocell targets home and small office use, whereas the macrocell, microcell

Figure 1 – A typical macrocell base station with receive antennae at the top, transmit antennae below the receive antennae, and the control system at the base.

and picocell are traditionally sold to networks. Femtocells will likely be sold at retail directly to consumers or perhaps bundled in with services such as cable or satellite TV.

"So far, femto has been over-hyped and under-delivered," Wirbel said. "We don't even know if it will be a real market and what the price points will be." Still, it could be an interesting play as more devices in the home become wireless.

Analyst Richard Wawrzyniak addresses the promises and challenges of the picocell market as the "Xpert Opinion" in this issue of *Xcell Journal* (see page 8).

approach, such as a DSP. Some fine tuning will always take place. The physical layer may be pretty well understood but the actual algorithm to extract the best performance out of the physical layer may change. It's good to have some flexibility, especially in the early days of the market."

Wirbel agrees with Byrne and believes that next-generation base stations will likely have a healthy mix of DSPs and FPGAs. "I think that the future lies in mixing and matching major DSP architectures on the top, with separate channels for multiple FPGAs in the middle. I think that's where the base station market is going," said Wirbel.

Designers are considering several architectures for 4G base stations. Figures 2

and 3 illustrate two of the many uses for FPGAs in those architectures. Analysts point out that in addition to flexibility, performance will also be a key to 4G networks. In fact, it's such an issue that many next-generation base station designers are moving more of the compute power up the base station tower, closer to the antennae, to physically shorten the amount of time it takes for the antennae and base station control system to communicate.

Uhm said that the latest generation FPGAs are up to the performance requirements and many employ high-speed I/O.

### **5G and Beyond**

While analysts seem to agree that FPGAs will play a stronger role in 4G networks, they all doubt that any manufacturer will be able to build a multimode base station that will also be able to anticipate and handle the data rates and feature set requirements of 5G base stations.

"Carriers have been doing incremental upgrades to their 3G base stations for several years now," Byrne said. "They've upgraded from 7.2 Mbps to 10 Mbps with a software upgrade to the baseband processor, which is now a DSP or FPGA. I think that with LTE, we will see a lot of incremental upgrades. If you do a bigger upgrade than that, you'll essentially need new hardware."

Byrne and others note that by the time 5G makes it to mainstream, there will likely be some crazy new hardware performance and functionality requirement. That means more challenges and opportunities for designers along the full spectrum of the wireless network.

Uhm said that Xilinx is investing heavily in developing not only FPGAs for the base station market but also tools, IP, and embedded software. Xilinx is also working with its many IP and software partners to help designers meet challenges and create innovations for the 4G wireless network, especially those base stations at the heart of worldwide wireless communications. For more information about Xilinx silicon and solutions for the base station market, visit www.xilinx.com/esp/wireless.

13

Figure 2 - FPGA preprocessing with DSP architecture

Figure 3 – FPGA as coprocessor for LTE

Third Quarter 2008 Xcell Journal

## What Role Will FPGAs Play in the Picocell Base Station Market?

Airports outfitted with a comprehensive set of picocell base stations could give their customers much better experiences while traveling.

by Richard Wawrzyniak

Senior Market Analyst,

ASIC and SOC

Semico Research Corp.

richw@semico.com

As we enter the second half of 2008, a sad fact of life is that airline travel is becoming harder and more uncomfortable with each passing week. This is due in large part to increased fuel costs for airlines and the cutbacks in service enacted to help offset these costs. Plus, some airlines are instituting additional fees for checked baggage and are also taking planes out of service, making the number of seats available fewer at any given time.

Undeniably, the life of the casual airline traveler is becoming more complicated. This is doubly true for the business traveler.

What does the FPGA have to do with all this? Please bear with me while I explain.

### Traveler's Tension

Picture a large airport anywhere in the world, with many gates. Numerous planes are taking off and landing. Large masses of people are coming and going; the corridors are packed. Everyone is either trying to make a connecting flight, heading toward baggage claim, or looking for a place to rest weary bones.

Let's say that your flight has just arrived. You could be traveling by yourself, with other colleagues, or even with your family. This airport is unfamiliar to you and the people in it may be speaking a foreign language. The signs may also be in an unfamiliar language. Your flight has landed late (of course) and you need to make decisions about several things simultaneously:

- Where is the gate for my next flight?

- How far away is the gate from where I'm at now? Do I have enough time to get there without running?

- Do I have enough time to get something to eat (preferably at a reasonably good restaurant) along the way?

- What types of food are available along the way? Do any of them interest me, my colleagues, or my other family members?

- My colleagues were sitting in seats somewhere behind me on the plane. If I obtain the necessary information about shops, restaurants, gates, and flight times, how do I easily communicate this to them without losing any time?

- I need to connect to my office to send/download a file necessary for my next customer visit. Will my cell phone reception provide a data rate sufficient to accomplish this in a reasonable amount of time so I still have time to eat? (Don't forget, you're still hungry.)

- What other shops are along the way?

wI need to pick up a birthday present,

which I didn't have time to do at my

point of departure. Am I limited to

just the shops I can see along the way?

Does more information exist somewhere that I can access easily?

- Finally, where is the closest restroom?

I'm sure the list of questions above pretty much outlines the experiences of most airline travelers today. It is a set of decision points that we travelers review each time we fly – especially if our arrival airport is new or unfamiliar to us. But given the press of humanity on all sides, all trying to do essentially the same thing at the same time, how will you collect all of this data in the short amount of time you have? This can be a daunting and stressful situation for most people. It definitely takes most of the fun out of flying today.

### **Smooth Skies**

I'd like to lay out the following scenario of what I think is a possible solution to solving some of these issues for airline travelers.

As the cell phone market continues to evolve, new types of technologies are becoming available. This includes commutions have yet to be worked out. Areas like which communications protocol to use – WiMAX or WiFi – are as yet undetermined. How many users each base station will support is still undetermined. In addition, who will pay for these stations and how much access to these services will cost are also as yet undecided.

Changes will also have to occur on the cell phone handset side for these types of services to be accessed. In fact, several vendors (Intel being one of them) are planning to create semiconductor solutions that incorporate several air interfaces — all simultaneously active.

### Airline travelers might start to see some of the fun come back into flying, with services enabled by picocell base stations.

nication interface solutions such as WiMAX and WiFi for broader, faster coverage. A new technology has also come along: the picocell base station.

A picocell base station is similar to a cellular base station, except that it is intended to function in large municipal buildings and large commercial spaces such as airports and sports stadiums. Unlike its larger cousin, the cellular base station, each picocell base station is intended to service a far smaller number of users – possibly only several hundred to 1,000 users at one time, as the range of a picocell base station is only 100 to 200 feet.

Because of these restrictions, it would take still many picocell base stations to fully cover one facility (think O'Hare Airport or any large sports stadium). The main idea for this type of solution is to make very fast data rates available to users and to increase the quality of services offered to them.

One possible scenario, given the increase in capabilities, is to offer good quality mobile TV, for example. Another is some form of video conferencing, which business travelers would surely pay for, as it would give them the opportunity to be more productive while traveling.

I must point out that at the time of this writing, many details for picocell base sta-

These solutions will begin entering the market toward the end of 2008 and into 2009. Much work still needs to be done to arrive at the right mix of features and capabilities. However, it would seem that there is definitely some value to this type of solution.

Airports outfitted with a comprehensive set of picocell base stations could give their customers much better experiences while traveling. Vendors could offer a wider set of products and sell these products to a broader set of customers. Most airport vendors today do not really do much advertising, depending instead on foot traffic.

Imagine a situation where vendors allow access to their products and services over the Internet through picocell base stations. Potential customers could access airport restaurant menus remotely, order meals, and reserve table space if necessary. They could pay for their meal and have it ready as they move toward their connecting gate.

The same solutions could apply for the other basic questions I outlined previously: where is the next gate, how much time does it take to get there, what shops and restaurants are along the way, and how do I communicate this information to my colleagues. All of these questions can be answered by putting such a system in place.

Thrid Quarter 2008 Xcell Journal 15

To make such a scenario real, additional middleware must be written with the appropriate level of security for financial transactions. This presents opportunities for both software companies and facility owners to jointly participate in improving the level of service available to the traveling public.

### **FPGAs in Picocell Base Stations**

Back to the FPGA. For the type of system outlined in this article, the number of picocell base stations would need to be substantial, since the range of each system will be fairly limited. This increases the number of systems needed to offer full coverage.

Given the range of capabilities inherent in such systems, the types of services offered must change very fast to meet changing consumer preferences. Programmable logic is a perfect fit given these parameters.

Picocell base stations will be fitted in relatively small enclosures, probably high up toward the ceiling in any given large commercial space. In this situation, there will be little opportunity to do an extensive installation of new fixtures, since the space around these installations will most likely remain in service during the installation process. Although the systems will have access to building power, they won't have extensive cooling systems, which means operating in ambient conditions. This lends itself well to the direction programmable logic is heading in today;

namely, lower power silicon that still delivers relatively high performance.

Finally, because the number of systems in any of these environments will be large, the ability to swap out circuit boards for upgrades will be limited. This is another area where programmable logic can shine, given its ability to be reprogrammed as needs dictate.

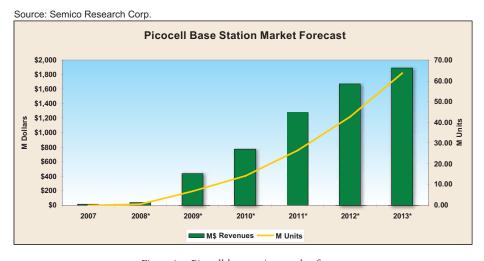

Semico Research Corp. has looked at this market and has concluded that a real potential exists both for the picocell base station concept and for the role programmable logic can play within it.

The forecast shown in Figure 1 is for the semiconductor content in the entire picocell base station market, including programmable logic. It is reasonable to expect that programmable logic will represent at least 15% of these revenues. It is also likely that each system will include at least one programmable logic device and that larger systems will include more than one programmable logic device.

If, as Semico believes, this market does in fact come to fruition, it can represent a significant growth potential and revenue stream to the programmable logic industry in the coming years.

The future is indeed bright for programmable logic. Airline travelers might start to see some of the fun come back into flying, with services enabled by picocell base stations.

Now if airports could do something to make their seats more comfortable ... •

Figure 1 – Picocell base station market forecast

### Xilinx Titanium Dedicated Engineering

- Increase your productivity

- Minimize your risk

- · Get your innovations to market faster

Our team of expert engineers will act as trusted advisors to your team, to give you the competitive edge.

With expertise in key application areas and design disciplines such as embedded, debug, design tools, digital signal processing, timing closure, and performance optimization, Xilinx Titanium Engineers will become a game changing extension of your team and will help you get it done!

Visit us at www.xilinx.com/titanium to learn more.

## Exploring and Prototyping Designs for Biomedical Applications

Third Quarter 2008

Researchers at the University of Hawaii at Manoa have implemented ECG analysis algorithms with Xilinx System Generator.

by Ashish Shukla Graduate Student University of Hawaii at Manoa ashishshuklabs@gmail.com

Luca Macchiarulo

Assistant Professor, Department of Electrical Engineering

University of Hawaii at Manoa

lucam@hawaii.edu

Many physicians use electrocardiogram (ECG) machines to monitor the electrical activity of the heart and the heart condition in general. But today, there is a lengthy delay in the time it takes to transfer data from ECG monitoring machines to trained physicians.

Here at the University of Hawaii at Manoa, we are researching ways to transfer – in real time – preprocessed ECG data from the patient's heart to physicians. As a first step toward this goal, we implemented two variants of a well-known software detection algorithm for ECG in hardware and explored the design choices using Xilinx® FPGA tools and hardware,

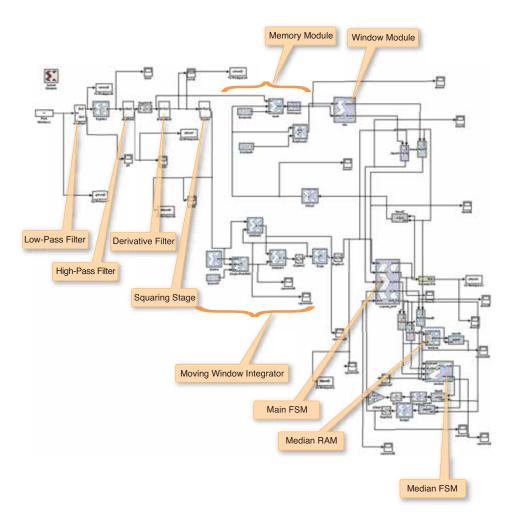

Many biological instrumentation-based designs require designers to combine filtering stages and customized logic such as finite state machines in the same system. But now it is easier for researchers to design filters in the Xilinx System Generator environment by simply connecting the various blocks from the Xilinx blockset (included with the System Generator blockset library) instead of creating these modules from scratch using a hardware description language like Verilog or VHDL.

Using System Generator to create most of the blocks allows you to concentrate on the critical parts of the design and delegate the details of the implementation of those standard modules to the tool. You can then import your custom logic modules into the System Generator environment; the tool will integrate those custom logic blocks with the rest of the design.

## Because noise contamination is an inherent problem in ECG monitoring and we cannot completely remove it, we had to come up with a way to suppress noise contamination.

### **Automated ECG System Analysis**

A heart's natural pacemaker, composed of special self-exciting cells, generates and propagates a polarization and depolarization electrical signal that regulates the proper contraction of the heart muscle. This electrical activity is recorded as an electrocardiogram (ECG) by a machine called an electrocardiograph, which provides physicians with a wealth of information on heartbeats and the heart's condition in general [1].

The QRS complex – a wave structure that corresponds to the depolarization of ventricles and has a spiked shape in the ECG – is often the most telling waveform found in an ECG signal. The morphology, duration, and amplitude of the QRS complex in an ECG signal provides significant information to physicians diagnosing various arrhythmias and other cardiac ailments.

Health professionals can best judge the state of a patient's heart by monitoring the heart's activity (and the QRS complex) during stress or physical activity. Therefore, health professionals often connect ECG monitors to their patients for many hours (generally 24 hours at a time).

Currently, most health professionals use Holter System monitors for this purpose. But Holter System monitors have an inherent battery power and processing power constraint that limits their functionality to data acquisition systems.

A Holter System's heart monitors record the patient's ECG data to flash memory or to a tape attached to the system. A technician then removes the drive from the Holter System and sends it to the lab, where technicians analyze the data. Once the lab technicians complete their analysis, they send the ECG report to the physician. Of course, this means that there is a delay between hooking up the monitor to the patient and getting the ECG data to the patient's physician, thus delaying treatment, possibly with tragic consequences.

Here at the University of Hawaii at Manoa, we are researching how to create ECG analysis systems that will reduce the amount of time it takes to transfer data from the patient's heart to the physician by carrying out the analysis in real time. We hope to achieve this by integrating the ECG analysis system into portable ECG monitors, which physicians can use directly and thus eliminate the technician translation/analysis step.

To aid us in this effort, we have implemented real-time ECG analysis on a Xilinx Spartan<sup>TM</sup> XC3S500 device in the Spartan-3E starter kit, which allows the system to perform this analysis much faster than previous software-based methods. FPGAs offer many advantages for this and other applications because they support rapid prototyping, are less expensive than ASICs at low volume, and are quickly reprogrammable.

Furthermore, their fast and efficient testing option, combined with System Generator software, makes them a great choice for algorithm exploration as well as hardware implementation and prototyping.

### Implementation of the Algorithm in Hardware

In our research, we are implementing a well-known algorithm by Tompkins and Hamilton for QRS detection in hardware ([2], [3], [4], [5]). To help us with this effort, we took advantage of the fast prototyping features included in the Xilinx toolset.

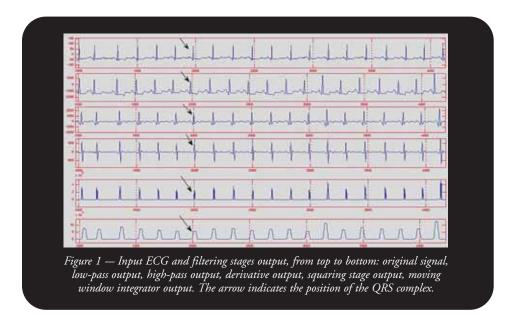

In our system, the processing of the ECG signal begins with a number of filtering stages through which a signal must pass before the system accurately detects a QRS complex. We divided the design into two main stages. The first stage, or preprocessing stage, comprises four linear filters and one non-linear filter. The second stage, or peak detection stage, identifies the peak signal in the QRS complex and applies decision rules to qualify a feature as a QRS complex.

### Filtering Stage

The ECG recording is very sensitive to even the smallest body movement or noise, such as electrical muscle (myographic) signals and the system's own electrical power-line interference. Because noise contamination is an inherent problem in ECG monitoring and we cannot completely remove it, we had to come up with a way to suppress noise contamination. We achieved this by employing filtering during the preprocessing stage (as in [4], [5]).

To do this, we first pass an ECG signal through an infinite impulse response (IIR) low-pass filter, which suppresses the high frequency noise in the signal. Then the signal passes through an IIR high-pass filter, which attenuates the P and T waves in the signal and suppresses the DC offset present in the signal.

The low-pass and high-pass filter together form a bandpass filter. It then feeds the output of the high-pass filter to a finite impulse response (FIR) derivative filter, which further emphasizes the QRS complex. This typically presents a more pronounced slope variation compared to the other signal features, making it somewhat easier for observers to identify [1].

The FIR derivative filter step also helps further reduce the noise content of the signal. After filtering, we employ a squaring stage that carries out non-linear amplification of the QRS complex and makes all data points positive.

Finally, we use the output of the squaring stage as the input to a moving window integrator. Each sample output from this filter is an average of the previous 32 values. We implemented all these filtering stages directly in the Simulink environment using the System Generator tool. Then we tried out two different approaches for the next stage, which is a moving window integrator.

The first approach involved the connection of a number of register, delay, and adder blocks to implement the filter as a

Thrid Quarter 2008 Xcell Journal 19

direct Form I structure. With this approach, however, we ended up using 31 adders and an equally large number of delay or register blocks.

We investigated further and later came up with a more resource-efficient structure that uses the block RAM resources in the Spartan-3 FPGA. This final structure uses a

small RAM of 32 40-bit words and just two adders and is also very efficient in timing. Figure 1 shows a typical ECG input, with results of the various filtering operations.

### Peak Detection Stage

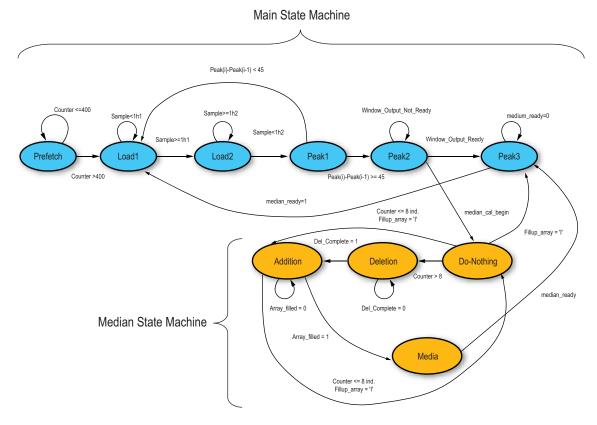

In the peak detection stage, we are trying to find the peak in the output of the moving window integrator. The peak detection process depends on the calculation of the threshold value, and we can locate a peak among the sample values that are greater than the threshold value. But the algorithm does not report a peak until a sample appears in the falling slope of the moving window integrator signal with a value less than half of the peak value.

We use this method because it reduces the number of false peak detections caused by noise. Once the algorithm locates the maximum point of the QRS signal in the moving window integrator output, we search for a peak in an appropriately delayed copy of the output of the high-pass filter and use it as a fiducial point for the position of the QRS complex.

Essentially, we are finding the peak of the QRS complex in the output of the bandpass signal instead of the original signal, because the original signal is highly contaminated by noise. We achieved this using a memory module, which records the previous 60 samples from the high-pass filter and sends a fixed interval of samples

Figure 2 – State machine for the complete design

containing the QRS complex as an input to the window module. The window module finds the maximum QRS signal.

We based the threshold for the next peak detection process in the moving window integrator output on the median of the eight previously detected peaks.

To calculate the running median calculation, the system maintains an updated, sorted list of such peaks. The computation is supervised by a median calculation FSM (called the median state machine) communicating with a separate peak detection FSM (called the main state machine) (see Figure 2). The main state machine finds the peak in the moving window output (as discussed); then the median state machine sets up the threshold value for the next detection.

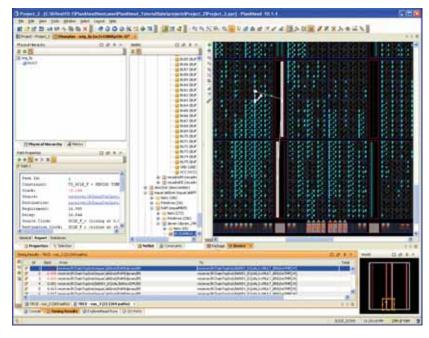

We implemented the entire peak detection stage in VHDL. It contains the memory, window, main, and median state machines and the median RAM modules. Later, we imported these VHDL modules into the System Generator environment as black boxes and simulated the design (Figure 3).

### Programming and Testing the Hardware Implementation

We programmed the FPGA through the JTAG port. To test the design, we used System Generator's JTAG co-simulation feature, which allowed us to pass data from the Simulink environment through the USB cable to the board (the Xilinx Spartan-3E starter kit) containing the downloaded design.

Figure 3 – Complete design in the System Generator environment

The design implemented in the FPGA processes the data and sends the output back to the MATLAB environment so that we can compare it to the simulation output. This feature was very convenient and helped us establish the accuracy of the design implementation in hardware. It also allowed us to run tests on complete sets of benchmark ECG data (from www.physionet.org) in a fraction of the time we previously needed to test the software version of the algorithm.

Overall, we found System Generator to be very useful for implementing designs for biomedical instrumentation applications. The tool provides easy filter design options and simplifies design implementation by accepting imported custom modules as black boxes. It also provides a fast and efficient way to test a design on hardware, with easy interfacing options between the board and the user's workstation.

### Citations

[1] B-U. Kohler, C. Hennig, and R. Orglmeister, "The principles of software QRS detection," *IEEE Engineering in Medicine and Biology Magazine*, vol. 21, no. 1, pp. 42-57, January 2002.

[2] A. Shukla and L. Macchiarulo, "FPGA based ECG Analysis System," *Proceedings of the Sixth IASTED International Conference on Biomedical Engineering*, Austria, pp. 68-72, February 2008.

[3] A. Shukla, "Hardware Implementation of real time ECG analysis algorithms," M.S. thesis, University of Hawaii at Manoa, Honolulu, Hawaii, 2008.

[4] J. Pan and W. Tompkins, "A real-time QRS detection algorithm," *IEEE Transactions on Biomedical Engineering*, vol. BME-32, no.3, pp. 230-236, March 1983.

[5] P. Hamilton and W. Tompkins, "Quantitative Investigation of QRS Detection Rules Using MIT/BIH Arrhythmia Database," *IEEE Transactions on Biomedical Engineering*, vol. BME-33, no.12, pp. 1157-1165, December 1986.

21

Third Quarter 2008 Xcell Journal

## Taking Designs to New Heights with Space-Grade Virtex-4QV FPGAs

Special processing, packaging, and SEU mitigation techniques enable designers to perform system-level integration with reconfigurable FPGAs in space-based systems.

by Greg Lara Virtex Marketing Manager Xilinx, Inc. greg.lara@xilinx.com

Carl Carmichael

Manager, Space Product Solutions

Xilinx, Inc.

carl.carmichael@xilinx.com

Gary Swift

Radiation Effects Specialist

Xilinx, Inc.

gary.swift@xilinx.com

Designing high-performance electronic systems for space presents designers with a slew of unique challenges. Designers must meet tight power and weight budgets while under enormous pressure to get designs completed on time and with zero flaws.

Companies and government agencies set rocket launch schedules years in advance of actual launch dates. Missing a launch date can delay programs until, literally, planets align; some delays can even lead to project cancellations.

But while space applications have power, weight, and time-to-launch challenges, by far the most stringent requirement is ultra-high reliability. If a component fails in space, you can't send the Geek Squad out to fix it (unless you have astronauts on board).

To make things worse, as spacecraft rise to higher altitudes – and especially as they move beyond the protective blanket of Earth's atmosphere – they are bombarded by increasing levels of radiation that can upset or even disable delicate electronic components.

As a viable solution to these challenges, you can try to integrate functions into an ASIC, which can meet your performance, capacity, and power requirements. But designing an ASIC is increasingly complex, and if the design requires new functionality or if you find a bug late in the design cycle, you may have to re-spin the design or even create a new mask, causing you to miss launch windows.

Some silicon vendors offer radiation-hardened anti-fuse FPGAs, but those devices have limited capacity and performance, which means most of them are unsuitable for achieving SOC-type integration goals. Increasingly, designers are turning to space-qualified Xilinx® Virtex<sup>TM</sup> FPGAs, which allow them to achieve performance, power, and integration targets while enjoying flexibility and productivity benefits previously available only in the commercial arena.

Let's examine our latest space-grade offering, the Virtex-4QV FPGA family, and some design techniques and tools that you can use in your design projects to tailor the devices for your space deployment requirements.

### The Xilinx Space Heritage

Xilinx has provided uninterrupted support to the aerospace and defense (A&D) community since 1989. Our company pioneered the application of SRAM-based FPGAs in high radiation environments, beginning with the XQR4036XL FPGA, which first flew in FedSat, an Australian satellite.

Quad-redundant XQR4062XL FPGAs performed mission-critical landing duties (pyro control) on the Mars Exploration Rover (MER) 2003 landers, which delivered the Spirit and Opportunity MERs to the surface of Mars. Virtex XQRV1000 FPGAs handle motor control functions on both MERs as they explore the Martian landscape.

To accelerate the adoption of reconfigurable FPGAs for aerospace applications, in 2002 Xilinx joined forces with the Jet Propulsion Laboratory, Los Alamos National Labs, Sandia, Aerospace Corp., and SEAKR Engineering to found the Single-Event Effects (SEE) Consortium. Fostering an environment of openness and collaboration, the SEE Consortium leverages the collective talents and financial resources of its member companies to perform exhaustive analysis of complex FPGAs.

The SEE Consortium subjects FPGAs to in-beam radiation testing and then reports peer-reviewed results to the industry. As a result of those efforts, Venus Express, the Mars Reconnaissance Orbiter, GRACE, OPTUS, TACSAT2, CIBOLA, and a number of classified programs have included Xilinx FPGAs. Many more Virtex FPGAs will soon be

orbiting overhead, as our customers have more than 50 new programs currently under development.

### **Virtex-4QV FPGA Family Overview**

To bring the benefits of advanced FPGAs to designers of in-orbit, space-based, or extraterrestrial systems, Xilinx recently launched a space-grade variant of its Virtex-4 family. The new Virtex-4QV family of radiation-tolerant FPGAs meets the military's MIL-PRF-38535 Class V screening requirements and offers design groups a compelling alternative to ASIC and one-

time programmable logic technologies. The lineup comprises four of the configurations from the commercial Virtex-4 device family (see Table 1).

High-performance logic, processing, and DSP capabilities make Virtex-4QV FPGAs ideal for demanding applications such as video processing, radar, and encryption. In addition, their packet processing capabilities are enabling a new generation of networked space-based communication systems, such as the IRIS program, to put reconfigurable network routing in orbit.

|                                                                                |            | Virtex-4QV FPGAs<br>Optimized for: |           |           |            |  |  |  |

|--------------------------------------------------------------------------------|------------|------------------------------------|-----------|-----------|------------|--|--|--|

|                                                                                |            | Logic DSP Embedded Processing      |           |           |            |  |  |  |

| Part Number                                                                    |            | XQR4VLX200                         | XQR4VSX55 | XQR4VFX60 | XQR4VFX140 |  |  |  |

| Logic Cells                                                                    |            | 200,448                            | 55,296    | 56,880    | 142,128    |  |  |  |

| CLB Flip-Flops                                                                 |            | 178,176                            | 49,152    | 50,560    | 126,336    |  |  |  |

| Maximum Distributed RAM (Kb)                                                   |            | 1,392                              | 384       | 395       | 987        |  |  |  |

| Block RAM/FIFO w/ECC (18 Kb each)                                              |            | 336                                | 320       | 232       | 552        |  |  |  |

| Total Block RAM (Kb)                                                           |            | 6,048                              | 5,760     | 4,176     | 9,936      |  |  |  |

| Digital Clock Managers (DCMs)                                                  |            | 12                                 | 8         | 12        | 20         |  |  |  |

| Maximum Single-Ended I/Os                                                      |            | 960                                | 640       | 576       | 896        |  |  |  |

| DSP Slices                                                                     |            | 96                                 | 512       | 128       | 192        |  |  |  |

| 10/100/1000 Ethernet MAC Blocks                                                |            | -                                  | -         | 4         | 4          |  |  |  |

| PowerPC Processor Blocks                                                       |            | -                                  | -         | 2         | 2          |  |  |  |

| Total lonizing Dose (krad)                                                     |            | 300                                | 300       | 300       | 300        |  |  |  |

| SEL Immunity (MeV-cm <sup>2</sup> /mg)                                         |            | >125                               | >125      | >125      | >125       |  |  |  |

| Package                                                                        | Area       | Available User I/Os                |           |           |            |  |  |  |

| CFA Packages (CF): Flip-Chip Ceramic Column Grid Array (1.0-mm Column Spacing) |            |                                    |           |           |            |  |  |  |

| CF1140                                                                         | 35 x 35 mm |                                    | 640       |           |            |  |  |  |

| CF1144                                                                         | 35 x 35 mm |                                    |           | 576       |            |  |  |  |

| CF1509                                                                         | 40 x 40 mm | 960                                |           |           | 768        |  |  |  |

Table 1 - Xilinx 90-nm Virtex-4QV FPGA family

23

## The combination of the XTMR methodology and configuration memory scrubbing provides an elegant and cost-effective method to ensure reliable operation for almost all critical space applications.

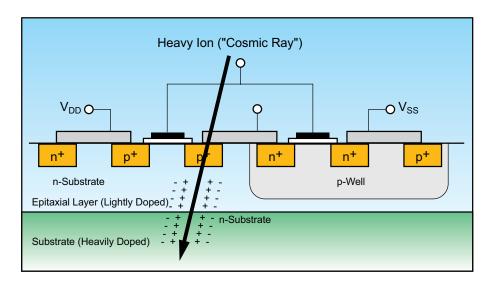

To enable design teams to use reconfigurable FPGAs in space, Xilinx tackled multiple technical challenges:

- Make the CMOS silicon immune to latchup induced by strikes of heavy ions (a.k.a., "cosmic rays")

- Create a high pin-count package that meets the unique requirements of space deployment

- Screen all devices to MIL-PRF-38535 Class V requirements

- Develop a range of upset mitigation techniques backed up by tools and IP

Ionizing particles in space can strike the electronic systems of a spacecraft and produce currents in a device's silicon junctions that can induce latchup of the parasitic transistors inherent in all CMOS integrated circuits. Latchup is a significant concern for designers because it results in high current that can kill the device.

To provide immunity against destructive latchup, Xilinx fabricates radiation-tolerant Virtex-4QV FPGAs on special wafers that incorporate a thin, lightly doped epitaxial layer. In the event of a particle strike, the doped substrate effectively limits the length of the charge trail that can contribute to a current spike in active nodes (Figure 1).

For each Virtex-4QV device type, the SEE Consortium verifies latchup immunity at maximum  $V_{\rm CC}$  and operating temperature, subjected to a heavy ion fluence exceeding 1 x  $10^7$  particles/cm², with an effective linear energy transfer (LET) exceeding 125 MeV-cm²/mg.

### **Packaging Considerations**

Space applications impose special requirements on device packaging with regard to thermal cycling and hermeticity. Xilinx has developed a column-grid array (CGA) surface-mount package that meets these requirements while supporting the high pin count of Virtex-4 FPGAs.

For reliable operation in the vacuum of space, semiconductor devices require packaging that can withstand the extreme temperature ranges and thermal cycles encountered outside the thermal conduction of the Earth's atmosphere.

It isn't uncommon for one side of a satellite to broil under the searing radiation of the sun, while the other side suffers the deepest chill of space. Components in an orbiting and spinning satellite can find themselves rapidly cycling between these temperature extremes. In such an environment, differences in the coefficients of thermal expansion between PCB and device pack-

ing point than the solder paste that companies typically use to attach the device to the circuit board. The solder columns flex to absorb the difference in expansion rates of the package and board to greatly extend the operating life of the device.

Hermetic packages encapsulate die, which electrically connect to the package pins through wire bonds. Virtex-4 FPGAs are high pin-count devices and thus can't employ wire-bond packaging. Instead, they use flip-chip packaging, in which solder bumps on the die make direct contact with the package substrate.

For Virtex-4QV FPGAs, we reengineered the device's flip-chip package to

Figure 1 – A mobile charge produced by a heavy ion strike can induce SEU in an FPGA.

age materials can lead to failures in the solder joints that bind the packaged device to its PCB.

To avoid this problem, we package our Virtex-4QV FPGAs with CGA packaging, which addresses the thermal cycling short-comings of traditional surface-mount technologies. An enhancement of BGA technology, CGA packaging uses solder columns, rather than balls, made of a more flexible low-tin solder with a higher melt-

address the thermal cycle-induced stress where the die attaches to the package, as well as to meet the reliability requirements of a hermetic package. Through judicious choice of solder bump and underfill materials, lid material, and lid-attach adhesive, we made sure that Virtex-4QV devices satisfy JEDEC moisture sensitivity level 1, NASA outgassing requirements, and corrosion specs, plus first- and second-level thermal cycle reliability requirements.

To ensure that our Virtex-4QV FPGAs meet reliability standards for space deployment, Xilinx performs conformance certification of each manufacturing lot. Following military performance specifications, we perform a full test suite across the full military temperature range, including dynamic and static burn-in.

In addition, we perform full TCI/QCI screening to MIL-STD-883 test method 5004 (screening 100% of units) and 5005 (destructive stress testing) on a lot-by-lot basis. We subject every assembly lot to destructive physical analysis (DPA) to comply with MIL-STD-1580 requirement 16, which involves the construction analysis of die fabrication, package fabrication, and assembly.

### **Design Techniques for Upset Mitigation**

In addition to making the silicon more resilient to radiation, Xilinx has developed a range of mitigation techniques that designers can employ to further reduce the likelihood that a charged particle strike will affect the operation of our FPGAs in high-radiation environments.

When developing systems that will operate in hostile radiation environments, you must consider the effects of charged particles such as heavy ions or reaction products from neutrons or protons. As these charged particles travel through the FPGA (Figure 1), they can alter the logic state of any static memory element, resulting in single-event upsets (SEUs). An SEU in the configuration memory array can have adverse effects on expected FPGA functionality.

By thoroughly analyzing your system's operating environment and radiation-tolerance requirements, you can choose an approach that economically delivers the required reliability. For example, for a mission-critical application in a harsh environment, you could use a mitigation scheme that combines redundant FPGAs with radiation-hardened configuration management hardware.

On the other hand, consider an orbiting satellite carrying an image processing circuit that powers up only periodically to capture scenes of interest. If the statistical risk of an upset during that short window of operation is acceptably small, you might choose to forego any special mitigation techniques, especially if the worst-case outcome is the corruption of single frame of image data. In this case, the standard configuration process of loading fresh configuration data on each power-up cycle could be a sufficient approach to fixing upsets.

Answering the following questions and understanding the trade-offs between these application requirements will guide you in selecting the appropriate mitigation scheme:

- Is the application error-tolerant?

- What is the expected operating time window?

- What is the FPGA performance requirement?

- What is the FPGA power requirement?

- How cost-sensitive is the application?

- Can the application withstand any possible FPGA downtime? If so, does the single-event functionality interrupt

(SEFI) cross section specified in the data sheet meet the application requirement?

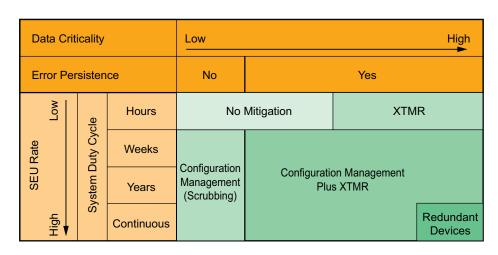

Based on your answers to these questions, you can employ a series of mitigation techniques and IP in your design to reduce the risks that a particle strike will affect the operation of Xilinx FPGAs when they are in high-radiation environments. Figure 2 provides an overview for a mitigation scheme selection based on application requirements and environmental constraints.

### Reconfiguration and Memory Scrubbing

A complete FPGA reconfiguration (or, alternatively, power-cycling the FPGA) is the simplest form of mitigation, as it reloads the configuration memory contents. You can use the FPGA's configuration memory readback function to determine whether the contents have been corrupted by an ion strike and then initiate reconfiguration. Although readback does not interfere with the device's operation, a complete reconfiguration interrupts design function for anywhere from a fraction of a second to a few seconds, depending on clock rates and device size.

Because a given design uses only a fraction of the configuration memory cells in an FPGA, an SEU will likely have no effect on system operation. To avoid unnecessary interruptions caused by complete reconfiguration, you can employ the partial reconfiguration capabilities built into Virtex-4QV FPGAs to reset corrupted bits. The FPGA performs this process (called memory scrubbing) automatically, without hindering the operation of the system.

### Hardware Redundancy

Designers can also fall back on a well-known technique called hardware redundancy, which is critical for high-availability systems – those that can only have minimal unplanned downtime. By employing hardware redundancy, you create two copies of a system so that one copy can keep running

25

Figure 2 – Mitigation scheme matrix

if the other fails. However, the overall system may not be able to distinguish which of the two systems has failed.

To resolve this dilemma, you can add a third copy of the system – known as triplication – to act as a tie breaker. Logic triplication, plus the addition of special voter circuits at key locations in the design, enables your system to continue running even in the presence of an upset.

You'll find that the ample logic and routing resources available in Virtex FPGAs enable you to implement logic triplication within a single device. This capability is the cornerstone of the Xilinx Triple Modular Redundancy (XTMR) methodology. We offer software called the TMRTool that automates the process of building triple redundancy into your designs to simplify this tedious and poten-

design to periodically scrub the circuits and prevent errors from accumulating. Indeed, the combination of the XTMR methodology and configuration memory scrubbing provides an elegant and cost-effective method to ensure reliable operation for almost all critical space applications.

There are extremely rare cases where the combination of XTMR and scrubbing is not enough. For example, if several ions simultaneously (during a single scrub cycle) strike the device's configuration memory and change the logic function on two signals going into the same voter circuit, the voter circuit will misinterpret the false signal as a valid signal and propagate the false signal through the rest of the circuit.

However, for a reasonable scrub rate, even during the most severe space radia-

### Redundant Devices

Depending on the mission criticality of your design and the orbit in which it will be operating, you might choose to use an even more robust mitigation scheme. For example, you can expect that a triplicated design with full-blown configuration management in geosynchronous orbit will experience only one SEFI per device-century. Thus, if the FPGA's SEFI detection and device reconfiguration requires only one second, the result is one second of device outage per 3 billion seconds of operation.

In the unlikely event that your system requires even higher availability (must have extremely short or no downtime), you should employ a design that involves redundant FPGAs plus dedicated configuration management, as well as voting on

| Mitigation Scheme                           | Mitigation<br>Strength | Board Layout<br>Complexity | Ease in Meeting<br>Timing Constraints | Power Consumption | Component Cost |

|---------------------------------------------|------------------------|----------------------------|---------------------------------------|-------------------|----------------|

| No Mitigation (Power Cycling)               | Weak                   | Low                        | Normal                                | Typical           | Low            |

| Configuration Management (Scrubbing)        | Medium                 | Low                        | Normal                                | Typical           | Low            |

| XTMR                                        | Medium                 | High                       | Reduced                               | ~3x Typical       | Medium         |

| XTMR + Configuration Management             | Strong                 | High                       | Reduced                               | ~3x Typical       | Medium         |

| Redundant Devices + Confguration Management | Strongest              | Medium                     | Normal                                | ~2-4x Typical     | High           |

Table 2 – Performance overview of mitigation schemes

tially error-prone task. Used in conjunction with the ISE<sup>TM</sup> software design tool suite, the TMRTool will partially or fully triplicate a design, insert voters, and synchronize feedback path loops. TMRTool also enables the insertion of custom-triplicated design modules.

XTMR by itself is not completely foolproof. As systems fly through space, they will accumulate errors that will adversely affect their operation. During system operation, the probability of system error increases exponentially as upsets accumulate in the system and defeat the device's voter circuits.

To address error accumulation before it becomes a problem, use a combination of XTMR and memory scrubbing in the tion conditions (a 90% worst-case solar flare), the probability of this happening is lower than the likelihood of a SEFI – the upset of a control bit that results in the persistent interference of the normal operation of the circuit.

A SEFI typically results in the loss of one or more of the following: configuration capability, power on reset ability, JTAG functionality, a region of configuration memory, or the entire configuration. Recovering from a SEFI requires reconfiguring your FPGA.

You can improve scrubbing by adding the ability to detect SEFIs. Thus, fullblown configuration management combines transparent readback and scrubbing plus SEFI detection. the outputs of the FPGAs. Table 2 shows the trade-offs that can guide your choice of mitigation schemes.

Xilinx takes great pride in introducing space-grade variants of our commercial devices to bring advanced functionality to designers in the aerospace and defense industries. This functionality allows you to meet payload and power requirements and integrate more advanced functionality into your designs. It also gives you the unique flexibility to make changes to your designs late in the development process and even in space, if required. And as you plan to expand the possibilities of space exploration, Xilinx continues its commitment to helping you make those possibilities a reality.

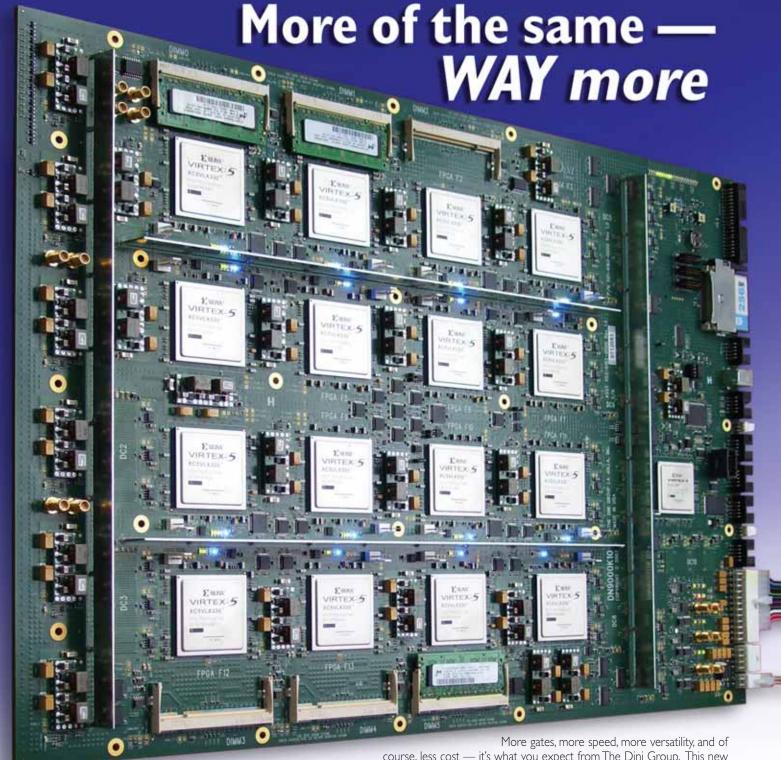

course, less cost — it's what you expect from The Dini Group. This new board features 16 Xilinx Virtex-5 LX 330s (-1 or -2 speed grades). With over 32 Million ASIC gates (not counting memories or multipliers) the DN9000K10 is the biggest, fastest, ASIC prototyping platform in production.

User-friendly features include:

The

Group

- 9 clock networks, balanced and distributed to all FPGAs

- 6 DDR2 SODIMM modules with options for FLASH, SSRAM, QDR SSRAM, Mictor(s), DDR3, RLDRAM, and other memories

- USB and multiple RS 232 ports for user interface

- 1500 I/O pins for the most demanding expansion requirements

Software for board operation includes reference designs to get you up and running quickly. The board is available "off-the-shelf" with lead times of 2-3 weeks. For more gates and more speed, call The Dini Group and get your product to market faster.

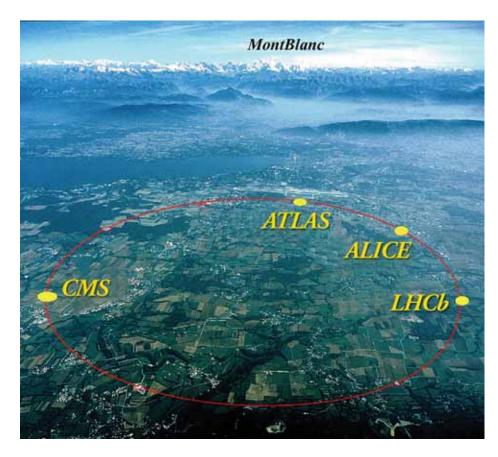

## CERN Scientists Use Virtex-4 FPGAs for Big Bang Research

How 120 Xilinx FPGAs help scientists understand the big bang and gain insight into the fundamental building blocks of matter.

by Peter Alfke

Distinguished Engineer

Xilinx, Inc.

peter@xilinx.com

Volker Lindenstruth

Professor/Chair of Computer Science

Kirchhoff Institute for Physics, University Heidelberg, Germany

voli@compeng.de

In a tunnel underneath the French-Swiss border, scientists at CERN, the European laboratory for particle physics, are on the verge of conducting an experiment called ALICE (A Large Ion Collider Experiment).

They will use the world's most powerful particle accelerator to accelerate two streams of heavy lead (Pb) ions very close to the speed of light and make them collide head-on, attempting to recreate conditions believed to exist shortly after the big bang.

CERN scientists expect that each collision will release an enormous amount of energy and create a local temperature of  $10^{12}$  °C – a hundred thousand times higher than the core of our sun.

When the heavy ions collide, CERN scientists expect the collision will also generate a vast number of subatomic particles flying in all directions. CERN scientists hope that by tracing the paths of these particles, they can discover answers to many of the deepest questions in physics.