Xilinx 7 Series: FPGAs

Make Play for Logic IC Dominance

#### **INSIDE**

Xilinx Rad-Hard FPGA Reaches for the Stars

Biometrics App Rides Reconfigurable Hardware

How to Maintain Repeatable Results in Xilinx FPGA Designs

**Timing Constraints Tutorial**

ISE Design Suite 12.2 Tips 4th-Generation Partial Reconfiguration

### Design Platforms Accelerate Application Success

Development kits help ramp up new Spartan®-6 or Virtex®-6 FPGA designs

Avnet Electronics Marketing introduces three new development kits based on the Xilinx Targeted Design Platform (TDP) methodology. Designers now have access to the silicon, software tools and reference designs needed to quickly ramp up new designs. This approach accelerates time-to-market and allows you to focus on creating truly differentiated products.

Critical to the TDP methodology is the FPGA Mezzanine Card (FMC) from the VITA standards body. Avnet has collaborated with several industry-leading semiconductor manufacturers to create a host of FMC modules that add functionality and interfaces to the new baseboards, allowing for easy customization to meet design-specific requirements.

Learn more about the new Spartan-6 and Virtex-6 FPGA baseboards and FMC modules designed by Avnet at www.em.avnet.com/drc

#### New baseboards for Spartan®-6 and Virtex®-6 FPGAs

- » Spartan-6 LX16 Evaluation Kit

- » Spartan-6 LX150T Development Kit

- » Virtex-6 LX130T Development Kit

#### **New FMC Modules for Baseboards**

- » Dual Image Sensor FMC

- » DVI I/O FMC

- » Industrial Ethernet FMC

More are soon to be released!

Accelerating Your Success™

#### Xcelljournal **PUBLISHER** Mike Santarini mike.santarini@xilinx.com 408-626-5981 **FDITOF** Jacqueline Damian ART DIRECTOR Scott Blair Teie, Gelwicks & Associates DESIGN/PRODUCTION 1-800-493-5551 ADVERTISING SALES Dan Teie 1-800-493-5551 xcelladsales@aol.com INTERNATIONAL Melissa Zhang, Asia Pacific melissa.zhang@xilinx.com Christelle Moraga, Europe/ Middle East/Africa christelle.moraga@xilinx.com Miyuki Takegoshi, Japan miyuki.takegoshi@xilinx.com REPRINT ORDERS 1-800-493-5551 www.xilinx.com/xcell/ 2100 Logic Drive San Jose, CA 95124-3400 Phone: 408-559-7778 FAX: 408-879-4780 © 2010 Xilinx, Inc. All rights reserved. XILINX the Xilinx Logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trade marks are the property of their respective owners. The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilinx makes no warranties, express,

implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against Xilinx for any loss, damage, or

#### Teens to Technologists: Thanks for a Great Childhood

've seen many things over my years covering the electronics industry, but at the Design Automation Conference this past June, I witnessed a first: a group of EEs and EDA folks, eyes abrim with tears of pride. What could cause such a reaction in what would otherwise seem a prosaic event? No, it wasn't a leak from one of the foundry demos, nor an announcement that all EDA tools will henceforth be government subsidized. In fact, the moment came in the closing seconds of an event called "High School Panel: You Don't Know Jack," when four very bright teen panelists looked over the crowd and then did the unexpected: thanked them. "Thank all of you for the chips and technologies you create—thank you for making my childhood so great," said one of them, without a hint of irony. The gesture prompted engineers from Broadcom, Qualcom, Nvidia, Cadence and Synopsys alike...and yours truly...to all tear up.

"High School Panel: You Don't Know Jack" is becoming a regular highlight of the Design Automation Conference's Pavilion Panel series. As in years past, this year's panel featured Jasper Design Automation CEO Kathryn Kranen interviewing four teenagers (two girls and two boys) about their technology usage, what products are in, what products are out and what features they would like to see in future gadgets. The panel is meant to give attendees a glimpse into the technology usage of this finicky yet vitally important set of consumers and purchasing influencers. This year's foursome was exceptionally impressive and surprisingly gracious. Over years of exposure to technology and social media, these kids have become master multitaskers while still maintaining stellar GPAs (three are off to prominent colleges, while the fourth has one year of high school left).

If you are the parent of a teen, you probably won't find it too shocking that all four panelists described how, from the moment school lets out, they immediately connect to the Internet, mostly via laptops. "I have to stay connected," said one boy. A fellow panelist boots her laptop and downloads the photos she took that day from her cell phone or camera. She opens the photo files in Adobe Photoshop to airbrush any skin blemishes and then downloads those modified pictures onto her Facebook page. All four panelists said they have tens of photo albums on Facebook and have friends with hundreds. Increasingly, they are adding video to their Facebook profiles or launching their own YouTube channels. Facebook is the hub of their social lives because it allows them, as one panelist summarized, "to see what my friends are doing and what outings I was not invited to attend."

The kids gave Facebook, Twitter, YouTube and Hulu big thumbs-up, while giving thumbs-down to the once popular MySpace, which panelists said has turned into a site to merely hear band demos. Panelists liked the iPhone, even though none of them own one because of the relatively high price of the phone and the access plan. But they did not like the iPad—"it's just a big iPod Touch that I can't fit into my pocket," said one panelist. Panelists also said they prefer laptops over desktops but note that desktops are more reliable and are upgradable, which is good for power gaming. They had mixed feelings about TV, indicating they almost never watch TV on the flat-screen anymore but instead catch their favorite shows at a time of their choosing on the Web, typically via Hulu or YouTube.

The technology improvements these young people would most like to see are largely in line with the top IC and system design challenges of the day. Longer battery life topped the list. A close second was devices and applications that better facilitate multitasking. "I have six different IM/chats that I use regularly and it's hard to use all those at once," said one panelist. "I'd like to have them all in one place."

What all these data points mean, I'll leave you to interpret. But certainly one thing is clear. The technology you create is having a remarkable effect on our youth and, seemingly, the future they will march into. And if these DAC panelists are any indication, it's a future that we can all be proud of.

Mike Santarini Publisher

#### VIEWPOINTS

### Letter from the Publisher Teen Panelists at DAC Say Thanks for the Memories...3

#### **Cover Story**

Xilinx Redefines State of the Art with New 7 Series FPGAs

#### XCELLENCE BY DESIGN APPLICATION FEATURES

#### Xcellence in A&D

New Xilinx Rad-Hard FPGA Reaches for the Stars...12

#### **Xcellence in Automotive**

Multiple MicroBlazes Ease Integration in Real-Time System...18

#### **Xcellence in ISM**

Biometrics May Be Killer App for Dynamic Partial Reconfiguration...24

#### **Xcellence in Communications**

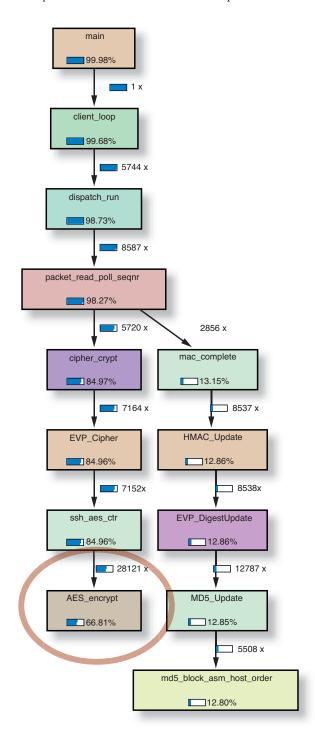

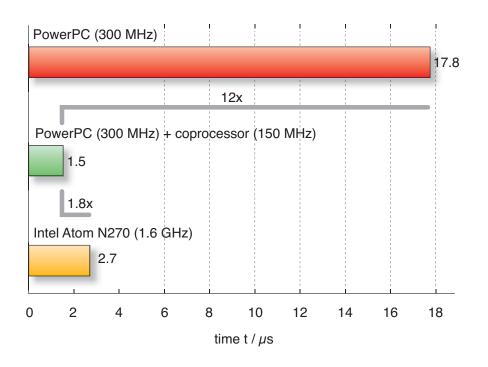

A Better Crypto Engine, the Programmable Way...32

#### **Xcellence in Wireless Communications**

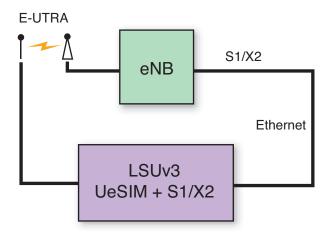

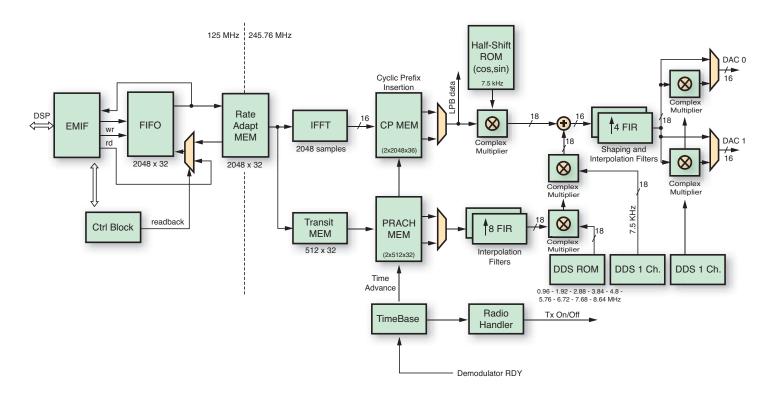

LTE Simulator Rides

Xilinx Virtex-5 FPGAs...36

#### THE XILINX XPERIENCE FEATURES

**Xperts Corner** Maintaining Repeatable Results in Xilinx FPGA Designs...40

Xplanation: FPGA 101

A Tutorial on Timing Constraints...46

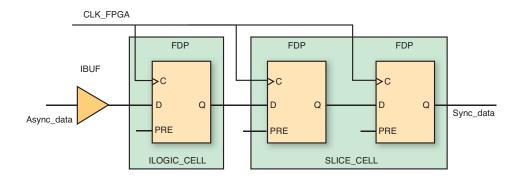

**Xplanation: FPGA 101**

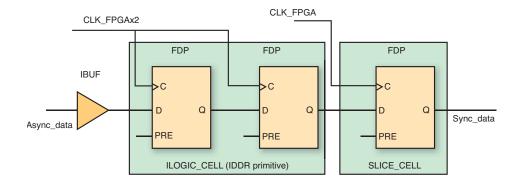

Simplifying Metastability with IDDR...52

#### XTRA READING

**Xtra**, **Xtra** The latest Xilinx tool updates and patches, as of July 2010...55

**Are You Xperienced?** Training at the cusp of the programmable imperative...**58**

**Xamples...** A mix of new and popular application notes...**60**

**Tools of Xcellence** A bit of news about our partners and their latest offerings...62

**Xclamations!** Share your wit and wisdom by supplying a caption for our wild and wacky artwork...66

Xcell Journal recently received 2010 APEX Awards of Excellence in the categories "Magazine & Journal Writing" and "Magazine & Journal Design and Layout".

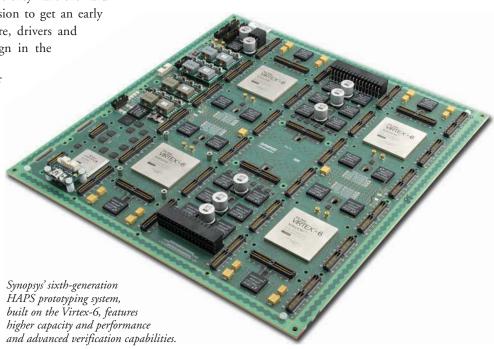

# Xilinx Redefines State of the Art With New 7 Series FPGAs

by Mike Santarini Publisher, Xcell Journal Xilinx, Inc. mike.santarini@xilinx.com

FPGAs have advanced remarkably ever since they first hit the market in the mid-1980s as 1,500-ASIC-gate-equivalent devices. Two decades later, with the launch of Xilinx's new 7 series, the FPGA stands poised to fulfill its historic promise of one day displacing ASICs as the electronics industry's mainstream logic IC. With the introduction of the 7 series FPGAs, Xilinx® is transitioning from being just a PLD maker to a premier supplier of logic ICs by providing lower total cost of ownership for low- to medium-volume applications and equivalent total cost of ownership for higher-volume applications traditionally addressed by ASICs and ASSPs. What's more, this total-cost-of-ownership benefit combines with the traditional FPGA advantages of faster time-to-market and risk reduction. Together, all of these factors mean that FPGAs are emerging as the de facto logic IC solution for most applications.

As part of the 7 series release, Xilinx will bring to market an unprecedented 2 million-logic-cell FPGA, which is 2.5x the capacity of the largest Virtex®-6 device. Depending on whom you ask, how you design and what application you are targeting, that means the largest 7 series FPGA delivers the clout of anywhere from 15 million to 40 million equivalent ASIC gates. Thus, in the last 10 years, Xilinx has increased the capacity of its FPGAs by more than 30x at equivalent price points of the devices it produced 10 years ago.

But a huge capacity increase is only the beginning of the 7 series story. These beefy FPGAs run faster than the previous-generation Virtex-6, but at half the power consumption.

"ASICs are not dead, nor will they die entirely, but they really are only viable for a very small number of applications that have the very highest volumes," said Moshe Gavrielov, Xilinx's chief executive officer. "Where once you had to ask why would you go with an FPGA, today you have to seriously ask yourself why wouldn't we use an FPGA?"

The new 7 series is the first Xilinx FPGA family created entirely under the watch of Gavrielov, who joined the company in late 2007 after serving as a CEO of Verisity, a design tool provider. Before that, he worked for many years in management at ASIC house LSI Logic. Gavrielov has set Xilinx on an aggressive path to growth, with the main driver being an industry-leading line of FPGAs, which culminates in the 7 series, and the Targeted Design Platform strategy (see cover story, *Xcell Journal* No. 68; <a href="http://www.xilinx.com/publications/archives/xcell/Xcell68.pdf">http://www.xilinx.com/publications/archives/xcell/Xcell68.pdf</a>).

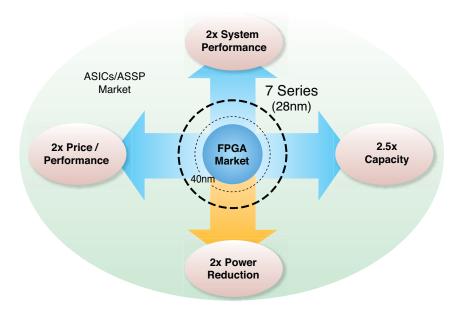

To enable this growth, the 7 series boasts several significant refinements, including a new unified and scalable architecture, a primary emphasis on power reduction and massive capacity, enabling better overall system performance (Figure 1).

#### Starts With a Unified Architecture

Up until the introduction of the 7 series, Xilinx's FPGA landscape has primarily centered on the high-performance Virtex family and the high-volume Spartan® family. When Xilinx originally introduced these two lines in the late 1990s, the Virtex and Spartan devices used radically different architectures. From a user perspective, the two families had notable differences, and so did the IP for each device and the design experience in working with them. If you wanted to increase the size of your end product from a Spartan design to a Virtex design or vice versa, the differences in architecture, IP and pin counts became apparent.

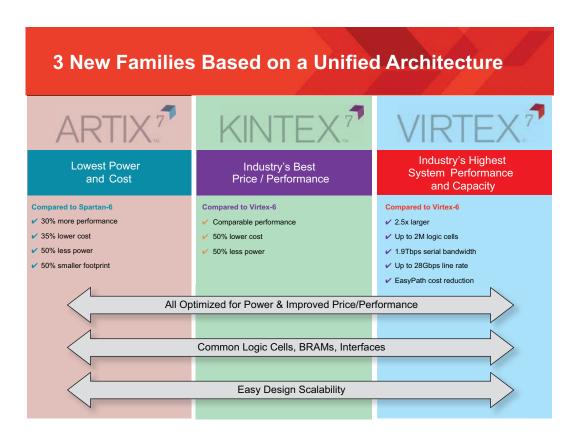

But with the unified architecture of the 7 series, those variances disappear. With the 7 series, Xilinx will not be introducing a new device under the Spartan name and has instead developed a complete lineup of FPGAs—primarily in three families, from lowest cost to highest performance—all based on the familiar Virtex FPGA architecture (Figure 2).

Virtex remains the moniker for the 7 series' highest-end FPGAs. This new Virtex-7 family delivers breakthrough capacity with up to 2 million logic cells and better than twofold system performance improvement over previous generations.

For a smooth transition from Spartan-6 FPGAs in the low-cost market, the new Artix<sup>TM</sup>-7 family leads the industry in price, power and small form factor for cost-sensitive, low-power applications.

The final member of the trio smoothly fills the space between the Virtex-7 on the high end and the Artix-7 line at the mass-market level. The Kintex<sup>™</sup>-7 introduces a new price/performance advantage and gives Xilinx a platform for displacing main-stream ASICs and ASSPs.

Victor Peng, senior vice president for programmable platforms development at in a unified 7 series architecture, customers will find it much easier to migrate their designs across the families, enabling better leverage of their development investments in IP."

They will also be able to migrate design blocks in the 7 series to the logic portion of the upcoming Extensible Processing Platform (see cover story, *Xcell Journal* No. 71; <a href="http://www.xilinx.com/publications/archives/xcell/Xcell71.pdf">http://www.xilinx.com/publications/archives/xcell/Xcell71.pdf</a>), because the EPP and 7 series devices all use the same Virtex logic architecture structure. Further, the common logic architecture supports

Figure 1 – The new Xilinx 7 series pushes the boundaries for FPGAs.

Xilinx, predicts that having a solid midrange product in the form of Kintex-7 will allow Xilinx to offer a comprehensive FPGA lineup that is more highly application targeted.

"In previous generations, Xilinx would fill that middle ground by creating a higher-performance, higher-capacity version of Spartan and at the same time a lower-cost, lower-capacity and lower-performance version of Virtex," said Peng. "But the Spartan and Virtex architectures, IP and pin counts were very different. With the Artix, Kintex and Virtex families all built the ARM AXI4 (Advanced Extensible Interface) protocol. This means that Xilinx's internal IP developers and hundreds of IP partners can more easily target and implement AXI-compliant IP on Xilinx FPGAs. Chances are many customers have their own IP already built to comply with AXI, further facilitating moving designs from ASIC or ASSP to 7 series FPGAs.

Peng notes that in addition to offering great benefits for customers and IP partners, the unified architecture allows Xilinx to become more focused and aligned in all product development efforts going forward. "It means our organization can focus on doing things once rather than twice," said Peng.

#### 28-nm HPL: Right Mix of Power, Capacity and Performance

With the new 7 series family, Xilinx has also modified its manufacturing strategy to better align with the realities of modern IC design by choosing to implement its devices on a newly refined high-k metal gate (HKMG) high-performance, low-power (HPL) process with Taiwanese foundry TSMC.

Traditionally, FPGA vendors have implemented their designs on the highest-performance variation of each new silicon process as fast as foundries could make the processes available. However, starting with 90-nm process technologies, leakage started to become a big problem. It only got worse at 65 nm and 40 nm. At the 28-nm process node, if unaddressed, leakage current can account for well over 50 percent of a device's power consumption. In addition to using power when a device isn't running, during operation leakage creates extra heat, which in turn increases the leakage. Especially in continual-use, high-performance applications, this vicious cycle can lead to shortened device lifetimes and catastrophic IC failures. This greatly impacts the viability of using an FPGA in a given application as well as the reliability of a system.

The foundries have made remarkable strides to stem the leakage in their high-performance processes at 28 nm. Xilinx worked with its new foundry partner, TSMC, to refine the foundry's new HKMG HPL process for the 7 series FPGA, emphasizing low power combined with the usual gains in capacity and system performance when shrinking the geometry.

Peng said that by going with the HPL rather than the HP process, Xilinx will reduce static power by 50 percent with less than a 3 percent impact on performance. The use of the HPL process combined with the comprehensive power-savings enhancements implemented in the 7 series results in a 50 percent reduction in total power compared with devices at the same densities in the last generation of products.

The 50 percent lower-power benefit gives design teams two options, said Peng. "You either run a similar-size Virtex-6 or Spartan-6 design at half the power in the 7 series, or you can double the size of the logic functions in your [new] design and remain at your previous power budget," he said. "By going with the HPL process, we have given customers much more usable performance as well as more logic gates to implement more functions in their designs."

achieve performance is through higher integration and efficiency, as opposed to simply making things move faster," said Gavrielov. "With today's processes, if you just make things faster, you drain more power and create thermal problems—which degrades power and performance. We need to pay a lot of attention to end-customer applications and ensure we strike the right balance between meeting low-power needs while simultaneously meeting

even fan or liquid cooling and related power circuitry to the end system.

HPL is just one of about a dozen technologies Xilinx employs to reduce power in the 7 series, Gavrielov said. For example, Xilinx reduced configuration logic voltage from 2.5 to 1.8 V, and optimized each of the hard blocks—DSP, Block RAM, SelectIO<sup>TM</sup> and others—using HVT, RVT and LVT transistors to reduce static power while optimizing performance and area. As a result, each

Figure 2 – The three new families in the 7 series unified architecture offer users a smooth path from lowest cost to highest volume.

Xilinx CEO Gavrielov notes that by choosing the higher-capacity but lower-power variant of the 28-nm process, Xilinx is leading the FPGA industry in aligning with the microprocessor industry. Almost a decade ago, MPU makers realized that cranking up clock rates in these newer process geometries would only create extremely leaky, thermally challenged devices that would fail.

"We learned from the processor side of the semiconductor business that given the realities of processes today, the best way to the system performance needs of the application. We believe we will deliver a great value proposition with the 7 series FPGAs that will delight customers."

Peng notes that had Xilinx gone with an HP process for an incremental clock speedup, the significant increase in power for the fairly insignificant increase in performance would have burdened users with paying extra attention to designing around power and thermal issues. They might have incurred extra systems costs associated with adding elaborate heat spreading or DSP slice consumes 1/12 the power of the equivalent logic implementation. By optimizing the ratio of these tightly integrated hard blocks throughout the FPGA fabric, Xilinx was able to achieve the greatest performance and lowest power while preserving flexibility.

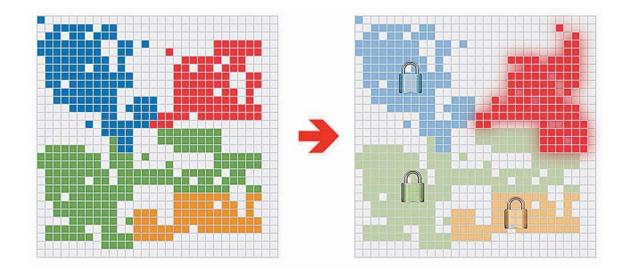

Customers can also use the intelligent clock-gating feature introduced in the ISE® Design Suite 12 to give their 7 series designs an additional 20 percent reduction in dynamic power consumption. And finally, users can get a dramatic savings in power consumption by leveraging Xilinx's fourth-

### The Virtex-7 family takes the industry's most successful FPGA architecture to new heights by doubling the capacity and boosting system performance at 50 percent lower power.

generation partial-reconfiguration methodology to effectively "turn off" portions of the design when they are not in use.

The upshot? By going with an HPL process, taking other power reduction measures and rolling out its new devices in a unified architecture, Xilinx now offers a comprehensive line of FPGAs, from the high-volume low-power lines to those boasting the highest system performance and capacity the industry has seen to date.

#### The Virtex-7, Kintex-7 and Artix-7 Families

Patrick Dorsey, senior director of marketing at Xilinx, said the three new families in the 7 series will allow Xilinx to capture an even greater share of the ASIC and ASSP market and penetrate even more deeply into a broader number of vertical markets, from low-powered medical devices to the highest-performing wired and wireless networking equipment.

At the entry level, "The new Artix-7 family provides the lowest absolute power and cost, with small-form-factor packaging," said Dorsey. Densities range from 20,000 to 355,000 logic cells. The devices are 30 percent faster and consume 50 percent less power than Spartan-6 FPGAs at 35 percent lower price points. When moving from Spartan-6 FPGAs to Artix-7 devices, designers can expect up to 85 percent lower static power and up to 35 percent lower dynamic power consumption.

GTP serial transceivers support line rates up to 3.75 Gbits/second. Other key features include 3.3-volt-capable I/O for interfacing to legacy components and wirebond packaging for the lowest cost, with optional chip-scale packaging for the smallest form factor and 1.0-mm ball spacing for low-cost PCB manufacturing.

Dorsey said that because the new family is based upon the Virtex architecture, it also now includes many of the advanced features of the Virtex family that were not available in the Spartan line. For example, the Artix-7 includes an enhanced System Monitor ana-

log function, now called XADC (analog capability), to allow users to monitor the functionality, temperature, touch sensor, motion control and other real-world analog activities in the system. The integrated XADC technology will enable a whole new class of mixed-signal applications.

Further, with these refined specs, the Artix-7 FPGAs better target the low-power performance requirements for applications such as ultrasound equipment. The devices also now address the small-form-factor, low-power requirements of lens control modules for high-end commercial digital cameras as well as next-generation automotive infotainment systems driven by 12 V. Artix-7 devices also meet the strict SWAP-C (size, weight, power and cost) requirements of military avionics and communications applications.

#### **Kintex-7 FPGA Family**

Dorsey said that with the new midrange family, Kintex-7, Xilinx now provides FPGAs with the best price-for-performance on the market. "With the Kintex-7 family, we offer devices that are less than half the price and power consumption of Virtex-6 FPGAs but equal in performance and functionality," said Dorsey.

The Kintex-7 devices will be especially welcomed in applications that require costeffective signal processing, he said. That's because they offer abundant DSP slices (from 120 to 1,540), up to 5,663 kbits of distributed static RAM and 28,620 kbits of internal block static RAM, and between four and sixteen 10.3-Gbps GTX serial transceivers. Dorsey said Kintex-7 devices will be equally attractive to Virtex users seeking a lower-cost alternative as well as to customers who have traditionally used Spartan FPGAs but are scaling their designs to the next level of system performance. Indeed, with logic densities ranging from 30,000 to 400,000 gates and with 40 percent higher performance than Artix-7 FPGAs, Kintex-7 devices equal the performance of Virtex-6 and are significantly faster than Spartan-6 FPGAs.

Dorsey said the Kintex-7 parts are ideal for implementing Long Term Evolution (LTE) wireless radio and baseband subsystems. And thanks to the recent release of Xilinx's fourth-generation partial-reconfiguration technology, 7 series customers can further reduce power and cost, for wide deployment in femto, pico and mainstream base stations. The serial connectivity, memory and logic performance of these devices is a good fit for high-volume wired communications as well, Dorsey added, citing equipment such as 10G passive optical network (PON) optical line terminal (OLT) line cards that bring high-speed networking to the neighborhood and home as one example.

In addition, Kintex-7 FPGAs are also suited for use in high-definition 3D flatpanel displays in consumer electronics markets; video-over-Internet Protocol bridges that enable next-generation broadcast videoon-demand systems; and high-performance image processing required for military avionics and ultrasound equipment that can support up to 128 high-resolution channels.

#### **Virtex-7 FPGA Family**

For its part, the high-end Virtex-7 family takes the industry's most successful FPGA architecture to new heights by delivering more than a doubling in capacity and 30 percent faster system performance along with 50 percent lower power than the Virtex-6 FPGA predecessors.

Dorsey said the Virtex-7 FPGAs are well suited for communications systems requiring the highest performance, capacity and bandwidth. With its Virtex-7T and Virtex-7XT variants, this FPGA line boasts ultrahigh-end devices that push the limits of FPGA technologies in terms of the number and performance of embedded serial transceivers, DSP slices, memory blocks and high-speed I/O to establish new benchmarks for the industry.

Virtex-7 devices offer up to 36 GTX 10.3-Gbps serial transceivers, ultrahigh-end logic capacity with as many as 2 million

logic cells and the highest parallel I/O bandwidth in the industry, with up to 1,200 SelectIO<sup>TM</sup> pins. This I/O configuration enables the greatest number of parallel banks of 72-bit DDR3 memory available on the market, supporting 2,133 Mbps.

Meanwhile, the new Virtex-7XT devices also provide the highest serial bandwidth in a single FPGA, with up to 72 GTH transceivers at 13.1 Gbps, or 80 GTH and GTX transceivers (24 running at 13.1 Gbps and 56 at 10.3 Gbps, respectively). In addition, the devices feature higher DSP-to-logic ratios for greater throughput, with up to 3,960 DSP slices at 600 MHz delivering 4.7 TMACs. Also, the 7XT FPGAs have higher on-chip BRAM-to-logic ratios with up to 65 Mbits, for low-latency data buffering. Dorsey said that Xilinx will eventually add devices with 28-Gbps transceivers to this family; the release details are forthcoming.

The new Virtex-7 FPGAs target the highest-performance wireless, wired and broadcast infrastructure subsystems, said Dorsey. The teraMACC signal-processing capabilities of Virtex-7 FPGAs enable advanced radar and high-performance computing systems. Product developers can replace ASICs and multichip-set ASSP solutions with single-FPGA implementations of 100GE line cards to increase bandwidth, while simultaneously lowering the power and cost. Other applications include 100-Gbit Optical Transport Network (OTN) muxponders for integrated multiplexer/transponder applications, 300G Interlaken bridges and 400G optical network cards.

In addition, these ultrahigh-end devices provide the logic density, performance and I/O bandwidth needed to build next-generation test and measurement equipment. For systems where ASIC production is justified, Virtex-7 FPGAs enable designers to use fewer devices during prototyping and emulation in order to lower cost and reduce interconnect/design complexity.

#### EasyPath—a Further Cost Alternative

Dorsey said the company's EasyPath<sup>TM</sup> program extends the value of Xilinx 7 series FPGAs to provide the lowest total cost of ownership for medium- to higher-volume

applications on the order of 100,000 units. This total cost of ownership requires that customers assume only the development and unit cost. In addition, they receive the full advantages of time-to-market and risk reduction that FPGAs offer. This further bolsters Xilinx's value as a strategic logic IC supplier.

EasyPath provides a cost reduction by coupling Xilinx's FPGA manufacturing process to the customer's design. This results in the same silicon with the same features, but only guaranteed to work with a given design. Dorsey said that EasyPath-7 takes six weeks to complete from design freeze and offers a guaranteed 35 percent cost reduction and no minimum-order quantity, with no customer engineering effort required—all for a \$300,000 nonrecurring engineering cost

"Now you have the peace of mind that once you design the FPGA, you can get to lower cost by targeting either Kintex-7 or Artix-7 and, if further cost reductions are necessary to support higher volumes, by going to EasyPath-7," said Dorsey. "What's more, if you've already completed your FPGA design and want to go with EasyPath, you can let your purchasing department handle the rest, since no further customer engineering resources are required."

#### **Next-Generation Targeted Design Platforms**

Along with announcing the new family, Xilinx is also launching a second generation of Targeted Design Platforms, application-specific design aids which the company first rolled out in 2009 in tandem with the release of the Virtex-6 and Spartan-6 FPGAs. Xilinx's Targeted Design Platform strategy gives system designers access to simpler, smarter design methodologies for creating FPGA-based solutions through the integration of five key elements: FPGA devices, design tools, IP, development kits and targeted reference designs.

Early-access ISE Design Suite software supporting the new FPGA families has shipped to a limited number of early-adopter customers and partners. First shipments of the devices will begin in the first quarter of 2011.

For more information on the 7 series FPGAs, visit <a href="http://www.xilinx.com/technology/roadmap/7">http://www.xilinx.com/technology/roadmap/7</a> series-fpgas.htm.

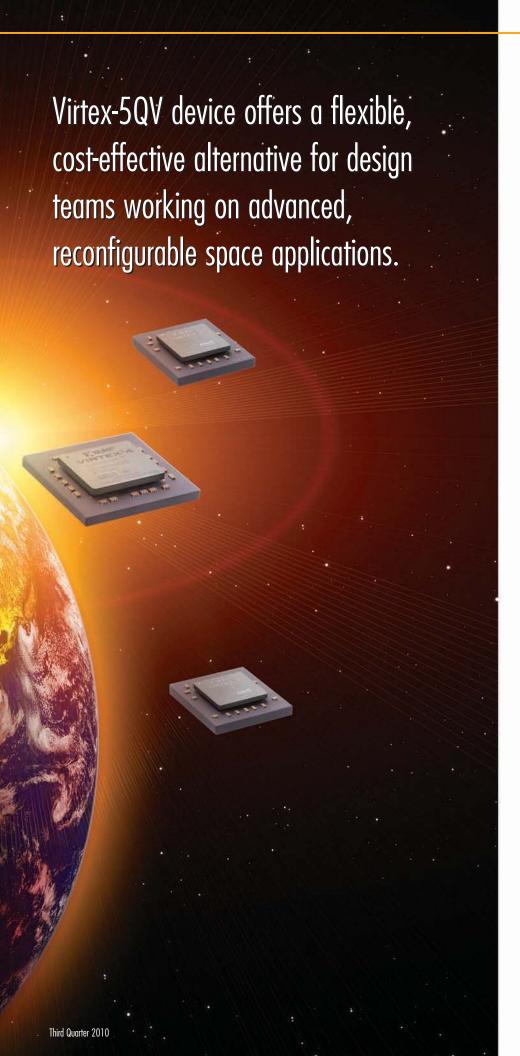

## New Xilinx Rad-Hard FPGA Reaches for the Stars

by Maury Wright President WDC Marketing

Electronic systems designs headed to space naturally require high reliability, but the design task is further complicated by exposure to radiation that can cause sporadic circuit failures. From a functional perspective, FPGAs with inherent reconfigurable attributes are a perfect match for space. FPGAs enable a single system to perform multiple tasks and let mission teams remotely reconfigure a system, either fixing a bug or adding new functionality. Now Xilinx® has an FPGA—the Virtex®-5QV—that is radhard and can deliver the full benefits of programmability to space programs. The design teams get an off-the-shelf solution with all the advantages of a 65-nanometer commercial SRAM-based FPGA, including ready access to development and prototyping tools.

It's hard to underestimate the value an FPGA can offer in an application such as space-bound systems. Once a system, satellite, rocket or spacecraft is deployed, there is little or no ability to make hands-on changes to it, so the reprogrammability of an FPGA is a huge benefit. To be sure, microprocessors and microcontrollers can also be reprogrammed. But FPGAs excel in data-flow applications where functions such as packet inspection or signal-processing algorithms implemented in hardware logic offer far more processing throughput than do traditional microprocessors. And the FPGA hardware can be easily reconfigured to support new algorithms.

Given the advances in circuit density and the mix of hardwired IP blocks and configurable logic, the latest FPGA technologies can capture the bulk of a system's functionality. For example, the Virtex-5QV includes Ethernet MAC functions and high-speed transceivers to go along with DSP slices and configurable logic (for details on the FPGA capabilities, see sidebar, next page).

A rad-hard IC that's derived from a commercial FPGA family also offers significant benefits in the development process. Design teams can do development work with readily available commercial devices and development tools and then seamlessly move the design to the rad-hard target system platform at any point in the development process.

#### **Space Presents Reliability Challenges**

To deploy FPGAs in space applications, however, designers have to understand the environment and learn how to mitigate issues that affect reliability. For example, a number of radiation-induced effects have been identified as a problem area for space-based designs. The list includes single-event upsets, single-event functional interrupts, single-event latchups, single-

event transients and total ionizing dose effects. (See the second sidebar for more information on these effects.)

Designers working on space applications haven't traditionally had the freedom to use ICs such as FPGAs without carefully considering ways to mitigate radiation effects. Specialty ASIC houses have radiation-hardened IC manufacturing processes. But ASIC design cycles are lengthy and expensive, and the quantity of devices the application will actually need simply doesn't justify the time and effort, given viable alternatives.

The radiation-hardened ASIC processes are also many generations behind state-of-

the-art commercial IC processes. For example, the rad-hard ASICs are still in the 150-nm or less-dense process nodes. Indeed, modern FPGAs offer performance and circuit density that match those of radiation-hardened ASICs, along with much faster development cycles.

#### **Radiation Tolerance and TMR**

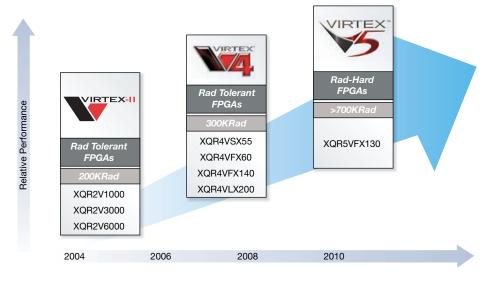

In the past, designers who wanted to use FPGAs have had to combine radiation-tolerant ICs with techniques that further mitigate single-event upset (SEU) effects. Xilinx has long addressed the need for radiation resistance in space-targeted designs. Radiation-tolerant FPGAs such as the

#### Rad-Hard FPGA Delivers State-of-the-Art Benefits

he Virtex-5QV offers a unique value proposition. This FPGA is rad-hard out of the box and also offers state-of-the-art reprogrammable-logic density and hardwired IP blocks. Design teams working on space applications get ASIC-like circuit density without the ASIC NRE costs.

The FPGA includes more than 130,000 logic cells for large, complex designs. The architecture is based on six-input LUTs and the IC employs a diagonal interconnect structure that ultimately packs designs more efficiently in terms of silicon utilization and results in better performance and lower power consumption.

The design is based on the second generation of Xilinx's Advanced Silicon Modular Block (ASMBL<sup>TM</sup>) column-based architecture. ASMBL has allowed Xilinx to produce mixes of configurable logic and hardwired IP that are optimized for specific applications.

The Virtex-5QV includes 320 Enhanced DSP slices to complement the programmable logic. Each slice includes a 25 x 18-bit multiplier, an adder and an accumulator. Designers can cascade the IC's 36-kbit Block RAM elements to produce large, general-purpose memory arrays. The device includes 298 such blocks. Each block can also be configured as two 18-kbit blocks, so there is little wasted silicon for applications requiring smaller RAM arrays.

For networking and I/O operations, the Virtex-5QV includes a number of hardwired IP blocks. Six Ethernet media-access controller (MAC) functions can operate in 10-, 100 and 1,000-Mbps modes. Eighteen RocketIO<sup>TM</sup> transceivers support data transfers at rates ranging from 150 Mbps to 3.125 Gbps. The MACs can use some of the RocketI/O transceivers for physical-layer (PHY) connections or link to external PHYs via a soft Media Independent Interface implemented in programmable logic.

The IC also includes three PCI Express® blocks compatible with the PCI Express Base Specification version 1.1. Designs can implement x1-, x4- or x8-lane channels with each of the three blocks. The RocketIO transceivers are also available for PCI Express I/O.

The device features a number of other functions important in high-performance system designs. Six clock management tiles (CMTs) can each generate clocks that operate up to 450 MHz. Each CMT includes dual digital clock managers (DCMs) and a phase-locked loop (PLL). The DCMs enable zero-delay buffering, frequency synthesis and clock-phase shifting. The PLLs add support for input jitter filtering and phase-matched clock division.

Xilinx will manufacture the IC in a 65-nm copper CMOS process with a 1-V core voltage. A ceramic flip-chip column grid array package will ensure signal integrity. And Xilinx will guarantee operation over the full military temperature range of -55°C to +125°C.

– Maury Wright

## The Virtex-5QV design team aimed to provide intrinsic hardness from single-event upsets and transients to critical elements in the device. A novel latch implementation offers almost 1,000 times the hardness to SEUs of commercial versions of the FPGA.

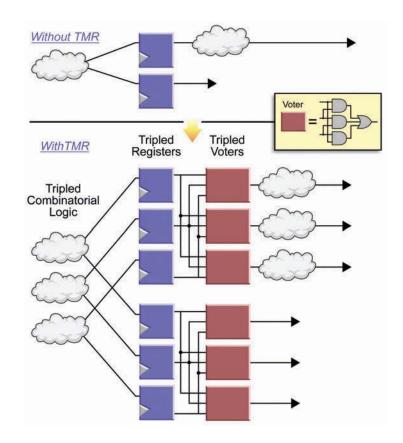

Virtex-4QV have immunity to single-event latchup (SEL), and can withstand a total ionizing dose (TID) up to 300 krads(Si). Xilinx combines these radiation-tolerant ICs with system-level techniques such as triple-modular redundancy (TMR) to ensure reliability. In a TMR design, three separate instantiations of a system perform the same task. A voting circuit compares the results and considers it correct if at least two systems produce the same result.

Xilinx has developed a tool that can greatly simplify the implementation of a TMR methodology. The TMRTool accelerates the design cycle by allowing the design team to focus on design and debug rather than TMR. The tool works seamlessly with any HDL and synthesis tool to automatically build TMR into a design.

The TMRTool also goes beyond baseline TMR functionality. It triplicates all clocks and throughput logic to protect against single-event transients (SETs). It also triplicates feedback logic and inserts majority voters on all feedback paths. And the tool triplicates all outputs and uses minority voters to detect and disable incorrect output paths.

By inserting voters on all feedback paths, the TMRTool overcomes a problem with the technology in designs with finite state machines. In most TMR-based statemachine designs, an SEU that causes an error in one of the three state machines ultimately requires that the state machines be reset for synchronization. But the voters in feedback paths ensure that the state machines remain continuously synchronized and can operate continuously through SEUs.

#### Rad-Hard by Design

While earlier FPGAs such as the Virtex-4QV have been successfully deployed in space applications and have been radiation-tolerant, the new Virtex-5QV was designed

from the ground up with a rad-hard-by-design (RHBD) methodology. The resulting FPGA is truly a rad-hard space-grade IC. Where the Virtex-4QV requires that designers add mitigation, the Virtex 5QV is rad-hard out of the box.

The Virtex-5QV design team's specific goal was to provide intrinsic hardness from

sions of the FPGA. Moreover, the latch is virtually impervious to proton interaction.

#### **Upset Hardening in Hardware**

Effectively obviating the need for TMR at the application design level, the Virtex-5QV design team used a variety of techniques in implementing the underlying

Figure 1 – Xilinx built its latest space-grade FPGA, the Virtex-5QV, to be rad-hard.

SEU, SET and other effects to critical circuit elements in the device. As with all SRAMbased FPGAs, configuration memory controls all aspects of device operation and is therefore critical to reliable operation. The Virtex-5QV design utilizes dual-node latches that control write operations to memory cells. Writes occur only when both latches are enabled synchronously. The implementation offers 1,000 times the hardness to SEUs relative to memory latches in commercial ver-

FPGA memory and circuit elements in the device. Xilinx took special care in hardening the 35 million configuration cells and the 81,920 user flip-flops. Both incorporate a clever self-redundant storage circuit that has double the normal number of transistors. The result is a very low susceptibility to SEU. Xilinx optimized the layout of this important structure by fabricating many variants and subjecting them to inbeam irradiation studies.

In addition, Xilinx made sure that all the clock, data and asynchronous inputs to the flip-flops are protected. These are capable of suppressing single-event transients and prevent them from turning into upsets.

Xilinx employs proprietary methods to protect against SEUs during the critical start-

up period when the FPGA is configured. One result is that designers don't have to take extra steps to ensure the elimination of single-event functional interrupts (SEFIs), which traditionally require an intrusive FPGA restart and reconfiguration. Gary Swift, senior staff engineer for space products

development and radiation testing at Xilinx, said the implementation reduces GEO (geostationary earth orbit) environment SEFI rates by more than two orders of magnitude (relative to the already low once per century for the rad-tolerant Virtex-4QV family) to about than one SEFI fault in 10,000 years. "Interestingly,

#### **Understanding Radiation-Induced Effects**

oing back to the 1950s, engineers have documented the adverse effect that radiation can have on electronic circuits. With the advent of ICs and the constant move to finer process geometries, the potential for radiation-induced errors grew. The impact ranges from soft errors that are easy to detect and correct to actual device failures.

Design engineers working on space applications must prepare for a number of problems.

- A single-event upset (SEU) is a change of state in an IC, such as a change in the value of a memory bit caused by a radiation strike. SEUs are also called soft errors because the instance of an SEU has no long-term effect on the IC and in fact, the soft error can often be found and fixed.

- A single-event functional interrupt (SEFI) is similar to an SEU in that it is typically the result of a single ion strike. But SEFIs result in a temporary instance of some element of the IC not functioning properly. In some cases, an SEFI-induced fault remains until power cycles, and in other cases the condition is truly temporary.

- A single-event latchup (SEL) is a potentially more damaging event typically caused by ions or protons generated by cosmic rays or solar flares. The radiation induces a high-current state that results in a full or partial loss of IC functionality. In some cases, power-cycling an IC eliminates the SEL condition. In other cases the device may be permanently flawed.

- The single-event transient (SET) encompasses the concept of an SEU, but includes more-complex errors induced by a radiation strike. An SET, for instance, might affect a clock and propagate multiple errors throughout memory or logic.

- Total ionizing dose (TID) effects lead to the failure of an IC based on the aggregate exposure to radiation over time. Typically, performance parameters decline in an IC as the TID, measured in rads, increases over time. Radiation creates electron-hole pairs in the oxide layer of an IC—slowly changing the threshold voltage of transistors.

Xilinx and its partners have gone to great lengths to understand the radiation effects and to test and characterize mitigation techniques in FPGAs. Back in 2002, Xilinx and the Jet Propulsion Laboratory founded the Xilinx Radiation Test Consortium (XRTC—originally referred to as the Single-Event Effects Consortium, or SEEC). The consortium currently has 14 members, including universities, research laboratories, and defense and space contractors.

The partners are generally organizations that need to use FPGAs in space applications and have a vested interest in accurately assessing radiation-induced effects and radiation-tolerant and –hardened designs. The consortium website includes a comprehensive library of research papers (http://www.xilinx.com/esplaero\_deflradiation\_effects.htm) that have validated the reliable use of SRAM-based FPGAs in space applications.

Memory—including SRAM—has long been considered among the most susceptible circuits to radiation-induced effects and specifically to SEUs. That fact led some to question the suitability of SRAM-based FPGAs in space applications.

SRAM-based FPGAs, however, offer tremendous flexibility relative to programmable devices based on nonvolatile memory. For starters, SRAM-based FPGAs, and specifically those from Xilinx, have consistently offered the highest level of integration available in programmable ICs. Moreover, SRAM-based FPGAs are easily reconfigured, allowing a system to serve multiple applications and allowing teams to remotely reconfigure a system to fix a flaw in the system implementations that isn't revealed until after deployment. The capacity and performance of the most advanced SRAM-based FPGAs far exceed those of the most advanced programmable nonvolatile devices.

— Maury Wright

Figure 2 – The Virtex-5QV rad-hard FPGA is a crowning achievement in Xilinx's long, rich history of providing leading-edge IC technology for space applications.

the upset mitigation is so effective with virtually no susceptibility to protons that GEO is the worst-case orbit for SEFIs and SEUs, exactly the opposite of what space radiation experts have learned to expect," said Swift.

In addition, Xilinx's Digitally Controlled Impedance (DCI) allows adjustment output impedance and input termination values without external components. Finally, Xilinx ensured its Block RAMs are protected from outputting erroneous data in spite of upsets via an error-detection-and-correction circuit to eradicate upsets.

#### **Virtex-5QV Delivers Results**

The Virtex-5QV delivers results unmatched by previous FPGAs. The ICs are fully characterized for space radiation effects in heavy ion and proton environments. These FPGAs will withstand a TID of 700 krads(Si), based on method 1019 as defined in MIL-STD-833.

Immunity to single-event latchup is defined by a threshold to linear-energy transfer (LET)—the amount of energy transferred to material as an ionizing particle travels through that material. The Virtex-5QV meets the MIL-STD-833 requirement that LET is greater than 100 MeV/mg-cm<sup>2</sup> (mega electronvolts per milligram per centimeter squared). In short, the device is essentially immune to SEL effects.

SEU immunity in the configuration memory and control logic is defined in terms of deployment in a GEO environment relative to a space platform that travels 36,000 km per day. Based on 35 Mbits on an IC that could be subject to an SEU, the IC will suffer  $3.8 \times 10^{-10}$  errors per bit per day.

With the availability of the Virtex-5QV FPGA, space teams will have access to a state-of-the-art reprogrammable platform built on a 65-nm copper process technology. The teams can prototype their work with widely available commercial FPGAs and easily accessible development tools, and then deploy systems that the Xilinx Radiation Test Consortium has proven to be reliable in the harsh radiation environment in space.

The Virtex-5QV device will sample in the current quarter, with general production availability planned for first half of 2011. For more information, visit <a href="http://www.xilinx.com/products/virtex5qv/index.htm">http://www.xilinx.com/products/virtex5qv/index.htm</a>.

Maury Wright is an electronics engineer turned technology journalist and industry consultant, with broad experience in technology areas ranging from microprocessors to digital media, wireless and power management. Wright worked at EDN Magazine for 22 years, serving as editor-in-chief and editorial director for five years. Wright also served as editor of the EE Times Digital Home and Power Management websites.

#### IS YOUR MARKETING MESSAGE REACHING THE RIGHT PEOPLE?

Hit your target by advertising your product or service in the Xilinx *Xcell Journal*, you'll reach thousands of qualified engineers, designers, and engineering managers worldwide.

The Xilinx *Xcell Journal* is an award-winning publication, dedicated specifically to helping programmable logic users – and it works.

We offer affordable advertising rates and a variety of advertisement sizes to meet any budget!

> Call today: (800) 493-5551 or e-mail us at xcelladsales@aol.com

When facing a project with ever-changing requirements and software contributions from multiple locations, multiprocessors can actually help.

It is a commonly held view that it is harder to develop software for multiple-processor systems than single-processor systems. But in fact, this is not always the case. Our design team at TRW Conekt, the consultancy arm of TRW Automotive, recently undertook a project that demonstrates how partitioning the hardware to match the problem at hand allows development of very efficient systems using many processors.

Our team was tasked with providing embedded processing electronics to run in cars for a project known as "Foot-LITE" (led by MIRA Ltd. and sponsored by the U.K. government-backed Technology Strategy Board, the Department for Transport and the Engineering and Physical Sciences Research Council). This project provides feedback to drivers about their driving habits from the perspective of both safety and fuel economy.

The system gives the feedback to the driver in two ways. First, a dashboardmounted smartphone display system (designed by Brunel University and developed by HW Communications Ltd.) provides real-time communication with the driver about events that require immediate attention. In addition, the system collects continuous journey data, including video streams of particular "events," and then uploads them to an Internet-based server for users to view at their leisure. The decision about which events to flag to the user is made by an algorithm developed by partner Ricardo UK, based on driving advice from another partner, the Institute of Advanced Motorists.

The project will fit this system to a small fleet of 30 vehicles (see Figure 1). Test drivers will be members of the public employed by project partner Hampshire County Council.

The project has progressively incorporated the research results obtained by the collaboration of 12 industrial, governmental and academic partners. This means that we've needed a very flexible solution to our processing challenges.

## At the beginning, we envisioned providing a single-processor system. However, it was soon apparent that a dedicated processor would ease the task of integration for each iteration of algorithmic development.

#### **Base System**

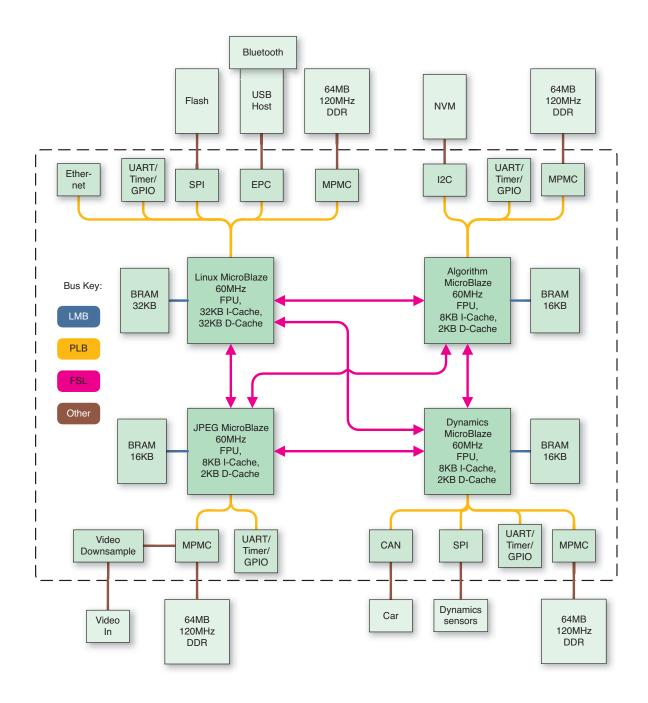

We had available to us a processing system, already under development in another project, to perform image-processing tasks (Figure 2).

This system is based around a single Xilinx® Spartan®-3A XC3SD3400A device connected to four independent blocks of DDR memory, an architecture that allows users to implement many different

additional processors by making use of embedded BRAM blocks.

In addition, I/O to the outside world is configurable using small daughterboards, which allows for quick turnaround of customized I/O sets for different projects.

The project partners decided very early on that a USB interface would be desirable, as it allows you to add a wide variety of peripherals to the system. This necessitated

Engine

Back

Office DB

Home PC

Camera & Image

Processing

On Car

Figure 1 - Foot-LITE system

processor/logic configurations. For example, you could use the whole FPGA fabric as pure logic resources crafted entirely in HDL. Alternatively, you could use higher-level tools such as the Xilinx EDK to implement four (or more) soft-core microcontrollers. Each of the four would have access to its own private DDR memory device, protecting data from interference by the other microcontrollers. For other simple tasks, you could include

some form of USB stack—we obtained one using the Petalinux implementation of ucLinux—and a daughterboard with a USB host device.

The use of Linux also gives us a simple way to manage the SPI flash devices that the system provides for FPGA bitstream and application code storage. We installed a simple JFFS2 file system to allow in-field application updates, either over Ethernet (using FTP) or by booting

with a USB Memory Stick that contains a script to upload new code to the internal flash. In a traditional embedded system, all this would require the software team to write low-level application code. However, with Linux available to us, we can easily write simple Bash scripts to control these processes.

#### **Foot-LITE Algorithms**

Ricardo developed the core algorithms that assess the driver's actions and implemented them on its rCube rapid prototyping system (http://www.ricardo.com/en-gb/ Engineering-Consulting/Automotive-Expertise/Controls--Electronics/ Embedded-Software/rCube/). We used this approach for initial simulator trials and three test vehicles. In the test vehicles, an embedded vision system (based around an existing TRW product—coincidentally also containing an FPGA) measured distance to the vehicle in front and assessed the vehicle's position within the lane. A radar system provided an alternative source of range information in the test vehicles. As a step toward a production implementation, we eliminated the radar system for the larger-scale trials, as the vision system provided sufficient information for the application

We fitted the vehicle with a forward-facing video camera and processing subsystem, which are combined into a small unit that fits near the rear-view mirror. Embedded algorithms in this subsystem process the video images to measure the distance between the car and the edge of the lane. In addition, a parallel algorithm detects vehicles in front of the Foot-LITE vehicle and provides a measure of the headway distance. This subsystem transmits its data to the Foot-LITE system unit using the automotive-standard controller-area network (CAN) bus.

We integrated a three-axis accelerometer and yaw-rate sensing package into the Foot-LITE unit, potentially providing the Foot-LITE algorithms with access to high-rate, low-latency vehicle dynamics information when required.

The Foot-LITE algorithms fuse all this data to provide a set of simple outputs to the driver relating to his or her driving style.

#### Algorithm Implementation

At the beginning, we envisioned providing a single-processor system. However, it was soon apparent that a dedicated processor would ease the task of integration for each iteration of algorithmic development. We isolated the main host processor and the Foot-LITE algorithm processor by impleto the host application will not affect their application's performance.

We developed a collection of wrapper functions that allow us to "drop in" the code-generated C from the Simulink® compiler without having to make major changes to the interface. We provide a small amount of nonvolatile memory onboard via an I2C bus, which is required for storing various tune parameters within the Foot-LITE algorithms. This necessitated a simple wrapper to provide the algorithms with easy access from the Simulink environment to read this memory at startup and write it back at shutdown.

The system needed to measure accelerations and yaw rate, as well as communicating over the CAN bus with the lane- and

Figure 2 – Processing module is Spartan-based.

menting communications using the MicroBlaze<sup>TM</sup> Fast Simplex Link (FSL) bus system. This allows a complete isolation of the processors' memories (unlike the popular shared-memory methodologies), which greatly eases the integration task, since bugs cannot "migrate" from one processor to another via memory corruptions.

In addition, there is no competition for processor cycles, which means our partners can be confident that any changes we make vehicle-detection system. As we already had low-level CAN drivers and were concerned as to the timeliness of a Linux application measuring the vehicle dynamics information at 40-millisecond rates, we decided to insert a third MicroBlaze into the system. This saved porting CAN drivers to Linux, and allowed deterministic performance via another isolated processing node—critical to the algorithms—which made use of the dynamics measures. In addition, this

approach allowed us to split the task of writing the software to allow parallel development. Once again, we used FSL as the interface between the dynamics processor and the Foot-LITE algorithm processor.

#### **Video Capture and Compression**

The initial conception of the system provided simple measures of lane width and offset, distance to the vehicle in front and so on from the vision system, transmitted over CAN to the Foot-LITE algorithm unit. The project partners decided to enhance this setup by capturing video frames for transmission to the server, to provide off-line contextual assistance for interpreting the advice the system gave. Given that the requirement was only for "Internet-quality" video (300 x 200 pixels at 5 Hz), we felt we could easily assign a fourth MicroBlaze to the task of compressing the video stream to a simple set of JPEG images in real time. The image coming from the camera was a wide-VGA (720 x 480 at 30 Hz) video stream. Clearly, downsampling the image was a task to be performed in hardware.

We designed a simple peripheral to handle the downsampling operation by simply dropping alternate pixels and lines to produce a 360 x 240 image. This peripheral also drops four in five frames to produce the required frame rate. Nothing more complex is needed to produce visibly acceptable results, since the JPEG process renders aliasing artifacts invisible. We used System Generator to develop this peripheral, as it makes export to EDK very straightforward, and we already have experience of using System Generator for more-complex image-processing tasks.

The downsampling peripheral bus masters the data into the SDRAM connected to the JPEG processor, which then compresses each frame, as it arrives, into a circular buffer until the Foot-LITE algorithm sends a flag. The JPEG processor sends the compressed video frames (again over FSL) to the host MicroBlaze. We used a code library from the Independent JPEG Group and found that it needed very little optimization to operate at 5 Hz. Again, having an isolated processor

enabled another software engineer (based at a different site) to work on this aspect of the system in parallel.

#### **Bluetooth to Smartphone and OBD**

Ease of installation was a critical factor for the project. Minimizing the number of wires that the system requires was also an important consideration. We chose Bluetooth as the interface to the smartphone. Drivers for standard USB Bluetooth dongles are standard in the ucLinux kernel, although we had to build the user-space tools ourselves. These have a

number of dependencies on other items of code, which are also cross-compiled with the Petalinux tool set and added to the ucLinux file system.

Once we had decided on Bluetooth for the smartphone interface, it was a natural choice to use Bluetooth for the interface to

Figure 3 – FPGA block diagram showing major external elements

the On-Board Diagnostic System. We made use of a standard off-the-shelf Bluetooth-OBD interface module, removing another wired link from the system.

#### **Easier Debugging**

Debugging a system with multiple, parallel threads of execution is always challenging. But splitting the system across multiple processors actually makes things easier. There is no requirement for a multithreadaware debugger (as might be needed when trying to debug multiple processors within the Linux environment). The Xilinx debugger (XMD) can connect to multiple processors, and by using TCL (the Tool Command Language, which XMD understands), we can automate the setup and download of the code under test to multiple processors. Of course, the common embedded-system debug approach using printf statements was also available, since each processor has its own serial port.

Another tool of great value when debugging the interprocessor communications was ChipScope<sup>TM</sup> Pro. This embedded logic analyzer built into the FPGA fabric allowed us to capture the data passing over the FSL links and narrow down subtle bugs to either the sender or the receiver, and from there to the offending line of code.

The isolation provided by using four processors means that once a particular element is debugged it will (to a large extent) not need to be looked at again. There are none of the weird interactions that always cause problems when integrating disparate code into a large, monolithic application, or when running multiple processes on a single processor.

#### **FPGA Implementation**

In this project, there is almost no HDL—simply a top-level wrapper integrating the EDK-based design with a tiny piece of watchdog code to guarantee the system shuts down after the driver has turned the ignition off. EDK generates the vast majority of the FPGA (the MHS file is more than 1,300 lines long!), with System Generator producing the video downsampler. We configured all four microcontrollers with caches and floating-point

units. With four processors, four DDR memory interfaces and a collection of peripherals (including Ethernet, SPI, IIC, CAN, UARTs, timers, GPIOs), around 70 percent of the device's lookup tables are occupied (around 28,000 LUTs). As is usual with microcontroller-based FPGAs, the block memories are very highly utilized at better than 90 percent, or 119 BRAMs, but the DSP blocks are relatively lightly used: Only the floating-point units in each processor (eight in each, for a total of 32) need them.

#### **Bringing it All Together**

The host microprocessor boots the Linux kernel from internal flash and then mounts its local file systems. The slave processors each have an FSL-based boot loader, which accepts a standard S-record, parses it, copies it into local memory and executes it. The Linux processor simply streams the Srecord from the file system direct to the FSL pseudo-file (using the built-in dd utility). As described already, all interprocessor communication takes place over a fully connected mesh of FSL links. These are all 32 bits wide and operate at 60 MHz, providing plenty of low-latency communication bandwidth. Although avoiding shared memory may seem limiting, the upside is that this system provides the isolation benefits already discussed. The hardware architecture matches the application requirement subdivision well, which creates an intuitive software partition.

The Foot-LITE algorithm microprocessor sends triggers to the JPEG compressor when required and communicates with the smartphone display. The Linux processor intermediates between the Bluetooth communications and the rest of the system (Figure 3). In addition to the immediate signals to the driver, it sends a continuous stream of information about the state of the vehicle and occasional streams of video for onward transmission to a central server via the smartphone.

At the end of a journey, when the driver switches off the ignition, the main processor informs the slave processors, which can then perform their own shutdown procedures (such as writing updated parameters to the nonvolatile tune storage) before informing the main processor that they are in a safe state for shutdown. At this point, the host processor signals to the power supply and the system enters a very low-power sleep mode, awaiting the next turn of the ignition. In the unlikely case that the software does not send the shutdown signal within a couple of minutes of the ignition turnoff, a hardware timer in the FPGA fabric pulls the power, to avoid flattening the vehicle battery.

In the final stages of the project, two academic members of the consortium (Newcastle University and the University of Southampton) will analyze the data streamed out of the vehicle in actual highway use to evaluate the effectiveness of the system in altering driver behavior.

#### The FPGA Advantage

FPGAs provide huge flexibility, which meets the needs of evolving projects much more easily than a fixed hardware platform. The ability to mix in custom hardware for intensive applications (for example, video) is also beneficial. If you use Linux to gain the huge benefits of ready-made high-level access to peripherals such as Ethernet, you don't need to compromise on real-time performance, as you can push those critical tasks into their own microprocessor. Finally, if a large, geographically distributed team is developing the software, having a hardware architecture that matches the functional split provides benefits in development and integration.

For more information, contact the author at *martin.j.thompson@trw.com*. You can read more about the Foot-LITE project at *http://www.foot-lite.net*. MIRA Ltd. is the project lead. The other industrial project partners are Auto-txt Ltd., Hampshire County Council, HW Communications Ltd., The Institute of Advanced Motorists Ltd., Ricardo UK Ltd., Transport for London, TRW Conekt and Zettlex Printed Technologies Ltd. The academic partners are Brunel University, Newcastle University Transport Operations Research Group and University of Southampton Transportation Research Group.

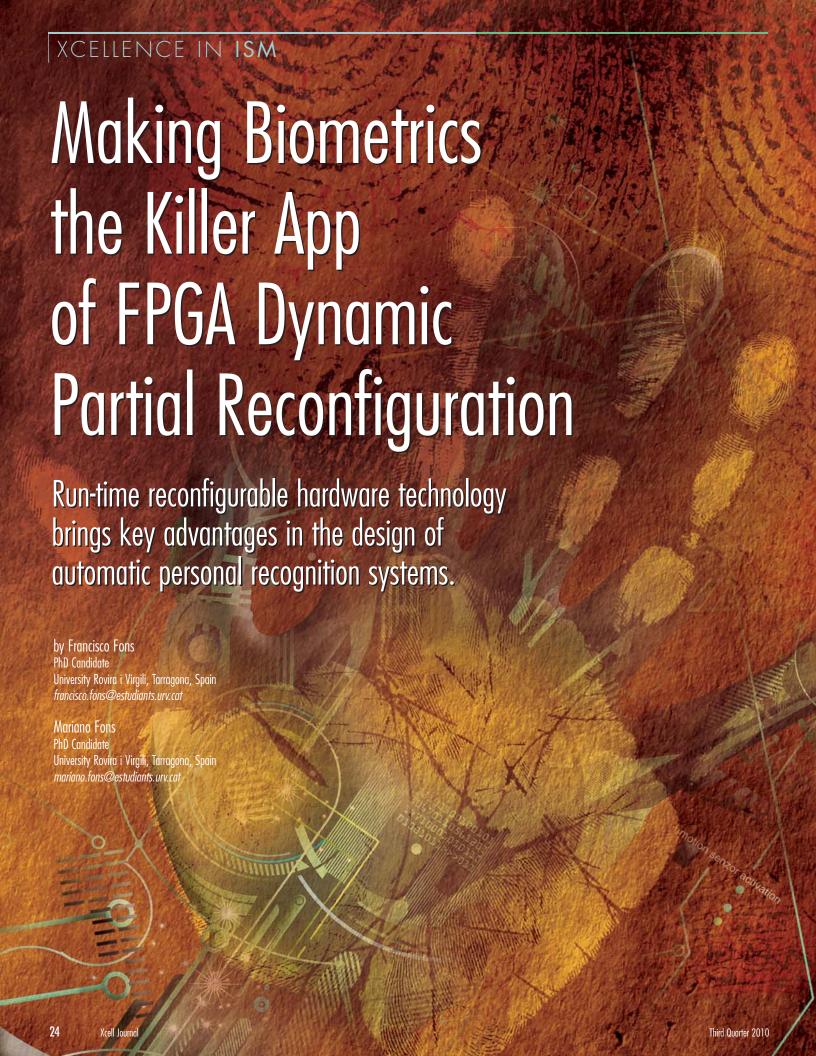

In the current era of communications and information technologies, automatic biometric personal recognition systems represent the state of the art in high-performance signal- and image-processing applications. In fact, it is not difficult to find in our daily lives systems requesting our personal authentication/identification before allowing us to use them; electronic tellers, computers, mobile phones and even cars require such authorization. Many end-user applications that demand better levels of security than PINs, passwords or ID cards use personal recognition algorithms based on biometric (physiological or behavioral) characteristics, usually delivering them as a kernel.

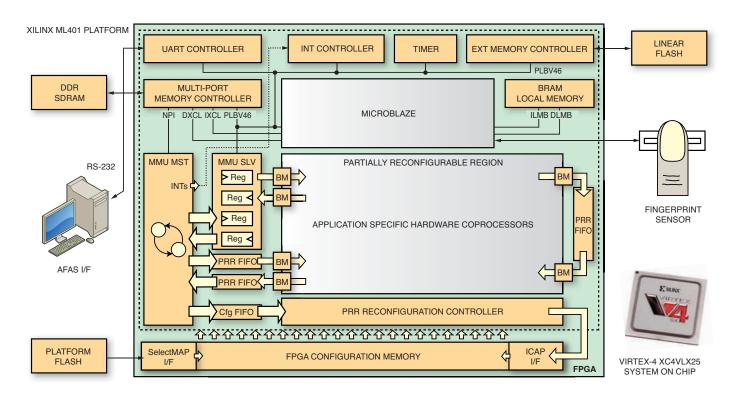

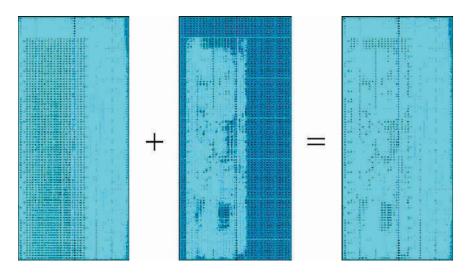

As a proof of concept, we developed an automatic fingerprint authentication system (AFAS) on the second smallest Xilinx® FPGA device in the Virtex®-4 LX family, making use of the Xilinx Early Access Partial Reconfiguration design flow and tools. The experimental results demonstrate it is possible to embed a full, highly demanding biometric recognition algorithm in such a small FPGA at an extremely low cost, processing it in real-time while preserving data accuracy and precision in its physical implementation by multiplexing functionality on the fly over a reduced set of resources placed in a partially reconfigurable region (PRR) of the device. These promising results, together with the proven maturity of the technology we used, encourage us to move this solution from research to industry, in an attempt to make partial reconfiguration (PR) available to the consumer world in the way of secure commercial products.

#### **Basics of Biometrics**

Computationally complex applications processed in real time, driven at low rates of power consumption and synthesized at low cost are unavoidable requirements today in the design and development of embedded systems, particularly when addressed to mass-production niches. In this context, dynamic partial self-reconfiguration of single-context FPGAs arises as a firm technological alternative, able to deliver a high functional density of resources to efficiently balance all those demands for time-, power- and cost-sensitive applications.

Software-defined radio, aerospace missions and cryptography are some of the known applications that exploit the benefits of dynamic partial reconfiguration of programmable logic devices today. In this context, our group is applying PR to an application space that hasn't traditionally leveraged it: biometrics. As security has become a major issue in today's digital information environment, especially for application fields like e-commerce, e-health, e-passports, e-banking or e-voting, among others, we believe the use of PR in biometrics holds great promise.

However, biometrics is complex. It requires stringent and computationally intensive image/signal processing in real time, along with a great deal of flexibility.

Finally, cost-effectiveness is probably the most important reason for biometrics to make use of partial reconfigurability. In aggressive markets like consumer electronics or automotive, vendors must market their systems at a competitive cost. Customers demand products with the highest level of security at the lowest possible price point.

The way to improve security and reliability is by increasing the computational power of the biometric recognition algorithm. This increment of computation usually involves a like increment in execution time and also in cost (resources). However, the cost is hardly affected in those scenarios where the design is based on dynamic-partial-reconfiguration technology. Using PR, designers can partition that new computation and schedule it as

Given that progress in biometrics technology is expected to continue in the future, biometric products already in the market will have to admit upgrades in the field just to avoid getting obsolete, and for this they require open system architectures.

In addition, personal recognition algorithms are in continuous evolution. As the research community expends major effort in this field, error rates like false acceptance and false rejection are improving. As a consequence, consumers are growing more confident about biometric systems, and acceptance is increasing. Given that progress in biometrics technology is expected to continue in the future, biometric products already in the market will have to admit upgrades in the field just to avoid getting obsolete, and for this they require open system architectures. In this regard, the flexible hardware found in run-time reconfigurable FPGA devices enables the versatility and scalability needed.

new processing stages added to the current sequential execution flow of the application. Thus, cost often can be held invariant to functional changes of the algorithm.

Designers can partition the biometric recognition algorithm into a series of mutually exclusive stages that are processed sequentially, where the outputs or results of one stage become the input data for the next. This sequential order means designers can multiplex hardware resources in time and customize them to execute a different task or role at each moment, increasing their functional density and thus keeping constant the total number of resources needed to process the entire algorithm. Moreover, the reconfiguration overhead is short enough

so as not to eclipse the benefits gained by hardware acceleration.

Furthermore, reconfiguring one set of resources on the fly will not interrupt the rest of the resources available in the FPGA. In this way, the resources that are not reconfigured continue to operate and guarantee the link with the exterior world for the entire life cycle of the application.

Our challenge in this work consisted in demonstrating that PR fits well in the development of complex personal recognition algorithms based on biometric characteristics, making use of a two-dimensional design abstraction level through which the functionality is managed not only in space but also in time. We describe this target step by step in the next sections.

#### Automatic Fingerprint Authentication System

Fingerprint verification is one of the most popular and reliable biometric techniques used in automatic personal recognition. Essentially, the technique splits the AFAS application into two processes or stages carried out at different times and in different conditions: enrollment and recognition.

Enrollment is the system configuration process through which the user gets registered. Generally, the user exposes his or her fingerprint to the system, which submits it to a set of computationally intensive imageprocessing phases aimed at extract-

ing all relevant, permanent and distinctive information that will permit the system to unequivocally recognize the fingerprint's genuine owner. This set of characteristics becomes the user ID, which the system stores in its database. This process is normally conducted off-line, in a secure environment and under the guidance of expert staff.

Once the user is registered, the next time his or her fingerprint is exposed to the system in the recognition stage, the system will check to see if it corresponds with any

ACQUISITION SEGMENTATION NORMALIZATION **ENHANCEMENT** FIELD ORIENTATION FILTERED ORIENTATION BINARIZATION **SMOOTHING** THINNING **FEATURES EXTRACTION** ALIGNMENT MATCHING

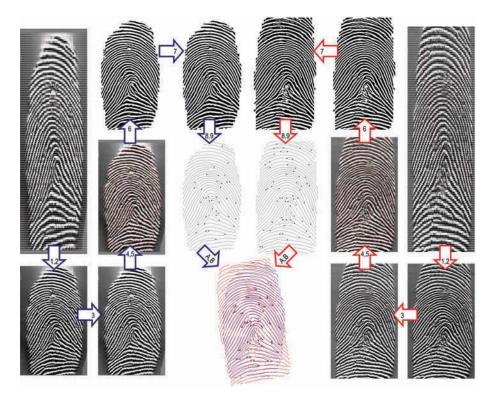

Figure 1 – Spatial partitioning and floorplanning of the AFAS take place in one static region and one reconfigurable region of the Virtex-4. Temporal partitioning of the application in sequential stages occurs in the reconfigurable region.

authorized member within the database. All the processing tasks performed in the enrollment are repeated now to again extract those distinctive characteristics from the live fingerprint sample. The system then compares these characteristics with the information stored as user templates in the database to conclude whether the live scan matches any of the registered templates. Recognition comes in two modalities depending on the size of the database: authentication, when a one-to-one (or one-to-few) matching is

processed; and identification, when the matching is one-to-many due to the fact that many users are registered in the system. Recognition is normally performed online in a less-secure environment and under real-time constraints.

Each of these stages is, in its turn, partitioned into a series of mutually exclusive tasks designed to extract from the fingerprint image such information as will distinguish one user from the others. With that object in view, the system carries out specific computations, such as image processing (2D convolution, morphologic operations), trigonometrics (sin, cos, atan, sqrt) [1] or statistics (average value, variance).

Thus, the biometric application is organized in a set of tasks that are processed following a sequential flow. A task cannot start unless the previous task has finished, since the output data of a given task is the input data for the next one in the chain. Moreover, most of these tasks are repeated in both enrollment and recognition stages.

Figure 1 enumerates the tasks that take place in the presented algorithm. The first task is the image acquisition. Depending on the size of the sensor, a system may acquire the whole image at one touch (complete image sensor) or in slices (sweeping sensor). In the second scenario—which was the case we used—an additional image reconstruction phase is necessary. The full finger-print image gets composed by the set of consecutive and partially overlapped slices acquired [2].

Once we have the whole reconstructed image, the next task consists of segmenting it in the foreground (that is, the region of interest, based on the ridges and valleys of the fingertip skin) from the background. We perform this process by convolving the image, pixel by pixel, with directional filters made up of Sobel masks of kernel 5x5. Afterwards, we normalize the image at a specific mean and variance.

Next, we enhance this normalized image through an isotropic filtering, which retrieves relevant image information from some potential regions of the captured

image initially lost or disturbed by the noise in the acquisition phase, making use of a kernel 13x13 [3]. Once this step has improved the quality of the image, the next task is to compute the field orientation map, which determines the dominant direction of ridges and valleys in each local region of the image foreground. The resultant field orientation is then submitted to a new filtering stage (kernel 5x5) to obtain a refined field orientation map.

Until this point, the image has been worked at 8-bit gray scale. Now, in the binarization process, Gabor directional filters of kernel 7x7 convolve the gray-scale image to improve the definition of the ridges and valleys and convert each of the gray-scale pixels to a 1-bit binary (black or white) dot. The image is then submitted to a new loop to smooth and redraw the shapes of the resultant ridges and valleys. Later, the thinning or skeletonization task converts the black-and-white image to one with black ridges one pixel wide. From that image it is not difficult to extract the fingerprint characteris-

tic points or minutiae, that is, the ridge endings and bifurcations.

Finally, with the minutiae and the field orientation data already obtained, the fingerprint template and sample can be aligned. The first way of accomplishing this is through a brute-force algorithm that moves one image over the other-taking into consideration both translation and rotation movements as well as some admissible tolerances due to the image distortion coming from the skin elasticity in the acquisition phase—to find the best alignment between them [4]. The next step is to match the sample and template to obtain a level of similarity between them, which the automatic system will use to decide if both images correspond to the same person [5].

All this processing, illustrated in Figure 4, is performed on fingerprint images of 500-dpi resolution, 8-bit gray scale and up to 280 x 512 pixels, acquired through sweeping technology via the thermal fingerprint sensor FingerChip from Atmel Corp. and computed in the Xilinx Virtex-4 XC4VLX25 FPGA device.

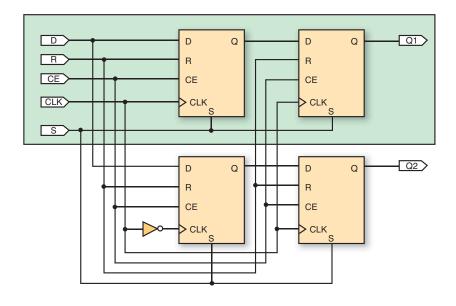

#### **System Architecture**