INDUSTRY'S FIRST TRIPLE MODULAR REDUNDANCY DEVELOPMENT TOOL FOR RE-CONFIGURABLE FPGAS

# XILINX TMRTOOL

# ∑ Challenge for Designing Circuits with Triple Modular Redundancy (TMR)

Mastering and implementing TMR into a design greatly increases the complexity and the time it takes to build and debug a system

### **∑** The Xilinx TMRTool Solution

- Works seamlessly with any HDL and Synthesis tool to automatically build triple modular redundancy into a Xilinx FPGAbased design

- Accelerates design cycle by allowing designers to devote more time to system design and debugging, and less time to the complex details of TMR

- Updated version with enhanced interface and algorithms

The Xilinx TMR methodology, along with scrubbing, provides effective single-event upset (SEU) and single-event transient (SET) immunity for Virtex®-5QV and Virtex-4QV space-grade designs. In addition, the TMRTool:

- Supports Windows 2000/XP/7 with ISE™, all design entry methods, HDL, and synthesis tools

- Provides optional SRL16 extraction and optional half-latch extraction capability

- Increases productivity by reducing errors, speeding TMR implementation, and enabling easy integration of custom-built TMR modules while giving designers complete control over how their design is triplicated

### Xilinx Triple Modular Redundancy Technology

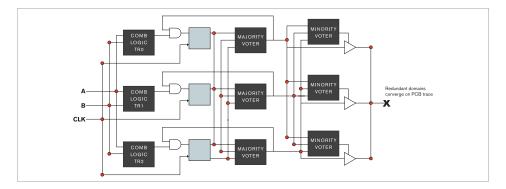

Traditional TMR does not protect against SEUs in voting logic or against SETs, and does not lend itself well to the re-configurability of Xilinx FPGAs. Unlike traditional TMR, the Xilinx TMR approach involves:

- Triplicating all inputs including clocks and throughput (combinational) logic

- Triplicating feedback logic and inserting majority voters on feedback paths

- Triplicating all outputs, using minority voters to detect and disable incorrect output paths

### AUTOMATIC IMPLEMENTATION OF TRIPLE REDUNDANCY FOR SEU MITIGATION

### Xilinx TMR State Machines

Finite State Machines pose a special problem for TMR in re-programmable devices. To operate continuously in the presence of SEUs, each redundant state machine domain must remain synchronized with the others. For traditional TMR, this means that state machines have to be reset to fully recover from a SEU. Xilinx TMR solves this problem by inserting voters on all feedback paths, so that redundant state machines are continually synchronized with each other—eliminating the need for resets to recover from SEUs.

## Protection from SEUs in Voting Circuits

The major difference between traditional TMR approaches and the Xilinx TMR approach: voters themselves are triplicated, as well as redundant domains coverage on the printed circuit board. If an upset occurs in throughput logic or in a state machine somewhere in the design, one of the redundant design domains will behave

TMRTool automatically implements Xilinx TMR methodology for state machines.

differently from the others. The output voter for that domain will detect that its domain is behaving differently and disable the three-state buffer for that domain, placing its pin in a high impedance state. The other two domains will continue to operate correctly, driving the correct output off the chip. If a voter is upset, the worst it can do is disable the output of a domain that is behaving correctly. As with the first scenario, the other domains will continue to operate correctly, driving the correct output off the chip.

### Take the NEXT STEP

For more information on the TMRTool\* or other Xilinx solutions for aerospace and defense markets, visit www.xilinx.com/esp/aerospace.htm

\*The Xilinx TMRTool is an ITAR-controlled product and as such certain documents and declarations must be collected from the customer when an order is placed. For more information, please contact your local Xilinx sales representative.

### **Corporate Headquarters**

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124 USA Tel: 408-559-7778

Tel: 408-559-7778 www.xilinx.com

### **Europe**

Xilinx Europe

One Logic Drive

Citywest Business Campus

Saggart, County Dublin

Ireland

Tel: +353-1-464-0311

www.xilinx.com

#### Japan

Xilinx K.K.

Art Village Osaki Central Tower 4F

1-2-2 Osaki, Shinagawa-ku

Tokyo 141-0032 Japan

Tel: +81-3-6744-7777

japan.xilinx.com

### Asia Pacific Pte. Ltd.

Xilinx, Asia Pacific 5 Changi Business Park Singapore 486040 Tel: +65-6407-3000 www.xilinx.com

© Copyright 2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.