# Vivado Design Suite User Guide

# **Programming and Debugging**

UG908 (v2022.2) October 19, 2022

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing non-inclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this <a href="link">link</a> for more information.

# **Table of Contents**

| Chapter 1: Introduction                                           | 8  |

|-------------------------------------------------------------------|----|

| Navigating Content by Design Process                              | 8  |

| Getting Started                                                   | 9  |

| Debug Terminology                                                 | 10 |

| Chapter 2: Vivado Lab Edition                                     | 14 |

| Installation                                                      | 14 |

| Using the Vivado Lab Edition                                      | 15 |

| Vivado Lab Edition Project                                        | 17 |

| Programming Features                                              | 22 |

| Debug Features                                                    | 22 |

| Chapter 3: Generating the Bitstream or Device Image               | 23 |

| Changing the Bitstream File Format Settings                       |    |

| Changing the Device Image (.pdi) File Format Settings             | 26 |

| Changing Device Configuration Bitstream Settings                  | 27 |

| Chapter 4: Programming the Device                                 | 29 |

| Opening the Hardware Manager                                      | 29 |

| Opening Hardware Target Connections                               | 29 |

| Connecting to a Hardware Target Using hw_server                   | 30 |

| Opening a New Hardware Target                                     | 31 |

| Troubleshooting a Hardware Target                                 | 33 |

| Associating a Programming File with the Hardware Device           | 35 |

| Programming the Hardware Device                                   | 35 |

| Closing the Hardware Target                                       | 39 |

| Closing a Connection to the Hardware Server                       | 39 |

| Reconnecting to a Target Device with a Lower JTAG Clock Frequency | 39 |

| Connecting to a Server with More Than 32 Devices in a JTAG Chain  | 41 |

| Changing the Default SmartLynq Ports                              | 42 |

| Chapter 5: Remote Debugging in Vivado                             | 43 |

| . 35 3                                                            |    |

| Using Vivado Hardware Server to Debug Over Ethernet                           | 43  |

|-------------------------------------------------------------------------------|-----|

| Xilinx Virtual Cable (XVC)                                                    | 44  |

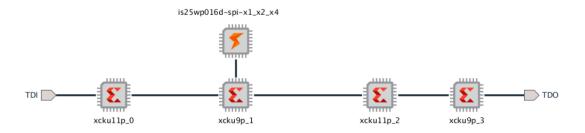

| Chapter 6: Programming Configuration Memory Devices                           | 56  |

| Changing Device Image Properties                                              | 57  |

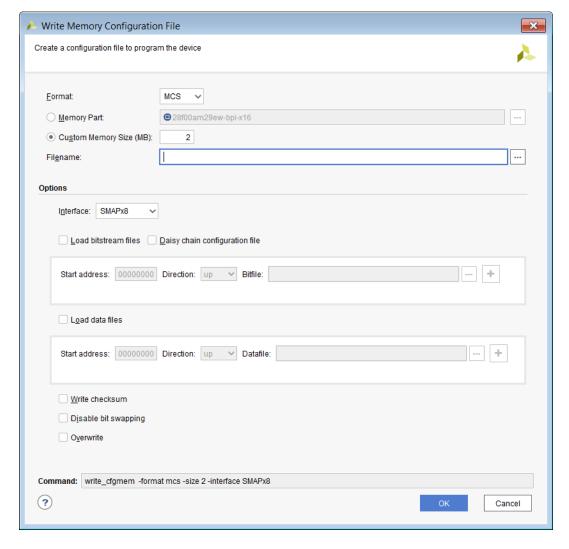

| Creating a Configuration Memory File (for FPGA Devices)                       | 58  |

| Creating a Configuration Memory File for SPI Dual Quad (x8) Devices (for FPGA |     |

| Devices)                                                                      |     |

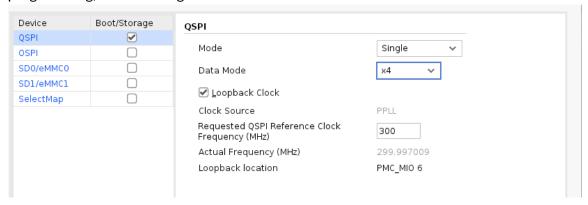

| Creating an Initialization PDI (for Versal Devices)                           | 61  |

| Connect to the Hardware Target in Vivado                                      | 62  |

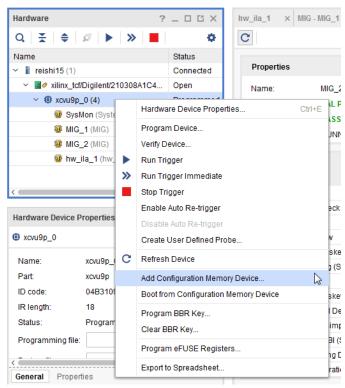

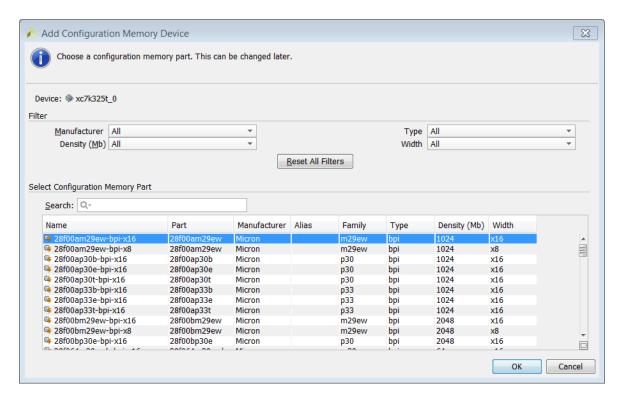

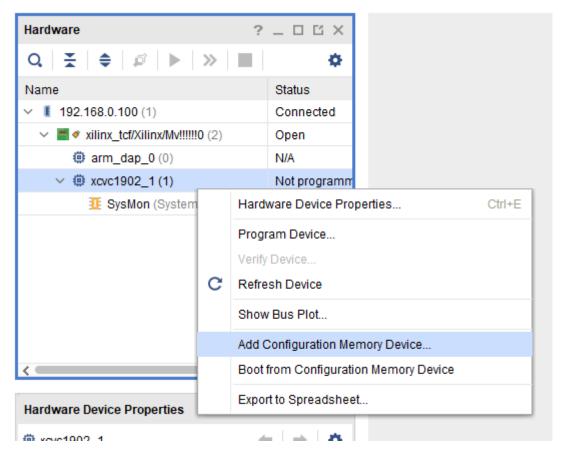

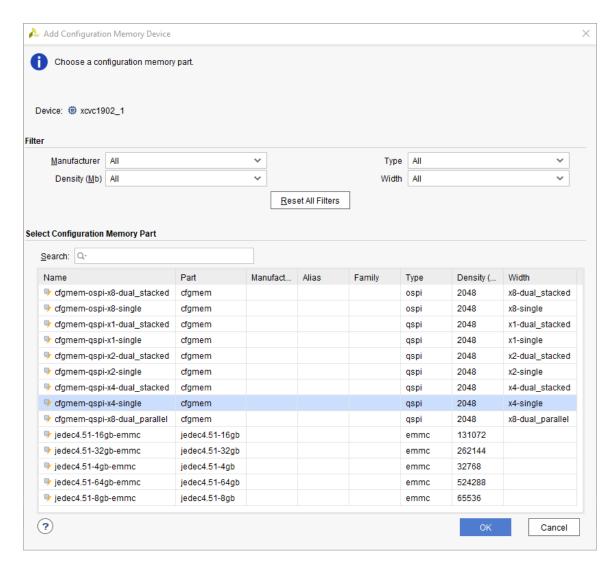

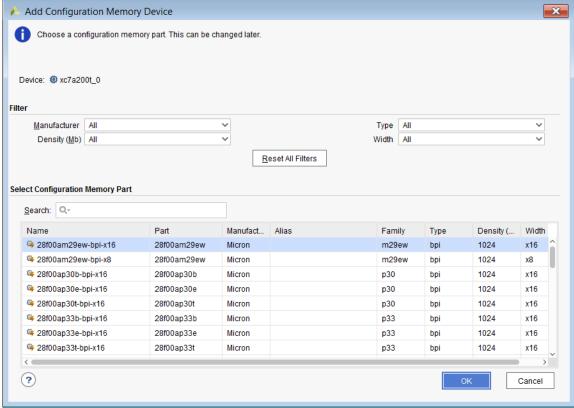

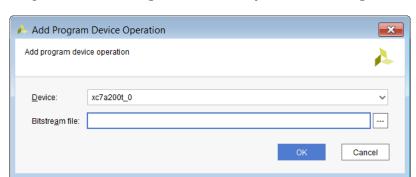

| Adding a Configuration Memory Device                                          | 63  |

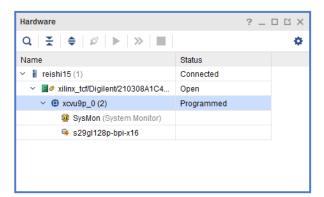

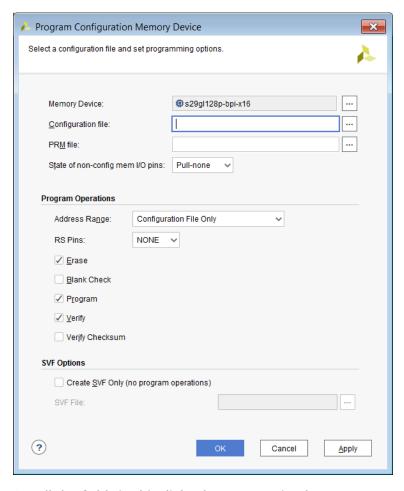

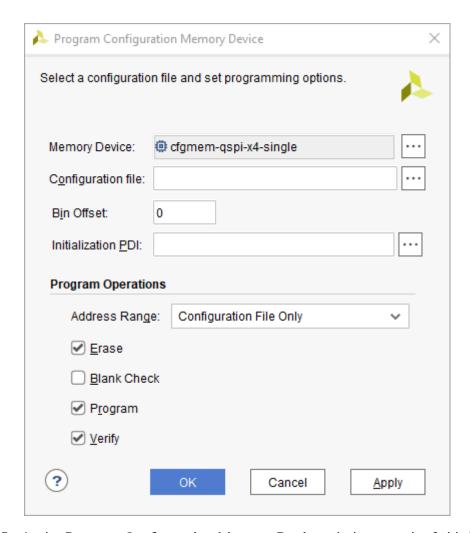

| Programming a Configuration Memory Device                                     | 64  |

| Programming a Configuration Memory Device (Versal Devices)                    | 67  |

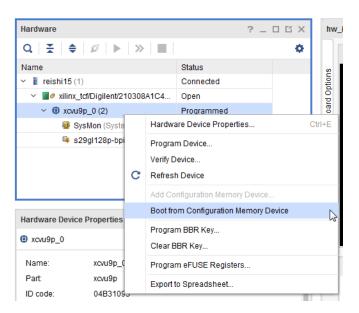

| Booting the FPGA Device                                                       | 71  |

| Configuration Failures in Master Mode                                         | 72  |

| Chapter 7: Advanced Programming Features                                      | 73  |

| Readback and Verify                                                           |     |

| Generating Encrypted and Authenticated Files for 7 Series Devices             |     |

| Generating Encrypted and Authenticated Files for UltraScale and UltraScale+   |     |

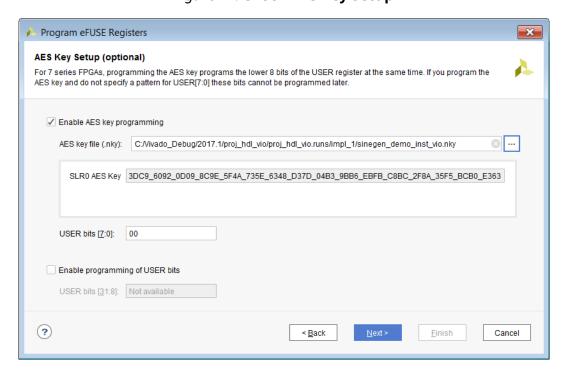

| Programming the AES Key for 7 Series Devices                                  |     |

| Programming the AES Key for UltraScale and UltraScale+ Devices                |     |

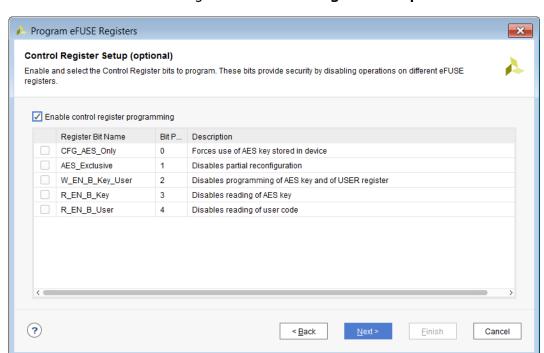

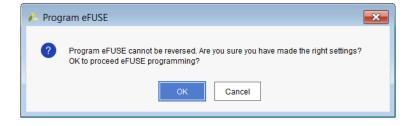

| eFUSE Register Access and Programming                                         |     |

| Cable Support for eFUSE Programming                                           |     |

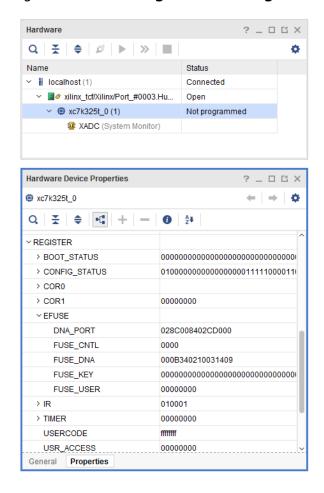

| eFUSE Register Access and Programming for 7 Series Devices                    |     |

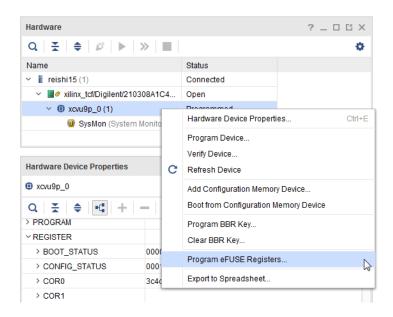

| eFUSE Register Access and Programming for UltraScale and UltraScale+ Devices  |     |

| eFUSE NKZ File                                                                |     |

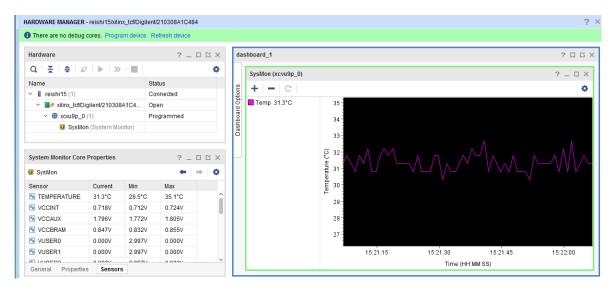

| System Monitor                                                                | 105 |

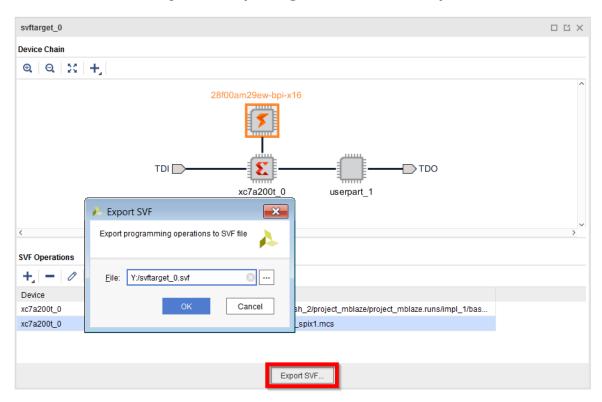

| Chapter 8: Serial Vector Format (SVF) File Programming                        | 100 |

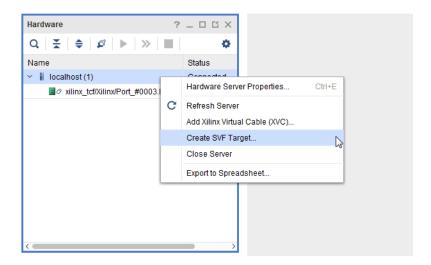

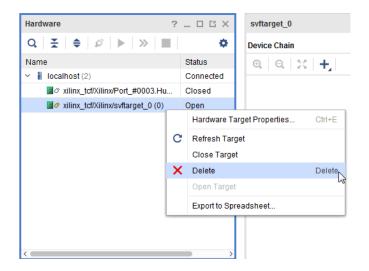

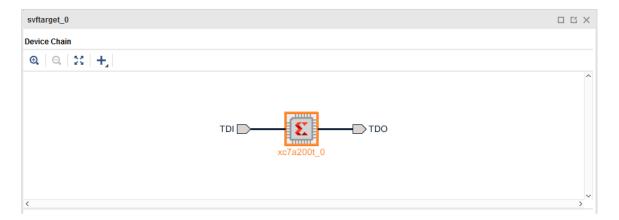

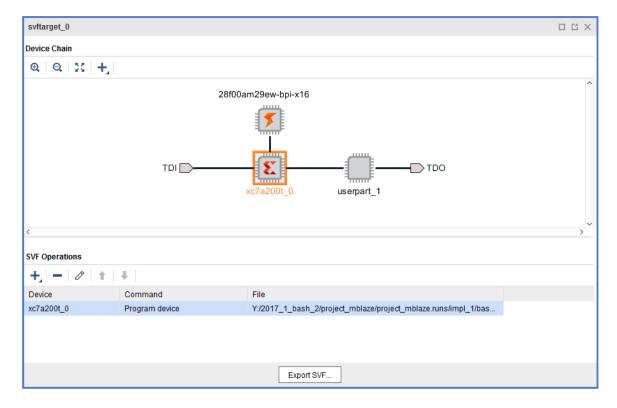

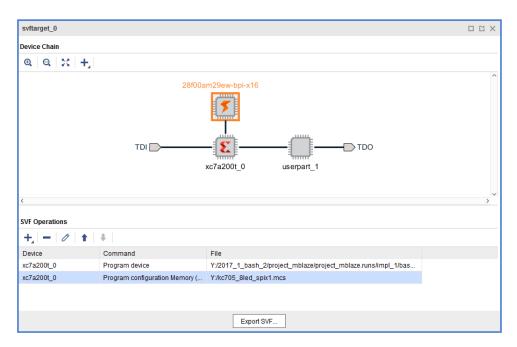

| Creating an SVF Target                                                        |     |

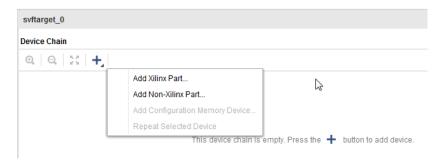

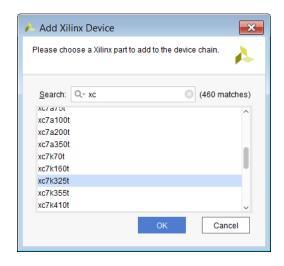

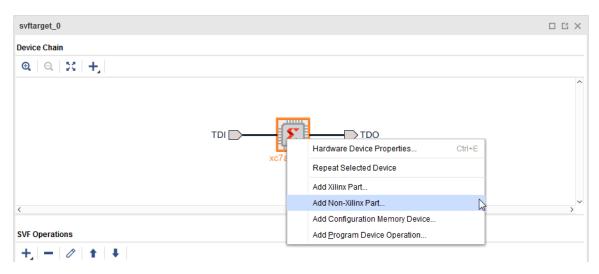

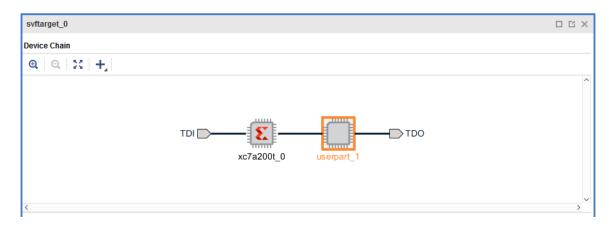

| Adding Devices to an SVF Target                                               |     |

| Adding Configuration Memory Parts to Xilinx Devices                           |     |

| Operations on the SVF Chain                                                   |     |

| Writing SVF Files                                                             |     |

| Executing SVF Files                                                           |     |

|                                                                               |     |

| Chapter 9: Debugging the Design                                               |     |

| RTI -I evel Design Simulation                                                 | 125 |

| Post-Implemented Design Simulation                                     | 125 |

|------------------------------------------------------------------------|-----|

| In-System Logic Design Debugging                                       | 126 |

| In-System Serial I/O Design Debugging                                  | 126 |

| Chapter 10: In-System Logic Design Debugging Flows                     | 127 |

| Probing the Design for In-System Debugging                             |     |

| Versal In-System Debugging                                             |     |

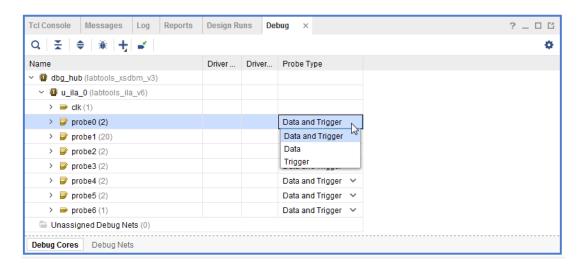

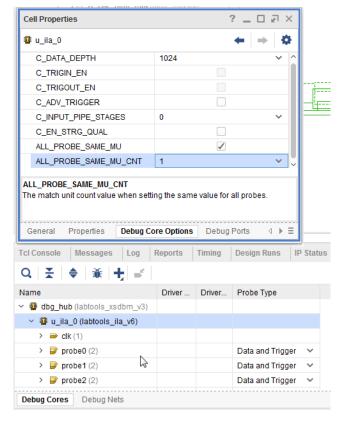

| Using the Netlist Insertion Debug Probing Flow                         |     |

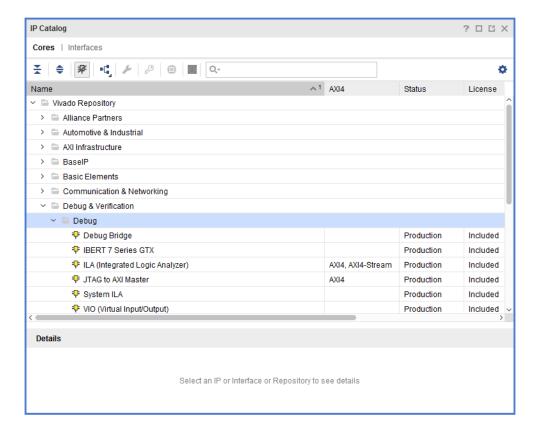

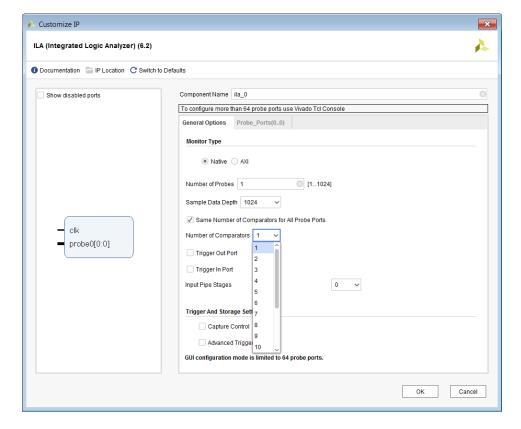

| HDL Instantiation Debug Probing Flow Overview                          |     |

| Using the HDL Instantiation Debug Probing Flow Flow                    |     |

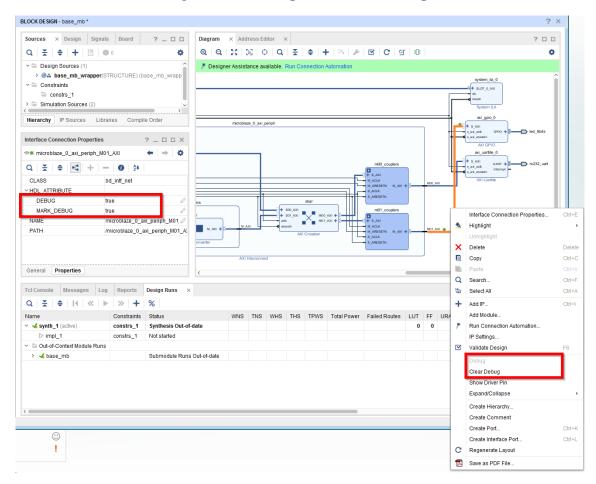

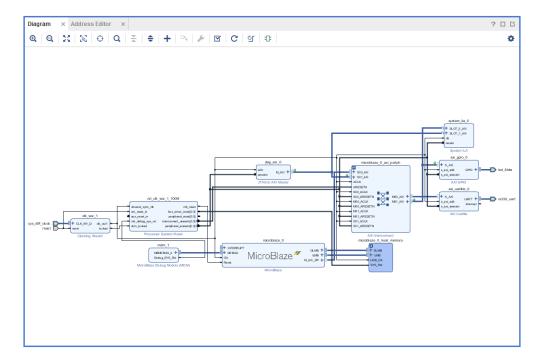

| Debug Flow in IP Integrator                                            |     |

| Implementing the Design Containing the Debug Cores                     |     |

| ILA Core and Timing Considerations                                     |     |

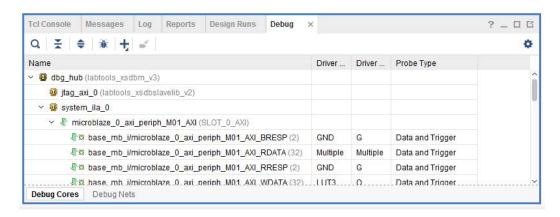

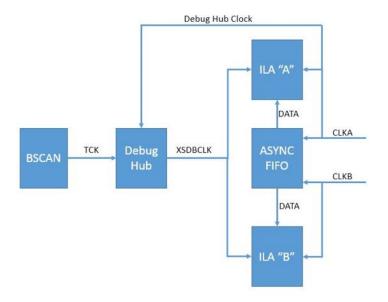

| Debug Cores Clocking Guidelines                                        |     |

| Debug Hub Insertion Guidelines                                         | 166 |

| Adding Vivado Debug Cores to a Dynamic Function eXchange Design        | 167 |

| Chapter 11: Debugging Logic Designs in Hardware                        | 168 |

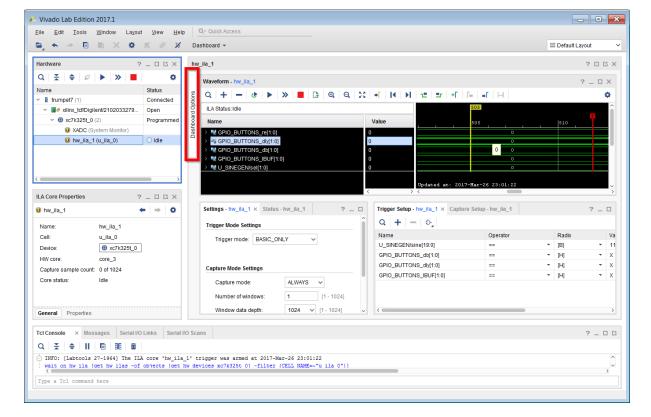

| Using Vivado Logic Analyzer to Debug the Design                        |     |

| Connecting to the Hardware Target and Programming the Device           |     |

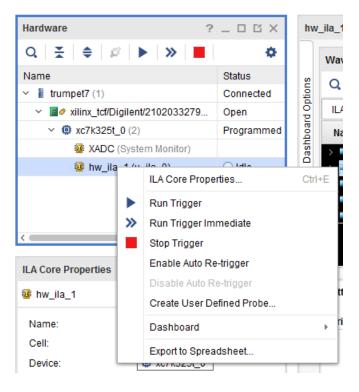

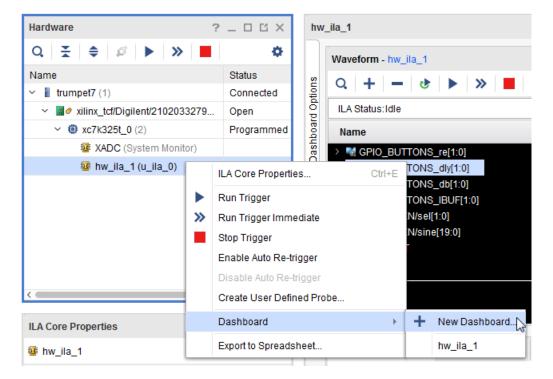

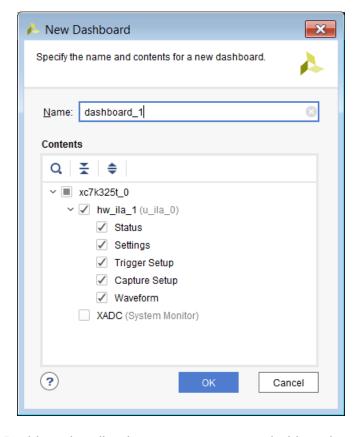

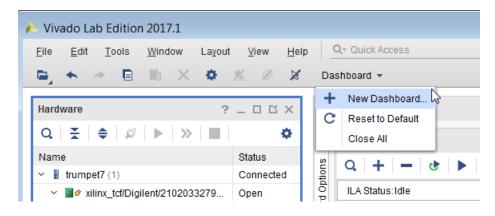

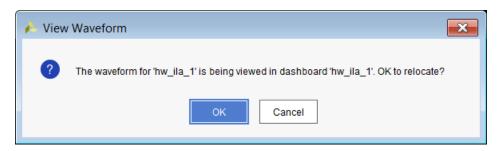

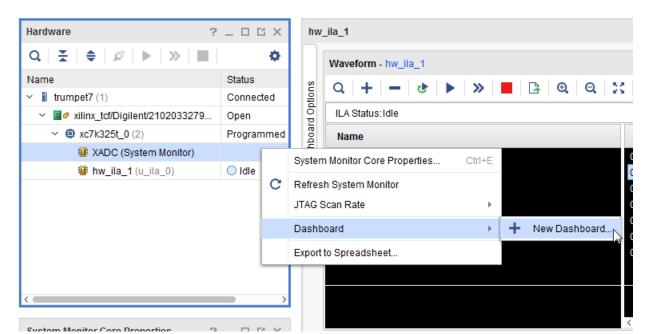

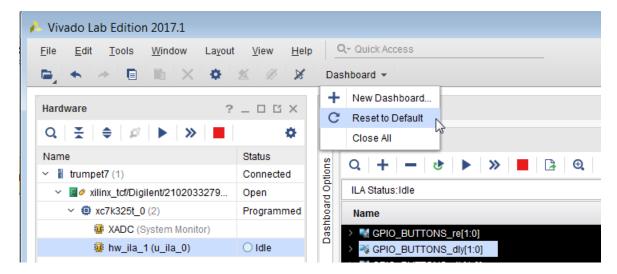

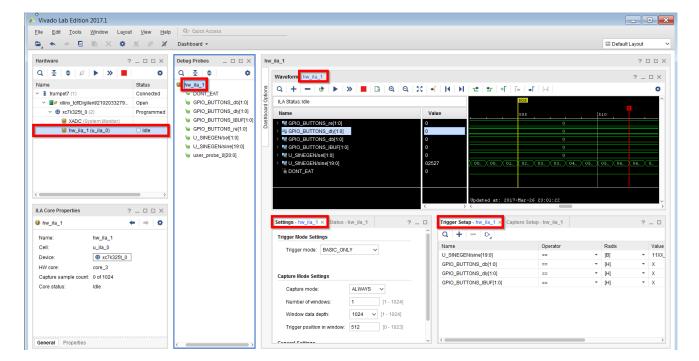

| Vivado Hardware Manager Dashboards                                     |     |

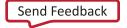

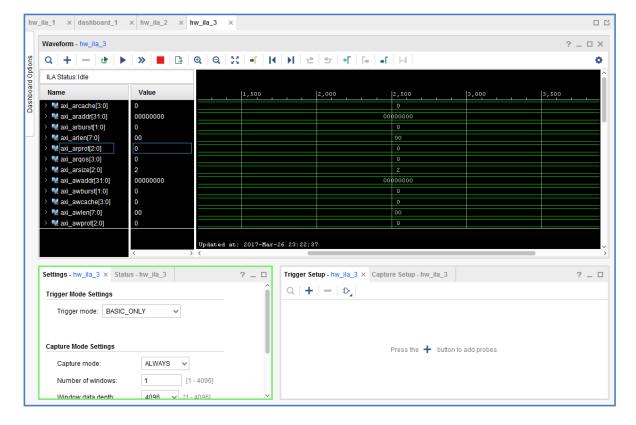

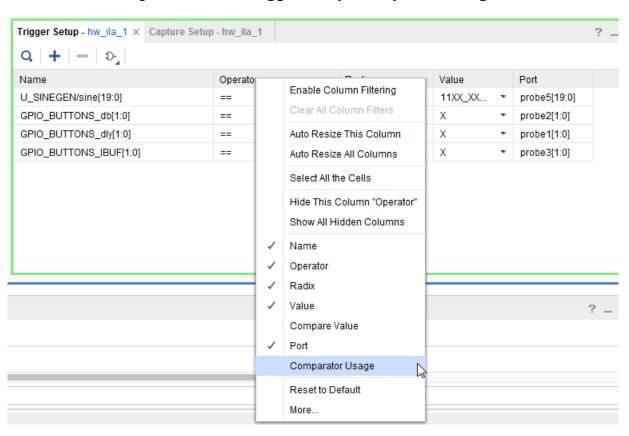

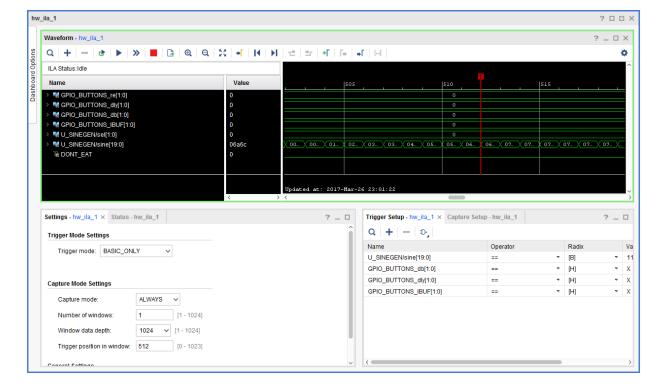

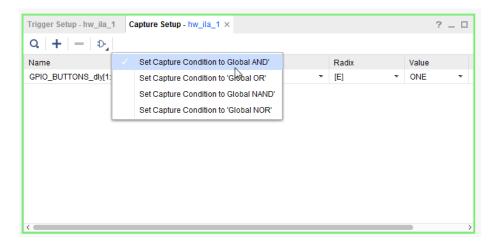

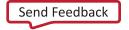

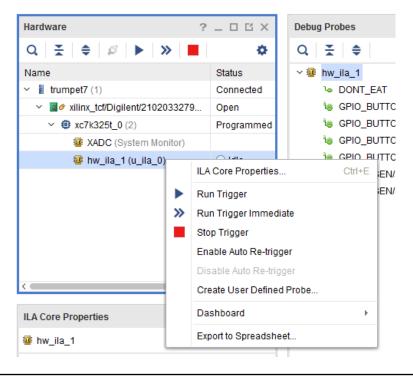

| Setting Up the ILA Core to Take a Measurement                          |     |

| Writing ILA Probes Information                                         |     |

| Reading ILA Probes Information                                         |     |

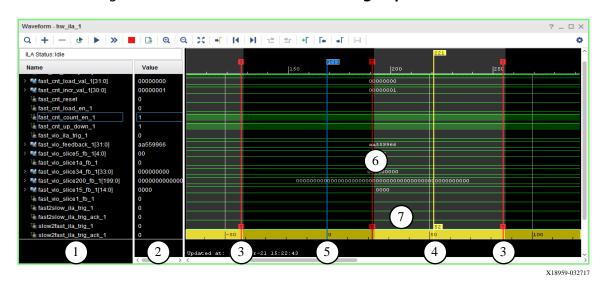

| Viewing Captured Data from the ILA Core in the Waveform Viewer         | 208 |

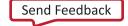

| Using Waveform ILA Trigger and Export Features                         |     |

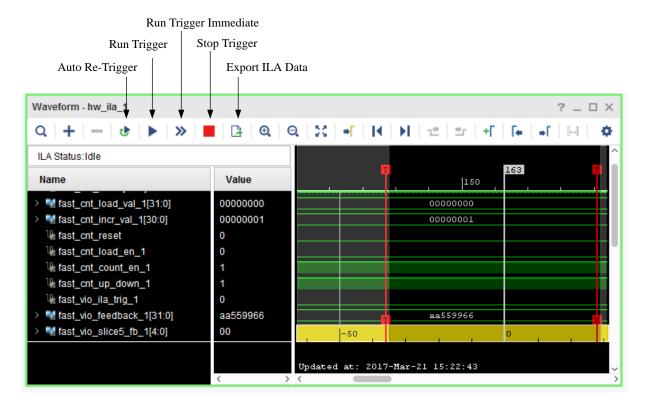

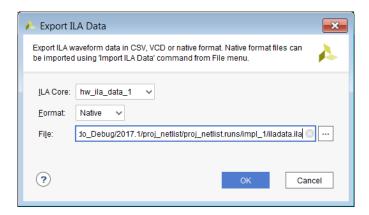

| Saving and Restoring Captured Data from the ILA Core                   | 211 |

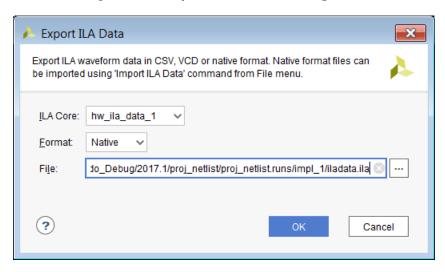

| Enumeration of Probe Values                                            | 213 |

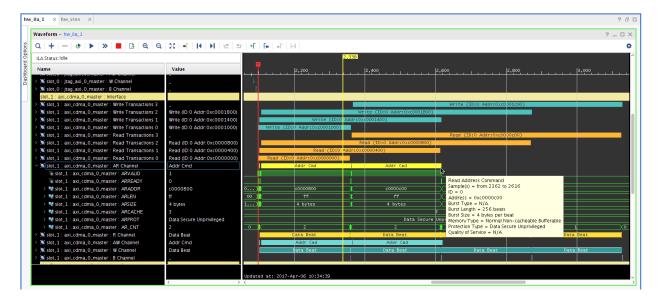

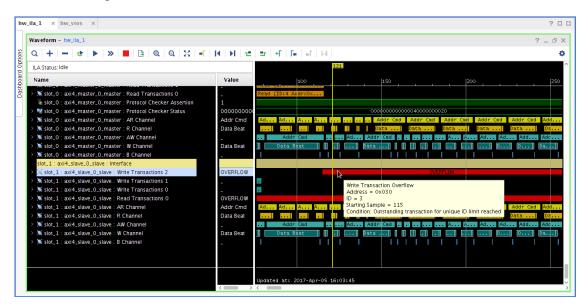

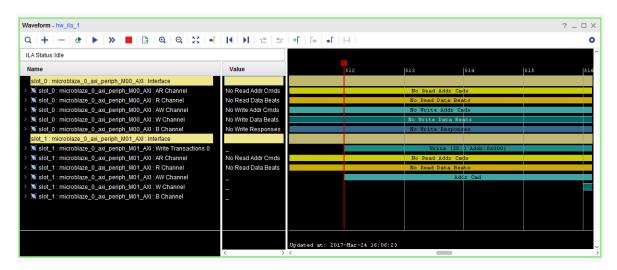

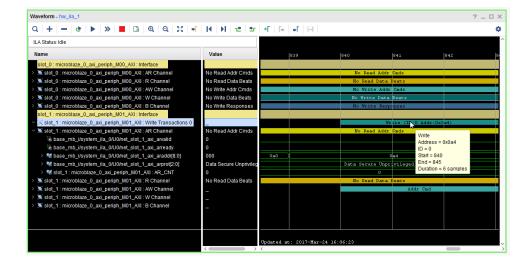

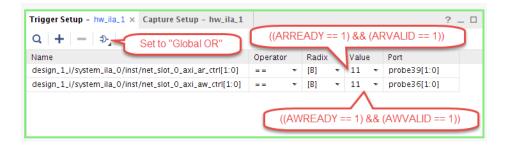

| Debugging AXI Interfaces in the Hardware Manager                       | 221 |

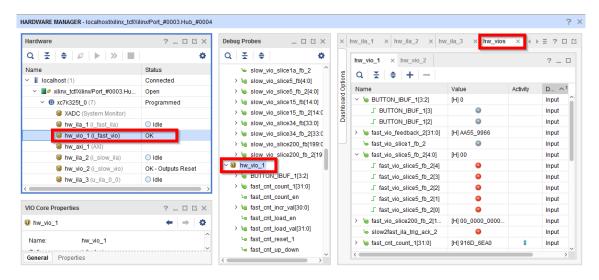

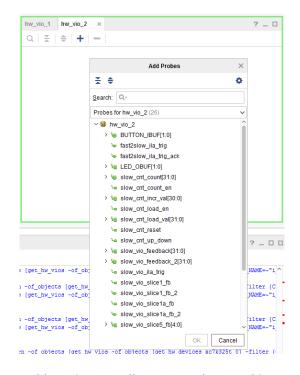

| Setting Up the VIO Core to Take a Measurement                          | 230 |

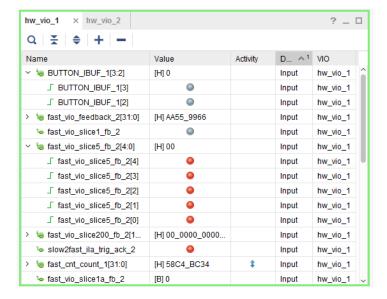

| Viewing the VIO Core Status                                            | 232 |

| Interacting with VIO Core Output Probes                                | 236 |

| Hardware System Communication Using the JTAG-to-AXI Master Debug Core. | 239 |

| Using Vivado Logic Analyzer in a Lab Environment                       | 242 |

| Description of Hardware Manager Tcl Objects and Commands               | 243 |

| Using Tcl Commands to Interact with a JTAG-to-AXI Master Core          | 247 |

| Using Tcl Commands to Take an ILA Measurement                          | 248 |

| Trigger At Startup                                                     | 249 |

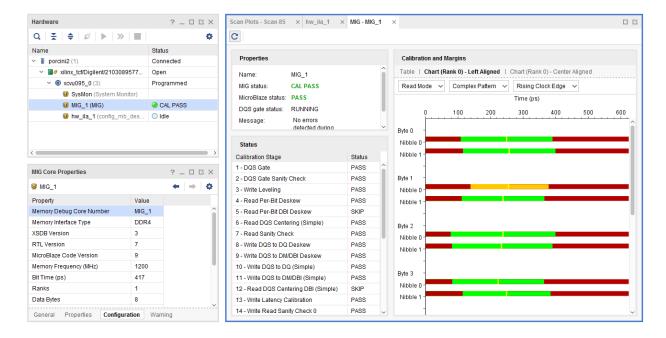

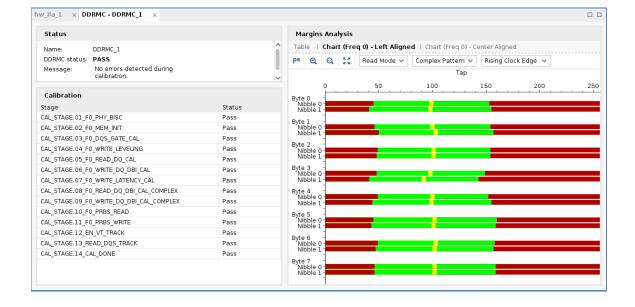

| Memory Calibration Debug                                               | 250 |

| Debugging Dynamic Function eXchange (DFX) Designs in Vivado Hardware                                                                 |     |

|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| Manager                                                                                                                              |     |

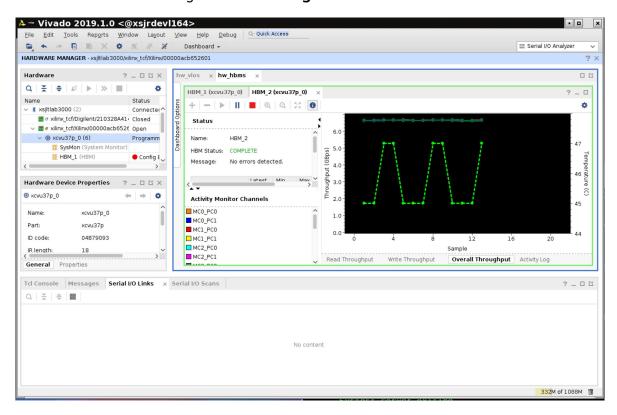

| High Bandwidth Memory (HBM) Monitor                                                                                                  | 253 |

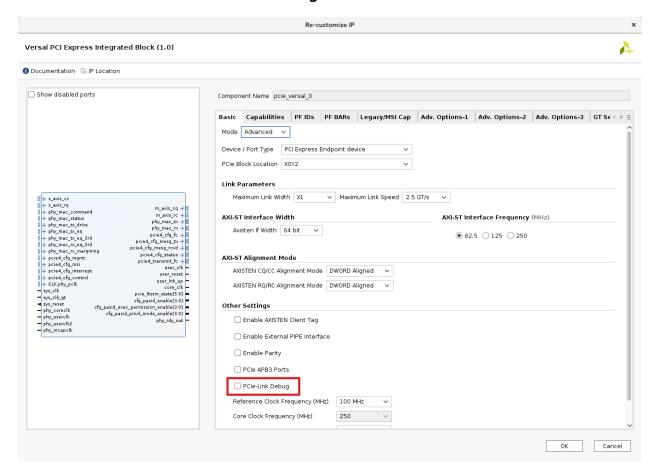

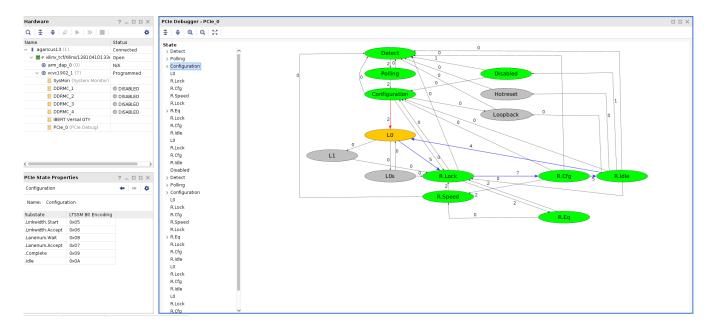

| PCI Express Link Debug                                                                                                               | 255 |

| ChipScoPy API                                                                                                                        | 257 |

| Chapter 12: Viewing ILA Probe Data in the Waveform Viewer                                                                            | 258 |

| ILA Data and Waveform Relationship                                                                                                   | 258 |

| Waveform Viewer Layout                                                                                                               | 259 |

| Waveform Viewer Operation                                                                                                            | 260 |

| Removing Probes from the Waveform                                                                                                    | 261 |

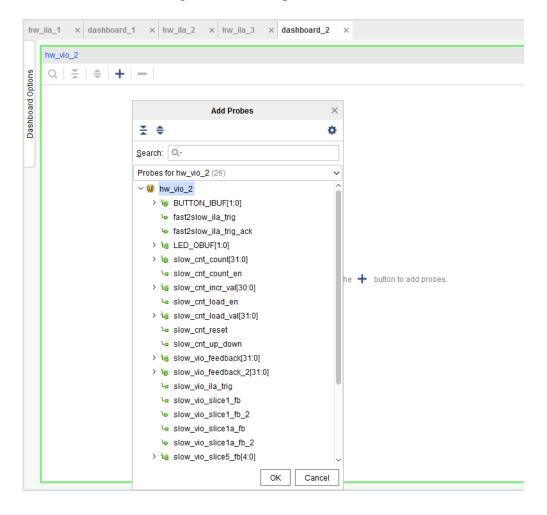

| Adding Probes to the Waveform                                                                                                        | 262 |

| Using Waveform ILA Trigger and Export Features                                                                                       | 263 |

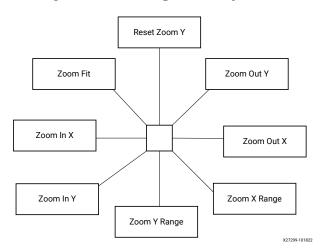

| Using the Zoom Features                                                                                                              | 264 |

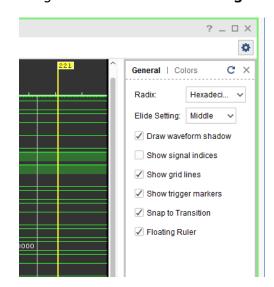

| Waveform Settings                                                                                                                    | 265 |

| Customizing the Configuration                                                                                                        | 266 |

| Renaming Objects                                                                                                                     | 270 |

| Bus Radixes                                                                                                                          | 272 |

| Viewing Analog Waveforms                                                                                                             |     |

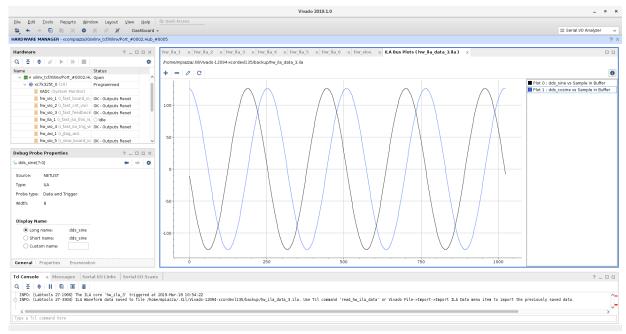

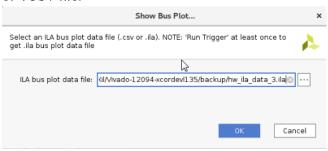

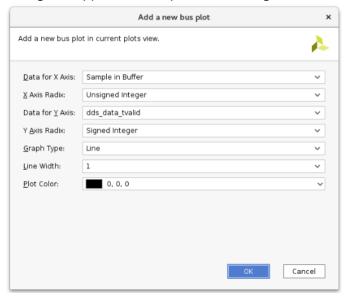

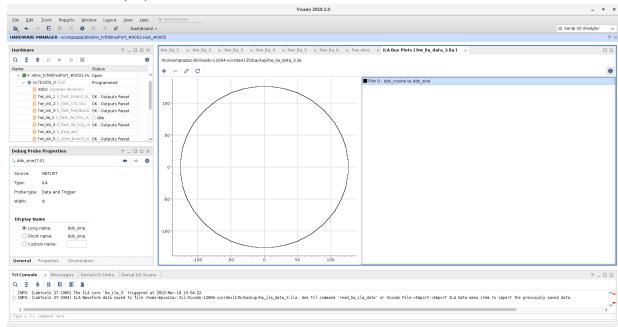

| Bus Plot Viewer                                                                                                                      | 275 |

| Zoom Gestures                                                                                                                        | 278 |

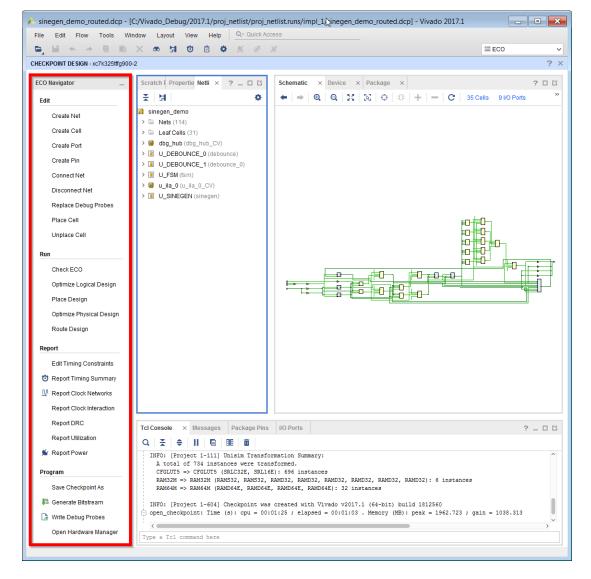

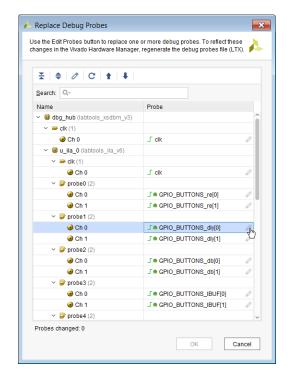

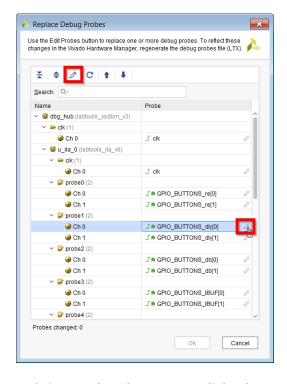

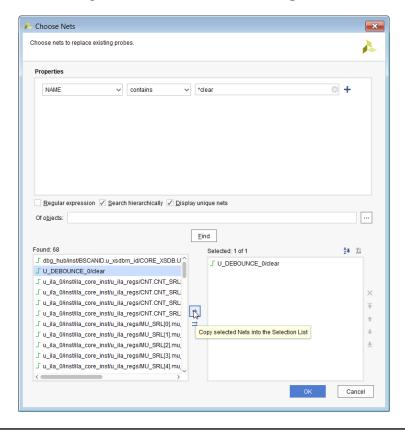

| Chapter 13: Debugging Designs Post Implementation                                                                                    | 279 |

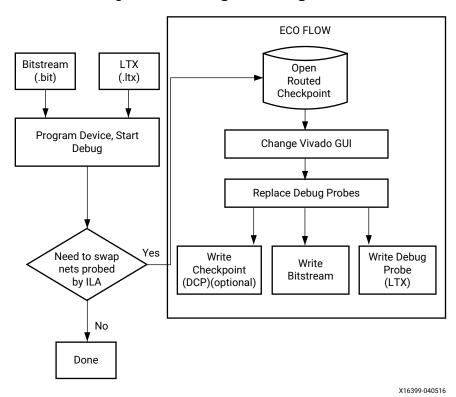

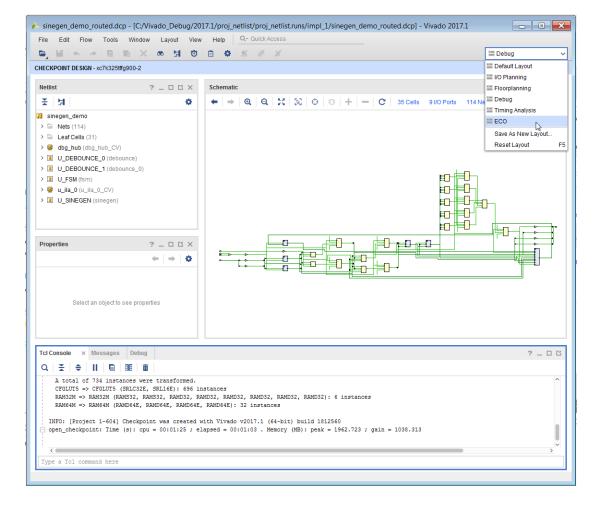

| Using Vivado ECO Flow to Replace Existing Debug Probes                                                                               |     |

| Replacing Debug Probes on a Placed and Routed Design Checkpoint                                                                      |     |

| Vivado ECO TCL Flow to Replace Existing Debug Probes                                                                                 |     |

| Incremental Compile with Debug Core (ILA) Modifications                                                                              |     |

| Chapter 14: Serial I/O Hardware Debugging Flows                                                                                      | 29( |

| Serial I/O Hardware Debugging Flows                                                                                                  |     |

| Chapter 15: Versal Serial I/O Hardware Debugging Flows                                                                               | 296 |

|                                                                                                                                      |     |

| Chapter 16: Debugging the Serial I/O Design in Hardware                                                                              |     |

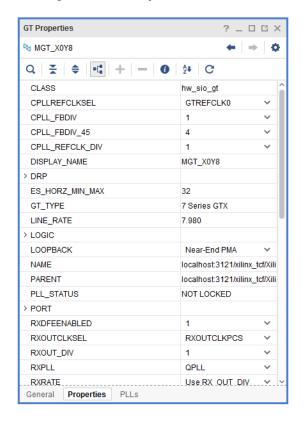

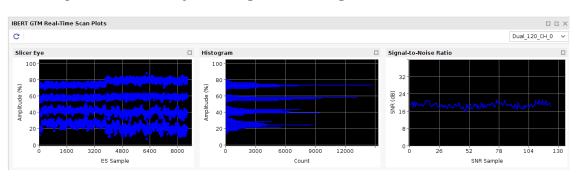

| Using Vivado Serial I/O Analyzer to Debug the DesignViewing Slicer Eye, Histogram, and Signal-to-Noise Ratio (GTM Transceivers Only) |     |

|                                                                                                                                      |     |

| Appendix A: Device Configuration Bitstream or PDI Settings                                                                           | 314 |

| 7 Series Bitstream Settings                                                                                                          | 314 |

|                                                                                                                                                                                                                                                            | 319                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| UltraScale Bitstream Settings                                                                                                                                                                                                                              | 325                      |

| Zynq UltraScale+ MPSoC Bitstream Settings                                                                                                                                                                                                                  | 331                      |

| Zynq-7000 Bitstream Settings                                                                                                                                                                                                                               |                          |

| Versal ACAP Programmable Device Image (PDI) Settings                                                                                                                                                                                                       | 338                      |

| Appendix B: Trigger State Machine Language Description                                                                                                                                                                                                     | on340                    |

| States                                                                                                                                                                                                                                                     | 340                      |

| Goto Action                                                                                                                                                                                                                                                | 340                      |

| Conditional Branching                                                                                                                                                                                                                                      | 341                      |

| Counters                                                                                                                                                                                                                                                   | 341                      |

| Flags                                                                                                                                                                                                                                                      | 342                      |

| Conditional Statements                                                                                                                                                                                                                                     | 342                      |

| Appendix C: Low Level SVF JTAG Commands                                                                                                                                                                                                                    | 348                      |

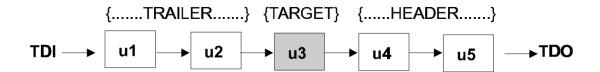

| Header Data Register (HDR), Header Instruction Register (HIR)                                                                                                                                                                                              | 348                      |

| TDR, TIR (Trailer Data Register, Trailer Instruction Register)                                                                                                                                                                                             | 349                      |

| scan_ir_hw                                                                                                                                                                                                                                                 | 350                      |

| scan_dr_hw                                                                                                                                                                                                                                                 | 351                      |

| Multi Chain SVF Operation                                                                                                                                                                                                                                  | 352                      |

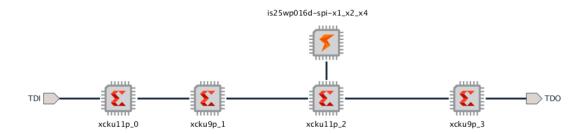

| Appendix D: JTAG Cables and Devices Supported by hw_ Appendix E: Programming FTDI Devices for Vivado Haro Manager Support                                                                                                                                  | dware                    |

| Appendix F: Configuration Memory Support                                                                                                                                                                                                                   |                          |

| ADDENOIX F. CONHOUTATION WEINOLV SUDDON                                                                                                                                                                                                                    |                          |

|                                                                                                                                                                                                                                                            |                          |

| Artix-7 Configuration Memory Devices                                                                                                                                                                                                                       | 360                      |

| Artix-7 Configuration Memory Devices                                                                                                                                                                                                                       | 360<br>368               |

| Artix-7 Configuration Memory Devices<br>Kintex-7 Configuration Memory Devices<br>Spartan-7 Configuration Memory Devices                                                                                                                                    | 360<br>368<br>376        |

| Artix-7 Configuration Memory Devices<br>Kintex-7 Configuration Memory Devices<br>Spartan-7 Configuration Memory Devices<br>Virtex-7 Configuration Memory Devices                                                                                           | 360<br>368<br>376<br>381 |

| Artix-7 Configuration Memory Devices<br>Kintex-7 Configuration Memory Devices<br>Spartan-7 Configuration Memory Devices<br>Virtex-7 Configuration Memory Devices<br>Artix UltraScale+ Configuration Memory Devices                                         | 360<br>368<br>376<br>381 |

| Artix-7 Configuration Memory Devices  Kintex-7 Configuration Memory Devices  Spartan-7 Configuration Memory Devices  Virtex-7 Configuration Memory Devices  Artix UltraScale+ Configuration Memory Devices  Kintex UltraScale Configuration Memory Devices |                          |

| Artix-7 Configuration Memory Devices                                                                                                                                                                                                                       |                          |

| Artix-7 Configuration Memory Devices                                                                                                                                                                                                                       |                          |

| Artix-7 Configuration Memory Devices                                                                                                                                                                                                                       |                          |

| Artix-7 Configuration Memory Devices                                                                                                                                                                                                                       |                          |

| Artix-7 Configuration Memory Devices                                                                                                                                                                                                                       |                          |

| Versal Configuration Memory Devices                | 436 |

|----------------------------------------------------|-----|

| Appendix G: Command Line Options for hw_server     | 444 |

| Standard hw_server Options                         | 444 |

| Advanced Options                                   | 446 |

| Appendix H: Additional Resources and Legal Notices | 452 |

| Xilinx Resources                                   | 452 |

| Solution Centers                                   | 452 |

| Documentation Navigator and Design Hubs            | 452 |

| References                                         | 453 |

| Training Courses                                   | 454 |

| Revision History                                   |     |

| Please Read: Important Legal Notices               | 455 |

|                                                    |     |

# Introduction

# **Navigating Content by Design Process**

Xilinx® documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal® ACAP design process Design Hubs and the Design Flow Assistant materials can be found on the Xilinx.com website. This document covers the following design processes:

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, functional simulation, and evaluating the Vivado® timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Chapter 9: Debugging the Design

- Chapter 10: In-System Logic Design Debugging Flows

- Chapter 11: Debugging Logic Designs in Hardware

- Chapter 12: Viewing ILA Probe Data in the Waveform Viewer

- Chapter 13: Debugging Designs Post Implementation

- Board System Design: Designing a PCB through schematics and board layout. Also involves

power, thermal, and signal integrity considerations. Topics in this document that apply to this

design process include:

- Chapter 4: Programming the Device

- Chapter 5: Remote Debugging in Vivado

- Chapter 6: Programming Configuration Memory Devices

- Chapter 7: Advanced Programming Features

- Chapter 8: Serial Vector Format (SVF) File Programming

- Chapter 14: Serial I/O Hardware Debugging Flows

- Chapter 16: Debugging the Serial I/O Design in Hardware

- Appendix A: Device Configuration Bitstream or PDI Settings

- Appendix C: Low Level SVF JTAG Commands

- Appendix D: JTAG Cables and Devices Supported by hw\_server

- Appendix F: Configuration Memory Support

### **Getting Started**

After successfully implementing your design, the next step is to run it in hardware by programming the FPGA or ACAP and debugging the design in-system. All of the necessary commands to perform programming of FPGAs and in-system debugging of the design are in the Program and Debug section of the Flow Navigator in the Vivado® Integrated Design Environment (IDE) (see the following figure).

Figure 1: Program and Debug Section of the Flow Navigator Panel

### **Debug Terminology**

#### ILA

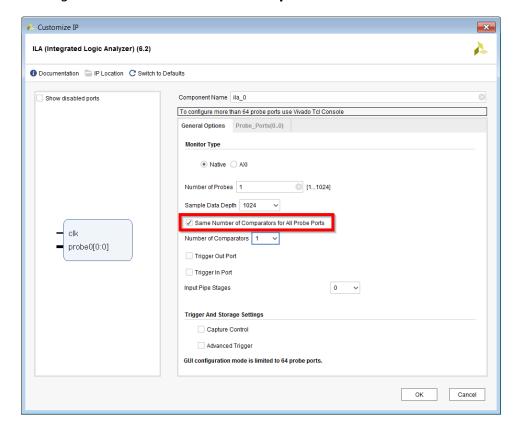

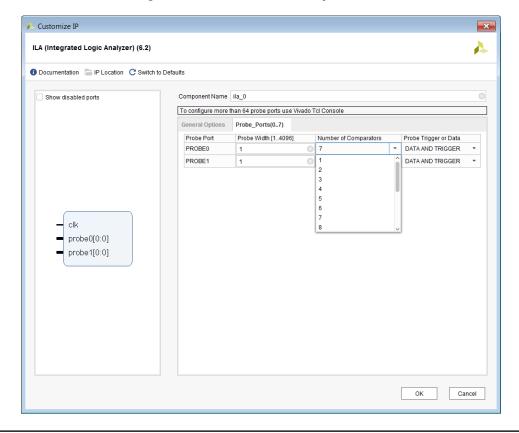

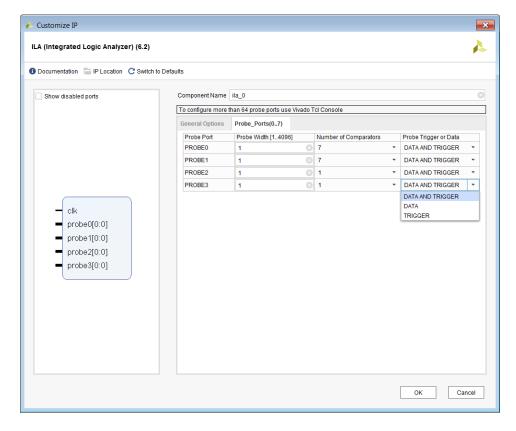

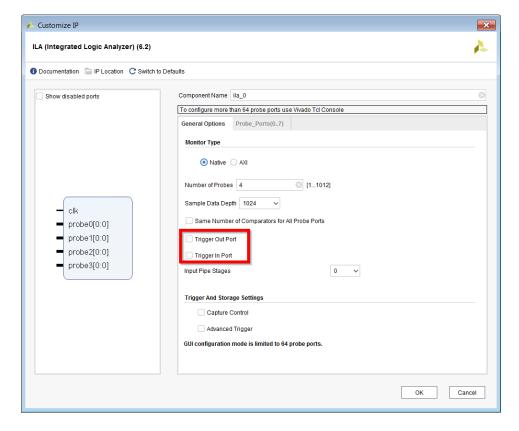

The Integrated Logic Analyzer (ILA) feature allows you to perform in-system debugging of post-implemented designs on an FPGA, SoC, or Versal® device. This feature should be used when there is a need to monitor signals in the design. You can also use this feature to trigger on hardware events and capture data at system speeds.

The ILA core can be instantiated in your RTL code or inserted post synthesis in the Vivado design flow. Detailed documentation on the ILA core IP can be found in the *Integrated Logic Analyzer LogiCORE IP Product Guide* (PG172).

#### **Related Information**

In-System Logic Design Debugging Flows Debugging Logic Designs in Hardware

#### VIO

The Virtual Input/Output (VIO) debug feature can both monitor and drive internal FPGA, SoC, or Versal ACAP signals in real time. In the absence of physical access to the target hardware, you can use this debug feature to drive and monitor signals that are present on the real hardware.

This debug core needs to be instantiated in the RTL code, hence you need to know up-front, what nets to drive. The IP Catalog lists this core under the Debug category. Detailed documentation on the VIO core IP can be found in the *Virtual Input/Output LogiCORE IP Product Guide* (PG159).

#### **Related Information**

Debugging Logic Designs in Hardware

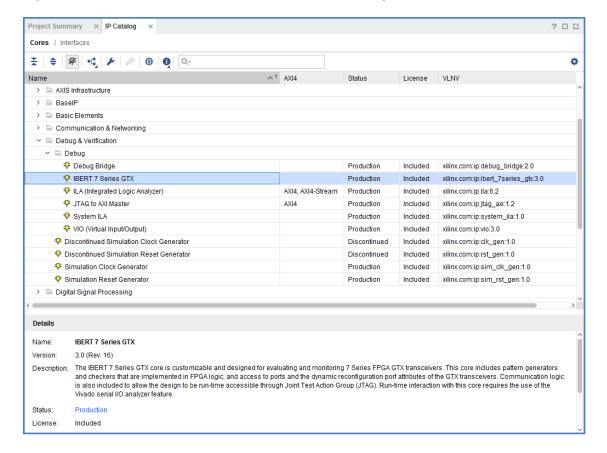

#### **IBERT**

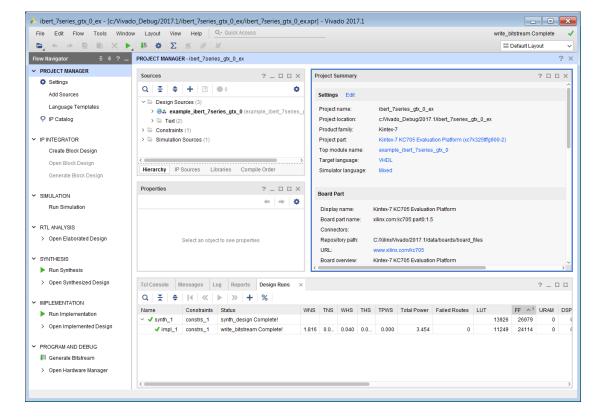

The Integrated Bit Error Ratio Tester (IBERT) Serial Analyzer design enables in-system serial I/O validation and debug. This allows you to measure and optimize your high-speed serial I/O links in your FPGA-based system. Xilinx recommends using the IBERT Serial Analyzer design when you are interested in addressing a range of in-system debug and validation problems from simple clocking and connectivity issues to complex margin analysis and channel optimization issues.

Xilinx recommends using the IBERT Serial Analyzer design when you are interested in measuring the quality of a signal after a receiver equalization has been applied to the received signal. This ensures that you are measuring at the optimal point in the TX-to-RX channel thereby ensuring real and accurate data. Users can access this design by selecting, configuring, and generating the IBERT core from the IP Catalog and selecting the Open Example Design feature of this core. See Serial I/O Hardware Debugging Flows and Chapter 16: Debugging the Serial I/O Design in Hardware for more details on the IBERT core and its usage methodology in the Vivado Design Suite.

#### **Related Information**

Debugging the Serial I/O Design in Hardware Serial I/O Hardware Debugging Flows

#### JTAG-to-AXI Master

**Note:** The JTAG-to-AXI Master is not supported on Versal ACAP devices as the built-in CIPS AXI Master interfaces can be used in combination with the Debug Packet Controller (DPC) to generate AXI transactions without additional IP.

The JTAG-to-AXI Master debug feature is used to generate AXI transactions that interact with various AXI full and AXI lite slave cores in a system that is running in hardware. Xilinx recommends that you use this core to generate AXI transactions and debug/drive AXI signals internal to an FPGA at run time. This core can be used in designs without processors as well.

The IP Catalog lists this core under the Debug category. Debugging Logic Designs in Hardware of this guide has more details about the JTAG-to-AXI Master core and its usage methodology in the Vivado Design Suite. Detailed documentation on the JTAG-to-AXI IP core can be found in the JTAG to AXI Master LogiCORE IP Product Guide (PG174).

#### **Related Information**

Debugging Logic Designs in Hardware

#### **Debug Hub**

On 7 series and UltraScale™ architectures, the Vivado Debug Hub core provides an interface between the JTAG Boundary Scan (BSCAN) interface of the FPGA and the Vivado Debug cores including the following types of cores:

- Integrated Logic Analyzer (ILA)

- Virtual Input/Output (VIO)

- Integrated Bit Error Ratio Tester (IBERT)

- JTAG-to-AXI

Memory IP

**IMPORTANT!** The Vivado Debug Hub core cannot be instantiated into the design. It is inserted by Vivado during the  $opt\_design$  stage.

#### **AXI4 Debug Hub**

On Versal® ACAP architectures the AXI4 Debug Hub is an IP core that provides an interface between the AXI4 Master interface of the CIPS and the AXI4-Stream interface on the Vivado Hardware Debug cores including the following:

- Integrated Logic Analyzer (ILA)

- Virtual Input/Output (VIO)

- Soft Memory IP

**Note:** On Versal devices, the AXI4 Debug Hub can be manually instantiated as an IP or inserted automatically during opt\_design, just as with previous architectures.

#### System ILA

The System Integrated Logic Analyzer (System ILA) IP core is a logic analyzer that allows you to perform in-system debugging of post-implemented designs on an FPGA device. Use this IP when you need to monitor interfaces and signals in the IP integrator Block Design. You can also use this feature to trigger on interface and signal related hardware events and capture data at system speeds. This ensures the intuitive presentation of interface events in the Hardware Manager when debugging the design on an FPGA or ACAP. This IP offers AXI interface debug and monitoring capability along with AXI4-MM and AXI4-Stream protocol checking.

Since the System ILA core is synchronous to the design being monitored, all design clock constraints that are applied to your design are also applied to the components of the System ILA core. Detailed documentation on the System ILA core IP can be found in the System Integrated Logic Analyzer LogiCORE IP Product Guide (PG261).

Note: On Versal® devices the System ILA functionality is available using the Versal ILA core.

#### **Debug Bridge**

**Note:** The Debug Bridge IP is not supported on Versal architectures.

The Debug Bridge IP core is a controller that provides multiple options to communicate with the debug cores in the design.

The primary use case for a Debug Bridge is to use a Xilinx Virtual Cable (XVC) to remotely debug designs through Ethernet or other interfaces without the need for a JTAG cable.

The other common use case is for debugging Dynamic Function eXchange and Tandem PCIe with Field Updates designs. For more information on the Tandem PCIe with Field Updates flow and Debug Bridge refer to UltraScale+ Devices Integrated Block for PCI Express LogiCORE IP Product Guide (PG213).

The Debug Bridge can also be used with the PCle® core in systems where JTAG is not the preferred communication and debug mechanism. For more information on the using the XVC flow with the PCle core and Debug Bridge refer to *UltraScale+ Devices Integrated Block for PCI Express LogiCORE IP Product Guide* (PG213).

Detailed documentation on the Debug Bridge core IP can be found in the *Debug Bridge LogiCORE* IP Product Guide (PG245).

#### **In-System IBERT**

Note: In-System IBERT is supported on UltraScale and UltraScale+ only.

The In-System IBERT IP enables you to perform 2-D eye-scans of UltraScale and UltraScale+ transceivers in your design, using the Vivado Serial IO Analyzer. The IP uses data from the design to plot the eye-scan of the transceivers in real time while they interact with the rest of the system. This IP can be integrated with user logic in the design or Xilinx transceiver based IPs (for example GT Wizard, or Aurora, etc.).

Detailed documentation on the In-System IBERT IP can be found in the In-System IBERT LogiCORE IP Product Guide (PG246).

#### **IBERT GTR**

IBERT UltraScale+ GTR can be used to evaluate and monitor GTR transceivers in Zynq UltraScale + MPSoC devices. With this feature, you can accomplish the following tasks:

- · Perform eye scans with user data

- Change GTR settings

- View link status

- Check the "lock" status of all PLLs used by all GTR lanes

However, IBERT GTR does not provide the following capabilities:

- Perform eye scans with raw PRBS data patterns

- Measure Bit Error Ratio (no bit or error counters)

Note that this solution is software based, meaning that no IP or logic is required in the programmable logic of the device.

## Vivado Lab Edition

Vivado<sup>®</sup> Lab Edition is a standalone installation of the full Vivado Design Suite with all the features and capabilities required to program and debug Xilinx<sup>®</sup> devices after generating the device image. Typical usage is for programming and debug in the lab environment where machines have a smaller amount of resources in terms of disk space, memory, and connectivity. Vivado Lab Edition has a reduced product footprint of around 2.4 GB after installation and the install package size is 1 GB.

#### **Installation**

To install the Vivado Lab Edition, select Lab Edition from the Unified Installer.

Detailed installation, licensing and release information is available in Vivado Design Suite User Guide: Release Notes, Installation, and Licensing (UG973).

#### **Launching Vivado Lab Edition on Windows**

To launch Vivado Lab Edition, select the following:

Start  $\rightarrow$  All Programs  $\rightarrow$  Xilinx Design Tools  $\rightarrow$  Vivado Lab 2020.2  $\rightarrow$  Vivado Lab 2021.1

# Launching the Vivado Lab Edition from the Command Line on Windows or Linux

Enter the following command at the command prompt:

vivado\_lab

**TIP:** To run *vivado\_lab* at the command prompt, set up your environment using the following script:

C:\Xilinx\Vivado\_Lab\2020.x\settings64.(bat|sh)

You can open the Vivado Lab Edition from any directory. However, Xilinx recommends running it from a writable project directory, because the Vivado Lab Edition log and journal files are written to the launch directory. When running from a command prompt, launch the Vivado IDE from the project directory, or use the <code>vivado\_lab -log</code> and <code>journal</code> options to specify a location. When using a Windows shortcut, you must modify the Start in folder, which is a property of the shortcut. Failure to launch from a writable project directory results in warnings and unpredictable behavior from the tool.

### **Using the Vivado Lab Edition**

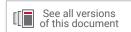

When you launch the Vivado Lab Edition, the Getting Started page (see the following figure) displays and provides you with different options to help you begin working with the Vivado Lab Edition.

Figure 2: Vivado Lab Edition Welcome Screen

#### Starting with a Project

To program or debug your design, you can create or open a project, and connect to a target server and device. The Quick Start section of the Getting Started Page provides links for easy access to the following tasks:

- Create a project.

- Open existing projects

Note: You can also open recently accessed projects from the Recent Projects list.

#### **Opening the Hardware Manager**

You can open the Vivado Design Suite Hardware Manager to download your design bitstream to a device. Use the Vivado logic analyzer and Vivado serial I/O analyzer features of the Hardware Manager to debug your design. For example, you can add ILA, VIO, and JTAG-to-AXI cores to your design for debugging in the Vivado logic analyzer, or use the IBERT example design from the Xilinx IP catalog to test and configure the GTs in your design with the Vivado serial I/O analyzer.

#### **Reviewing Documentation and Videos**

From the Getting Started page, you can use the Xilinx Documentation Navigator to access documentation, including user guides, tutorials, videos, and the release notes.

#### **Vivado Lab Edition Project**

Vivado Lab Edition allows users in the lab to create projects. All the relevant programming and runtime debug preferences and settings are stored in the project. When the project is reopened, the settings and preferences are restored back into the tool. A Vivado Lab Edition project can be created in both the Vivado Lab Edition tool as well as in Vivado Design Suite.

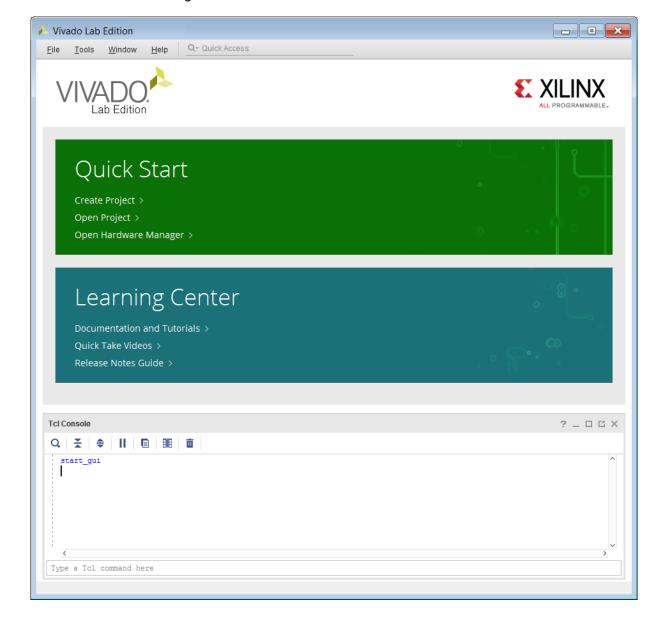

#### **Create a New Project**

To create a new project in Vivado Lab Edition, click the **Create New Project** icon as shown below. Enter the project name and location in the New Vivado Lab Edition Project dialog box. When you create a new project, Vivado Lab Edition creates a project file. The project file has the same name as the project name entered in the New Vivado Lab Edition Project dialog box with the <code>.lpr</code> extension. See the following figure.

Figure 3: Vivado Lab Edition Creating a New Project

#### **Creating Projects Using Tcl Commands**

You can also create a project using Tcl commands. Enter the following command in the Tcl Console of Vivado Lab Edition or source them from a Tcl file.

create\_project project\_1 C:/Lab\_edition/project\_1

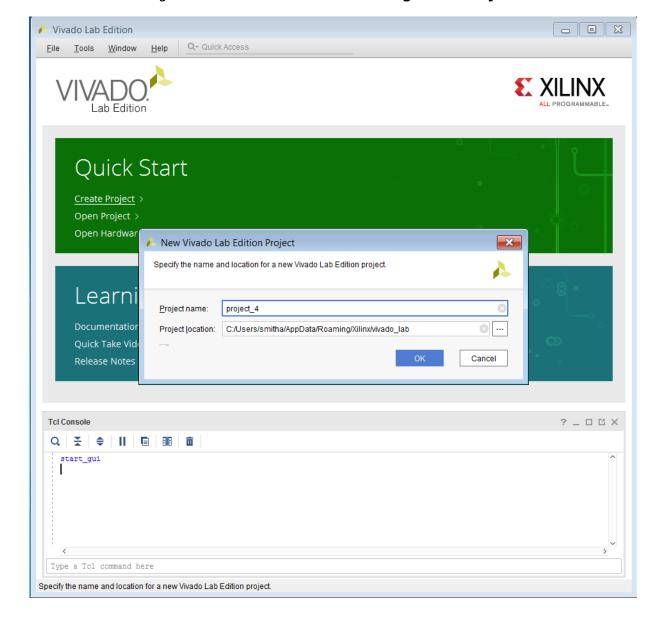

#### **Opening the Project**

To open existing projects, click the open project icon as shown in the following figure or double-click a project in the **Recent Projects** list. This opens a browser that enables you to open any Vivado Lab Edition project file (.1pr extension). By default, the last ten previously opened projects are listed in the Recent Projects list. To change this number, click **Tools**  $\rightarrow$  **Settings** and update the Project options. Vivado Lab Edition checks to ensure that the project data is available before displaying the projects.

Figure 4: Vivado Lab Edition Open Project Dialog

#### **Opening Projects Using Tcl Commands**

You can also open a project using Tcl commands. Enter the following command in the **Tcl Console** of the Vivado Lab Edition or source them from a .tcl file.

open\_project C:/Lab\_edition/project\_1/project\_1.lpr

# Using an Existing Device Image and Debug Probes Files in Vivado Lab Edition

You can use the existing device image (.bit or .pdi) and .ltx file from a previous implementation run in the lab machine where Vivado Lab Edition is installed.

Typical flow would entail the following:

- 1. Create a new Vivado Lab Edition project.

- 2. Connect to the board.

- 3. Specify the .bit or .pdi file and .ltx file for the project.

- 4. You can either manually copy these files or point to them on a network drive.

- 5. Program the device.

- 6. Debug the design in your hardware.

- 7. Changes are continuously saved to the project

- 8. User preferences, runtime manager debug dashboard, and window settings are continuously saved to the project.

- 9. User preferences, runtime manager debug dashboard, and window settings are restored at project reopen.

# Using an Existing .lpr Project from Vivado Design Suite Edition

Vivado Design Suite creates an .lpr file at project startup and populates this file with appropriate details when you use the Hardware Manager to program and/or debug the design in the project. This file is located in the project\_name.hw directory and is named project\_name.lpr. This project file can be opened in the Vivado Lab Edition.

Typical flow would entail:

- 1. Click the **Open Project** icon on the Vivado Lab Edition start page.

- 2. Traverse to the project\_name.hw directory, which is located inside the Vivado IDE project directory

- 3. Select the .lpr project file inside the project\_name.hw directory and click OK.

- 4. Connect to your hardware.

- 5. Program and debug with the correct device image file and .1tx file from the appropriate Vivado runs directory

- 6. User preferences, runtime manager debug dashboard, and window settings are restored at project open.

### **Programming Features**

After the project is open and the Hardware Manager is connected with a target device, you can use all the programming features that were available in the Vivado Design Suite from the Vivado Lab Edition. All the programming related Tcl commands are supported in Vivado Lab Edition. For more details on the programming features available refer to Programming Configuration Memory Devices.

#### **Related Information**

**Programming Configuration Memory Devices**

## **Debug Features**

After you open the project and connect the Hardware Manager with a target device, you can use all the debug features that were available in the Vivado Design Suite from the Vivado Lab Edition. All the debug related Tcl commands are supported in Vivado Lab Edition. For more details on the debug features available refer to Debugging Logic Designs in Hardware of this user guide.

#### **Related Information**

Debugging Logic Designs in Hardware

# Generating the Bitstream or Device Image

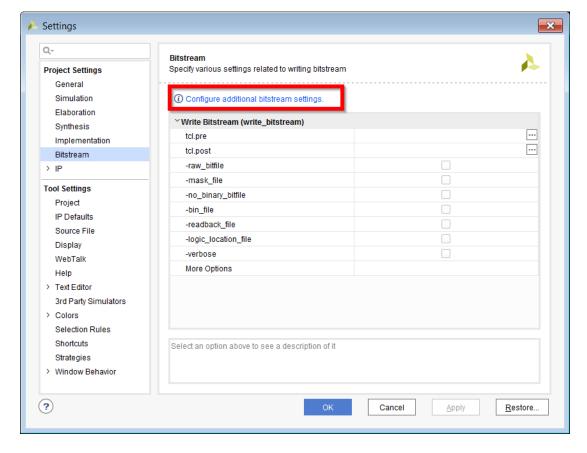

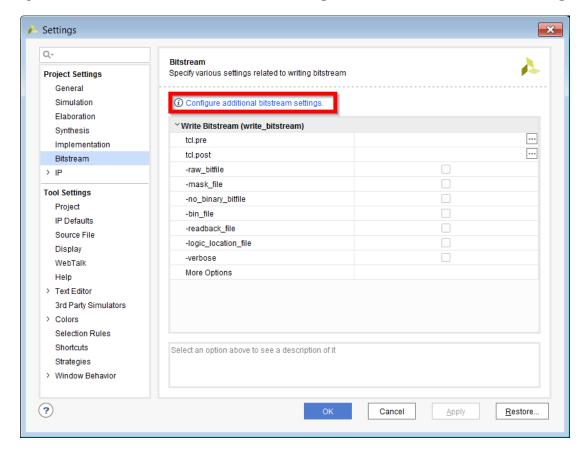

Before generating a bitstream or device image, it is important to review the settings to make sure they are correct for your design.

There are two types of bitstream and device image settings in Vivado® IDE:

- 1. Bitstream or Device Image file format settings.

- 2. Device configuration settings.

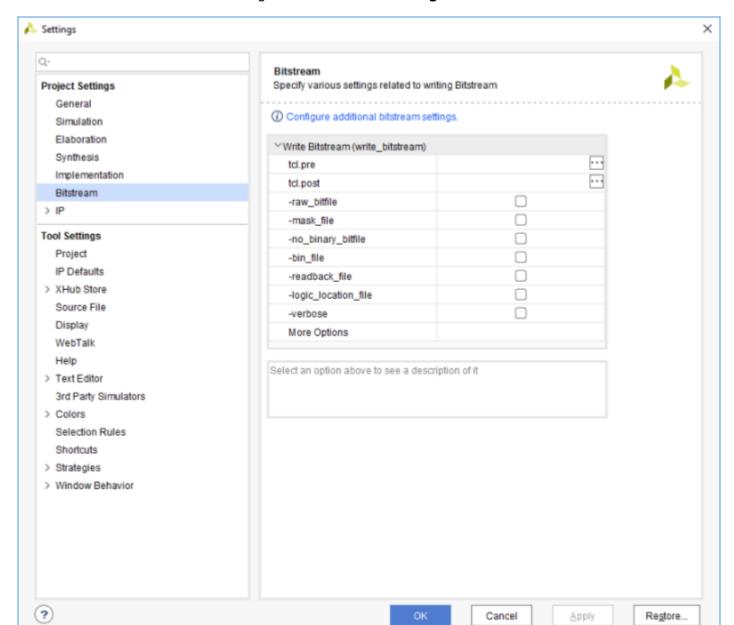

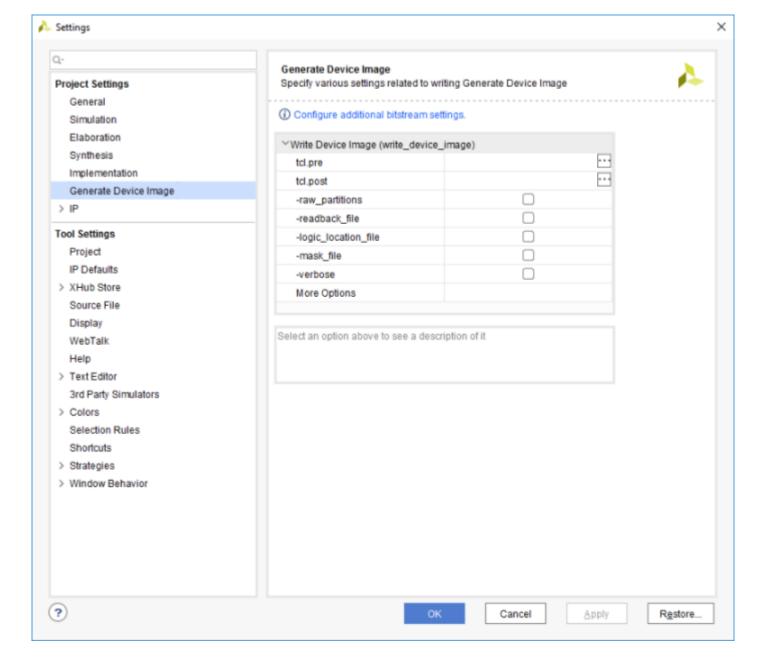

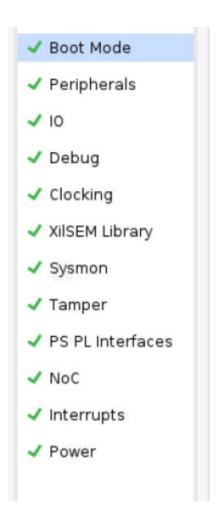

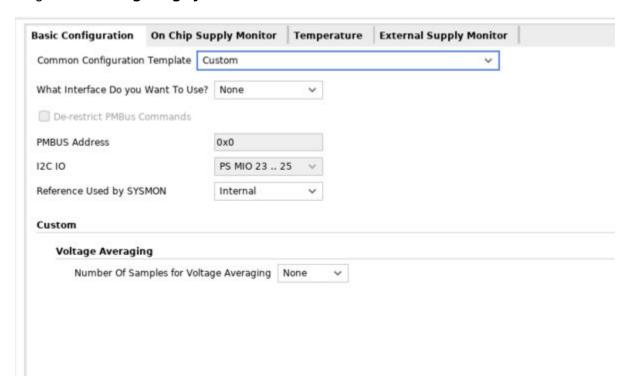

If a Versal® device is targeted, a programmable device image (.pdi) is generated instead of a bitstream. The procedure to change the device image settings is similar to previous architectures however the menu options, Tcl commands, and available settings will differ. To access the device image settings select Settings  $\rightarrow$  Generate Device Image in the Vivado Flow Navigator or Flow  $\rightarrow$  Settings  $\rightarrow$  Generate Device Image Settings... menu selection to open the Device Image section in the Settings popup window (see the following figure). The device image data file can be generated using the write\_device\_image Tcl command or by using the Write Device Image button in the Vivado flow navigator. For more details about the PDI format, refer to the Bootgen User Guide (UG1283).

Figure 5: Bitstream Settings Panel

Figure 6: Generate Device Image Settings Panel

# **Changing the Bitstream File Format Settings**

By default, the write\_bitstream Tcl command generates a binary bitstream (.bit) file only. You can optionally change the file formats written out by the write\_bitstream Tcl command by using the following command switches:

- -raw\_bitfile: (Optional) This switch causes write\_bitstream to write a raw bit file (.rbt), which contains the same information as the binary bitstream file, but is in ASCII format. The output file is named <filename>.rbt.

- -mask\_file: (Optional) Write a mask file (.msk), which has mask data where the configuration data is in the bitstream file. This file determines which bits in the bitstream should be compared to readback data for verification purposes. If a mask bit is 0, that bit should be verified against the bitstream data. If a mask bit is 1, that bit should not be verified. The output file is named <file>.msk.

- -no\_binary\_bitfile: (Optional) Do not write the binary bitstream file (.bit). Use this command when you want to generate the ASCII bitstream or mask file, or to generate a bitstream report, without generating the binary bitstream file.

- -logic\_location\_file: (Optional) Creates an ASCII logic location file (.11) that shows the bitstream position of latches, flip-flops, LUTs, Block RAMs, and I/O block inputs and outputs. Bits are referenced by frame and bit number in the location file to help you observe the contents of FPGA registers.

- -bin\_file: (Optional) Creates a binary file (.bin) containing only device programming data, without the header information found in the standard bitstream file (.bit).

- reference\_bitfile <arg>: (Optional) Read a reference bitstream file, and output an incremental bitstream file containing only the differences from the specified reference file. This partial bitstream file can be used for incrementally programming an existing device with an updated design.

# Changing the Device Image (.pdi) File Format Settings

By default, the write\_device\_image Tcl command generates a (.pdi) file only. You can optionally change the file formats written out by the write\_device\_image Tcl command by using the following command switches:

- -force (Optional): Overwrite existing file.

- -verbose (Optional): Print write\_device\_image options.

- -raw\_partitions (Optional): Write raw CFI and NPI partition files (.rnpi and .rcdo)

- -mask\_file (Optional): Write a mask file (.msk)

- -logic\_location\_file (Optional): Write logic location file (.11)

- -cell <arg> (Optional): Create only partial device image for the named cell.

- -no\_pdi Do not generate a pdi file. Stop after generating raw partitions files only.

- -no\_partial\_pdifile (Optional): Do not write partial pdi files for a Dynamic Function eXchange design.

- -quiet (Optional): Ignore command errors.

- <file> (Required): The name of the .pdi file to write.

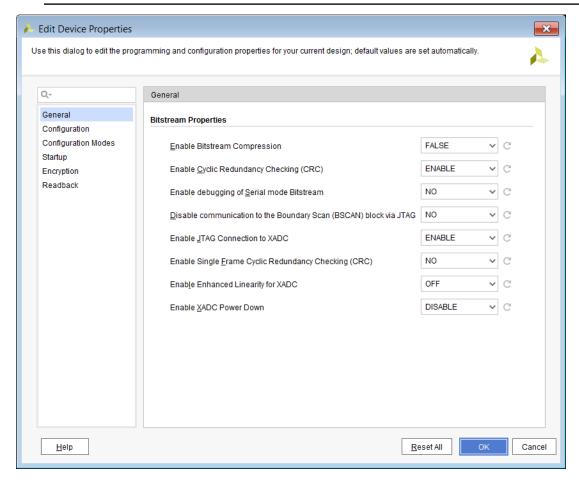

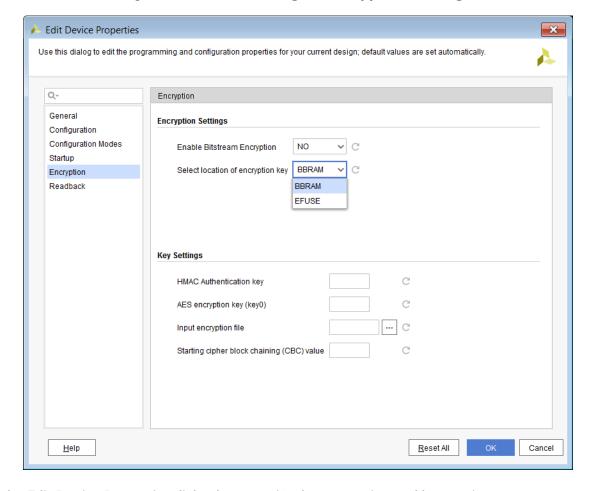

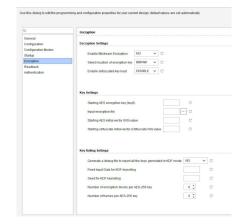

# Changing Device Configuration Bitstream Settings

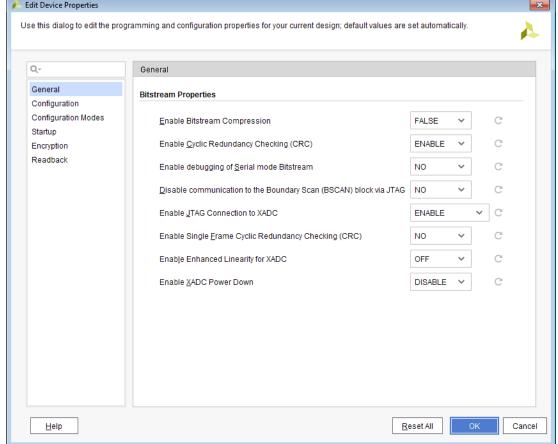

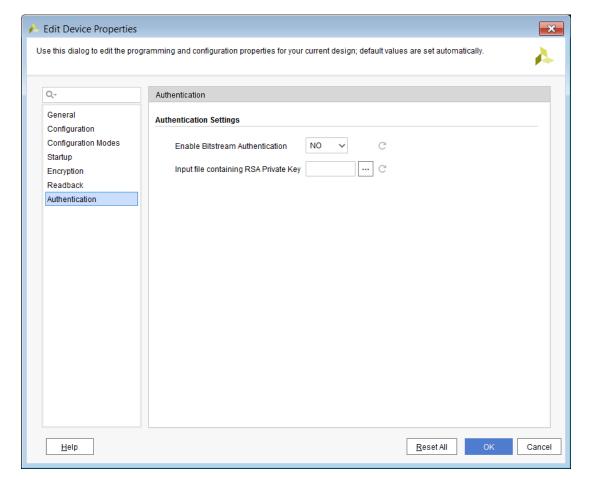

The most common configuration settings that you can change fall into the device configuration settings category. These settings are properties on the device model and you change them by using the Edit Device Properties dialog for the selected synthesized or implemented design netlist. The following steps describe how to set various bitstream properties using this method:

- 1. Select Tools → Edit Device Properties.

- 2. In the Edit Device Properties dialog, select one of the categories in the left-hand column (see the following figure).

**TIP:** You can type a property in the Search field. For example, type jtag into the Search text field to find and select properties related to JTAG programming.

- 3. Set the properties to the desired values, and click **OK**.

- 4. Select File → Constraints → Save to save the updated properties to the target XDC file.

You can also set the bitstream properties using the  $set_property$  command in an XDC file. For instance, here is an example on how to change the start-up DONE cycle property:

```

set_property BITSTREAM.STARTUP.DONE_CYCLE 4 [current_design]

```

Additional examples and templates are provided in the Vivado Templates. Device Configuration Bitstream Settings describes all of the device configuration settings.

**IMPORTANT!** Edit only the Device Configuration Bitstream Settings relevant to the configuration mode being used. Leave the other settings at their default values

#### **Related Information**

Device Configuration Bitstream or PDI Settings

# Programming the Device

The next step after generating the device image is to download it into the target device. Vivado IDE has native in-system device programming capabilities built in to do this.

Vivado Design Suite and Vivado Lab Edition includes functionality that allows you to connect to hardware containing one or more Xilinx® Device(s) to program and interact with those devices. Connecting to hardware can be done from either the Vivado Lab Edition, or Vivado Design Suite graphical user interface or by using Tcl commands. In either case, the steps to connect to hardware and program the target device are the same:

- 1. Open the Hardware Manager.

- 2. Open a hardware target that is managed by a hardware server running on a host computer.

- 3. Associate the device image with the appropriate device.

- 4. Program or download the device image into the hardware device.

#### **Opening the Hardware Manager**

Opening the Hardware Manager is the first step in programming and/or debugging your design in hardware. To open the Hardware Manager, do one of the following:

- If you have a project open, click the **Open Hardware Manager** button in the Program and Debug section of the Vivado flow navigator.

- Select Flow → Open Hardware Manager.

- In the Tcl Console window, run the open\_hw\_manager command

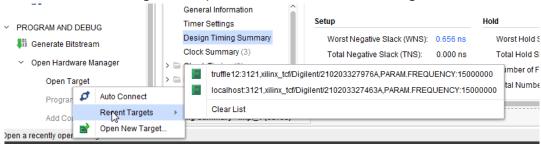

## **Opening Hardware Target Connections**

The next step in opening a hardware target (for instance, a hardware board containing a JTAG chain of one or more FPGAs or ACAPs) is connecting to the hardware server that is managing the connection to the hardware target. You can do this one of three ways:

• Use the **Open Target selection** under Hardware Manager in the Program and Debug section of the Vivado Flow Navigator to open new or recent hardware targets (see the following figure).

Use the Open Target → Recent targets or Open Target → Open New Target selection on the

green user assistance banner across the top of the Hardware Manager window to open recent

or new hardware targets, respectively (see the following figure).

Use Tcl commands to open a connection to a hardware target.

**TIP:** Use the Auto Connect selection to automatically connect to a local hardware target.

## Connecting to a Hardware Target Using hw\_server

The hw\_server is automatically started by Vivado when connecting to targets on the local machine. However, you can also start the hw\_server manually on either local or remote machines. For instance, in a full Vivado installation on a Windows platform, at a <code>cmd</code> prompt run the following command:

```

C:\Xilinx\Vivado\<Vivado_version>\bin\hw_server.bat

```

If you are using a Hardware Server (Standalone) installation on a Windows platform, at a cmd prompt run the following command:

```

c:\Xilinx\HWSRVR\<Vivado_version>\bin\hw_server.bat

```

Follow the steps in the next section to open a connection to a new hardware target using this agent.

For a list of compatable JTAG download cables and devices see Appendix D: JTAG Cables and Devices Supported by hw server.

For more information on using SmartLynq data cables, see the SmartLynq Data Cable User Guide (UG1258).

**IMPORTANT!** If Vivado Hardware Manager is connected to the hw\_server, and the hw\_server is stopped, the Hardware Manager detects this condition automatically and disconnects from the server.

#### **Opening a New Hardware Target**

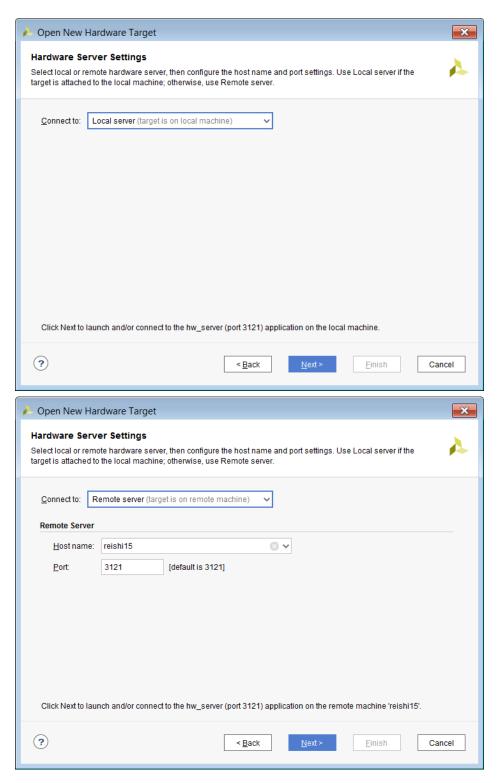

The Open New Hardware Target wizard provides an interactive way for you to connect to a hardware server and target. The wizard process has the following steps:

- 1. Select a local or remote server, depending on what machine your hardware target is connected to:

- Local server: Use this setting if your hardware target is connected to the same machine on which you are running the Vivado Lab Edition or Vivado IDE (See the following figure). The Vivado software automatically starts the Vivado hardware server (hw\_server) application on the local machine.

- Remote server: Use this setting if your hardware target is connected to a different machine

on which you are running the Vivado Lab Edition or Vivado IDE. Specify the host name or

IP address of the remote machine and the port number for the hardware server

(hw\_server) application that is running on that machine (see the following figures). Refer to

Connecting to a Remote hw\_server Running on a Lab Machine for more details on remote

debugging.

**IMPORTANT!** When using remote server, you need to manually start the Vivado hardware server  $(hw\_server)$  application of the same version of Vivado software that you will use to connect to the hardware server.

**TIP:** If you only want to connect to your lab machine remotely, you do not need to install the full Vivado design suite on that remote machine. Instead, you can install the light-weight Vivado Hardware Server (Standalone) tool on the remote machine.

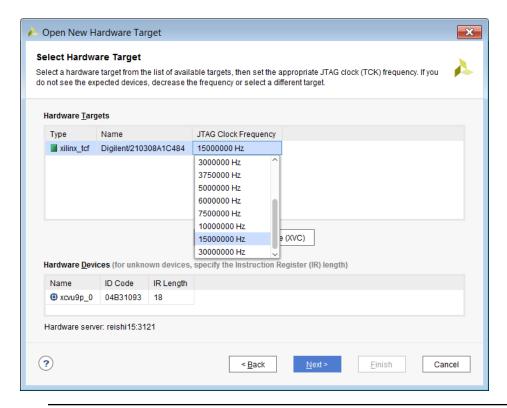

2. Select the appropriate hardware target from the list of targets that are managed by the hardware server. Note that when you select a target, you see the various hardware devices that are available on that hardware target.

**IMPORTANT!** If there are third party devices in the JTAG chain, use the instructions in Xilinx Answer Record 61312 to add IDCODE, IR Length, and name for the unknown devices.

#### **Related Information**

Connecting to a Remote hw\_server Running on a Lab Machine

## **Troubleshooting a Hardware Target**

You might run into issues when trying to connect to a hardware target. Here are some common issues and recommendations on how to resolve them:

• If you are not able to correctly identify the hardware devices on your target, it might mean that your hardware is not capable of running at the default target frequency. You can adjust the frequency of the TCK pin of the hardware target or cable (see the previous figure). Note that each type of hardware target may have different properties. Refer to the documentation of each hardware target for more information about these properties.

While the Vivado hardware server will attempt to automatically determine the instruction register (IR) length of all devices in the JTAG chain, in some rare circumstances it might not be able to correctly do so. You should check the IR length for each unknown device to make sure it is correct. If you need to specify the IR length, you can do so directly in the Hardware Devices table of the Open New Hardware Target wizard (see Opening a New Hardware Target).

#### **Related Information**

Opening a New Hardware Target

#### **Opening a Recent Hardware Target**

The Open New Hardware Target wizard is also what populates a list of previously connected hardware targets. Instead of connecting to a hardware target by going through the wizard, you can re-open a connection to a previously connected hardware target by selecting the Open recent target link in the Hardware Manager window and selecting one of the recently connected hardware server/target combinations in the list. You can also access this list of recently used targets through the Open Target selection under Hardware Manager in the Program and Debug section of the Vivado flow navigator.

#### **Opening a Hardware Target Using Tcl Commands**

You can also use Tcl commands to connect to a hardware server/target combination. For instance, to connect to the digilent\_plugin target (serial number 210203339395A) that is managed by the hw server running on localhost 3121, use the following Tcl commands:

```

connect_hw_server -url localhost:3121

current_hw_target [get_hw_targets */xilinx_tcf/Digilent/210203339395A]

set_property PARAM.FREQUENCY 15000000 [get_hw_targets \

*/xilinx_tcf/Digilent/210203339395A]

open_hw_target

```

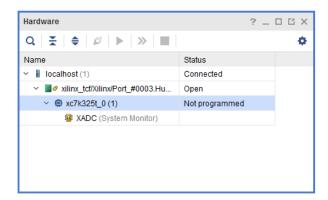

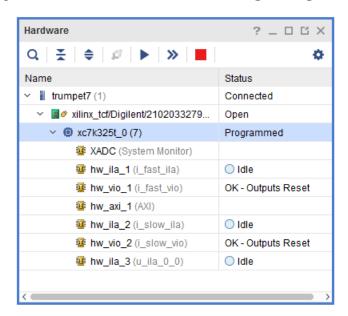

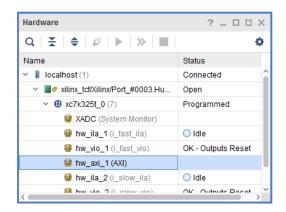

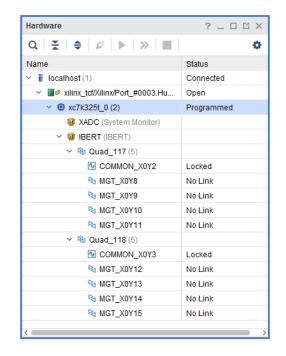

Once you finish opening a connection to a hardware target, the Hardware window is populated with the hardware server, hardware target, and various hardware devices for the open target (see the following figure).

Figure 7: Hardware View after Opening a Connection to the Hardware Target

# Associating a Programming File with the Hardware Device

After connecting to the hardware target and before you program the device, you need to associate the bitstream data programming file with the device. Select the hardware device in the Hardware window and make sure the Programming file property in the Properties window is set to the appropriate programming file.

**Note:** As a convenience, Vivado IDE automatically uses the programming file for the current implemented design as the value for the Programming File property of the first matching device in the open hardware target. This feature is only available when using the Vivado IDE in project mode. When using the Vivado IDE in non-project mode, you need to set this property manually.

You can also use the set\_property Tcl command to set the PROGRAM. FILE property of the hardware device:

```

set_property PROGRAM.FILE {C:/<path_to_programming_file>} [lindex

[get_hw_devices] 0]

```

# **Programming the Hardware Device**

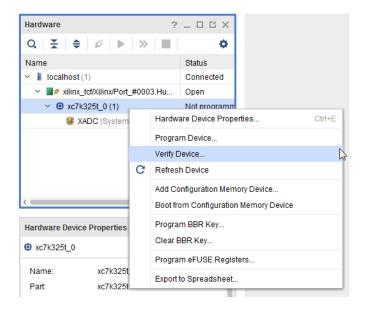

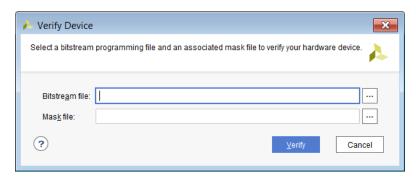

Once the programming file has been associated with the hardware device, you can program the hardware device using by right-clicking on the device in the Hardware window and selecting the Program Device menu option. You can also use the program\_hw\_device Tcl command. For instance, to program the first device in the JTAG chain, use the following Tcl command:

```

program_hw_devices [lindex [get_hw_devices] 0]

```

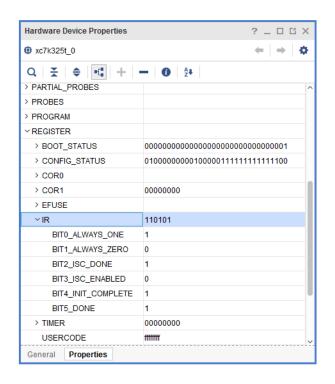

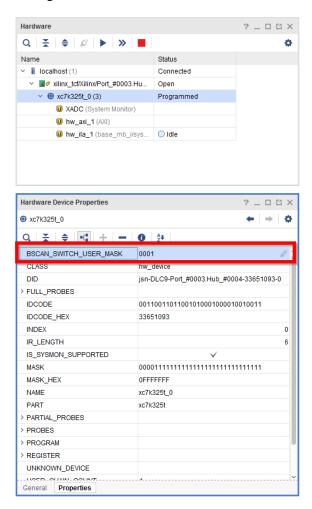

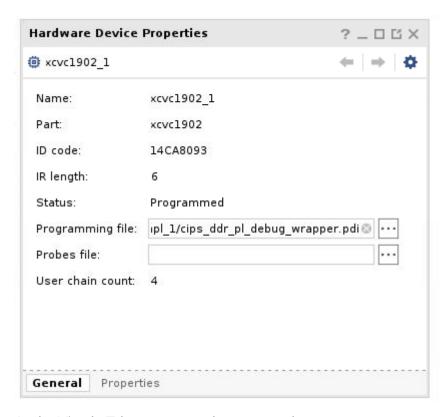

Once the progress dialog has indicated that the programming is 100% complete, you can check that the hardware device has been programmed successfully by examining the DONE status in the Hardware Device Properties view.

Figure 8: Checking the DONE Status of a Device

You can also use the  $get_property$  Tcl command to check the DONE status. For instance, to check the DONE status of a Kintex®-7 device that is the first device in the JTAG chain, use the following Tcl command:

```

get_property REGISTER.IR.BIT5_DONE [lindex [get_hw_devices] 0]

```

On Versal devices, the command differs slightly because the DONE status register is different. Index 1 must be read as the first device returned by  $get_hw_devices$ , and will be the  $arm_dap$  in a single device use case.

```

get_property REGISTER.JTAG_STATUS.BIT[34]_DONE [lindex [get_hw_devices] 1]

```

If you use another means to program the hardware device (for instance, a flash device or external device programmer), you can also refresh the status of a hardware device by right-clicking the Refresh Device menu option or by running the  $refresh_hw_device$  Tcl command. This refreshes the various properties for the device, including but not limited to the DONE status.

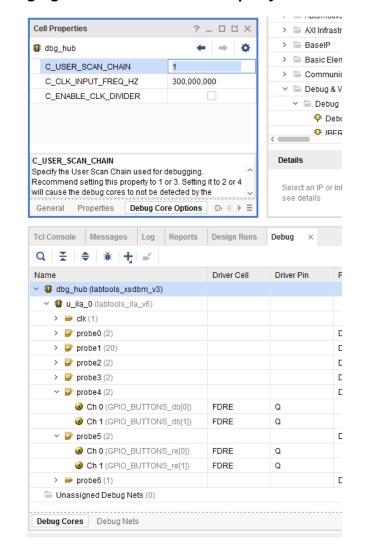

**IMPORTANT!** For non-Versal architectures, if your design contains debug cores, ensure that the JTAG clock is 2.5 times slower than the debug hub clock.

**IMPORTANT!** User SCAN Chain: For non-Versal architectures, Vivado Programmer tries to detect debug cores on the user scan chain specified in the design by default. It does the detection by issuing a JTAG\_CHAIN 1 command to the device. If you have programmed a device with a design that does not have any debug cores or a debug core with a user scan chain of 2, 3, or 4, you will see a warning.

To determine the user scan chain setting, for non-Versal architectures, open the implemented design and use:

```

get_property C_USER_SCAN_CHAIN [get_debug_cores dbg_hub]

```

You can change the user scan chain used in the Vivado Hardware Manager. Note that the BSCAN\_SWITCH\_USER\_MASK is a bit mask value. See the following figure.

Alternatively you can specify the user scan chain value as an option to hw\_server start-up.

hw\_server -e "set bscan-switch-user-mask <user-bit-mask>"

Figure 9: BSCAN Switch User Mask

**TIP:** For designs prior to Vivado 2016.3 Xilinx recommends manually launching  $hw_server$  with -  $e"set xsdb-user-bscan < C_USER_SCAN_CHAIN scan_chain_number>" to detect the debug hub at User Scan Chain of 2 or 4.$

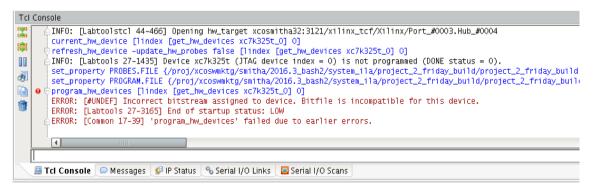

### **Incorrect Bitstream Assignment Message**

Vivado Hardware Manager generates an incorrect bitstream assignment message when:

Attempting to program an image with a bitstream or programmable device image generated for a different FPGA or ACAP.

For example, the following error message appears when trying to program an XCKU115 with an XCVU190 bitstream.

Figure 10: Programming an XCKU115 with an XCVU190 Bitstream

The solution is to specify the correct bitstream for the FPGA or ACAP being programmed.

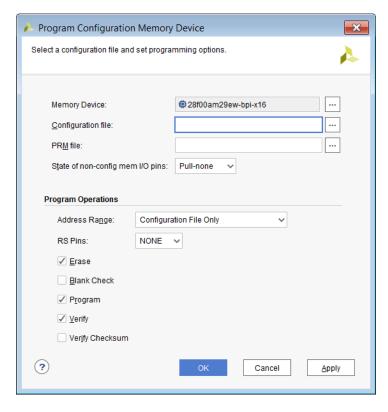

# Attempting to Program Configuration Memory Attached to an FPGA Device

To program configuration memory attached to an FPGA device, Vivado Hardware Manager first downloads a flash controller bitstream to the FPGA device. Hardware Manager then sends flash commands and data through the FPGA device's JTAG port to be processed by the controller, which then sends the processed flash commands/data to the configuration memory interface.

The controller bitstream downloaded by Hardware Manager is generated for the latest silicon revision of the FPGA device. For example, the configuration memory controller bitstream for the XCKU115 in 2016.3 and later was generated for XCKU115-es2 silicon.

When programming configuration memory attached to this FPGA, if the user has an XCKU115-es1 device on the board, the error message shown in Attempting to Program an FPGA Device with a Bitstream Generated for a Different Silicon Revision of the FPGA appears. This is because Hardware Manager is attempting to download the -es2 flash controller bitstream into the -es1 device.

# **Closing the Hardware Target**

You can close a hardware target by right-clicking on the hardware target in the **Hardware** window and selecting **Close Target** from the popup menu. You can also close the hardware target using a Tcl command. For instance, to close the xilinx\_platformusb/USB21 target on the localhost server, use the following Tcl command:

close\_hw\_target {localhost/xilinx\_tcf/Digilent/210203339395A}

**IMPORTANT!** If the board is powered off or cable disconnected, Vivado IDE closes the hardware target in the Hardware Manager. Any Vivado operation in the main Vivado thread is also canceled. If the board is powered back on or the cable is reconnected, the Vivado IDE will attempt to re-open the hardware target in the Hardware Manager.

# Closing a Connection to the Hardware Server

You can close a hardware server by right-clicking on the hardware server in the **Hardware** window and selecting **Close Server** from the popup menu. You can also close the hardware server using a Tcl command. For instance, to close the connection to the localhost server, use the following Tcl command:

disconnect\_hw\_server localhost

**IMPORTANT!** If Vivado Hardware Manager is connected to the hw\_server, and the hw\_server is stopped, the Hardware Manager detects this condition automatically and disconnects from the server.

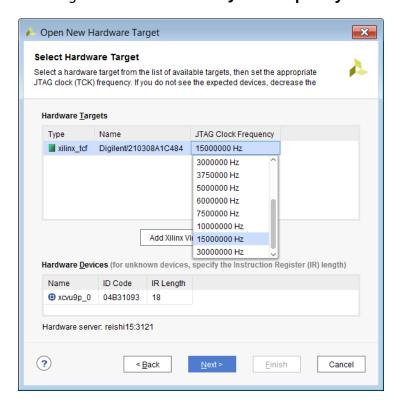

# Reconnecting to a Target Device with a Lower JTAG Clock Frequency

The JTAG chain is as fast as the slowest device in the chain. Therefore, to lower the JTAG clock frequency, connect to a target device whose JTAG clock frequency is less than the default JTAG clock frequency.

You should attempt to open with a default JTAG clock frequency that is 15 MHz for the Digilent cable connection and 6 MHz for the USB cable connection. If it is not possible to connect at these speeds, Xilinx recommends that you lower the default JTAG clock frequency even further as described below.

To change the JTAG clock frequency, use the Open New Hardware Target wizard, from Vivado<sup>®</sup> Design Suite, as shown in the following figure.

Figure 11: Vivado Lower JTAG Frequency

Alternately, you can use the following sequence of Tcl commands:

```

open_hw_manager

connect_hw_server -url machinename:3121

current_hw_target [get_hw_targets */xilinx_tcf/Digilent/210203327962A]

set_property PARAM.FREQUENCY 250000 [get_hw_targets */xilinx_tcf/Digilent/210203327962A]

open_hw_target

```

# Connecting to a Server with More Than 32 Devices in a JTAG Chain

It is possible to connect to a server which has more than 32 devices in its JTAG chain in Vivado. You need to provide option  $\max - j tag - devices$  at the startup of hw\_server to enable the ability to detect more devices in a scan chain. The default value for this setting is 32. Note that increasing this number will slow down the device discovery process which in turn can slow down cable access.

Specify the max-jtag-devices option at hw\_server start-up as follows:

```

hw_server -e "set max-jtag-devices 64"

```

### **Usage**

This option is used to start up the hw\_server with the ability to enable ir lengths greater than 64 bits. The default value for this setting is 64. You can increase this value for devices in the JTAG chains whose ir length are wider (for example 93). Note that increasing this number will slow the device discovery process, which in turn can slow cable access. Therefore, you should only increase this value for systems with long ir lengths and device counts.

This is how you specify the option at hw\_server start-up:

```

hw_server -e "set max-ir-length 93"

```

### **Init Option**

You may also use the --init=script.txt option to load this setting through a file. To use the init option, create a initialization script as shown in the following example. In the script, specify the set max-jtag-device parameter.

```

# Sample script.txt

set max-ir-length 93

```

Start the hw\_server as shown in the following example:

```

hw_server --init=script.txt

```

# **Changing the Default SmartLynq Ports**

By default, the SmartLynq module uses the following ports. In some cases, you might want to change the port used. To update the port used, add the commands to the SmartLynq config.ini file and update using the procedure documented in the SmartLynq Data Cable User Guide (UG1258).

**Table 1: Changing SmartLynq Default Ports**

| Default Port | Description                                              | Add to config.ini to change                                                                          |

|--------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 80           | TCF over HTTP                                            | set http-port <port></port>                                                                          |

| 3121         | TCF                                                      | set tcf-port <port></port>                                                                           |

| 10200        | Low level JTAG access over XVC                           | set xvc-port <port></port>                                                                           |

| 3000-3003    | GNU Debugger ports (for Arm®/<br>MicroBlaze™ processors) | set gdb-port <base port=""/> Setting the base port sets the lowest port for the range of four ports. |

# Remote Debugging in Vivado

The need for remote debugging may arise in a variety of situations. It could be required in the prototyping phase of a product, where you might want to debug a design in the lab without physical access to the lab, or where you might want to share resources across your organization. Remote debugging could also be required to perform in-the-field debug to diagnose issues or extend product life cycle.

Xilinx® provides multiple solutions to debug your design remotely. This can be done using the Xilinx Hardware Server product to connect to a remote computer in the lab. You could also implement the Xilinx Virtual Cable (XVC) protocol to connect to a network-connected board. Each of these solutions are explained in detail in the sections below.

## Using Vivado Hardware Server to Debug Over Ethernet

You can connect to a remote lab machine using Vivado Hardware Server product. This is a small sized (<100 MB) standalone download available for install on the lab machine. This option requires intranet or internet access and can be used internally just within your organization as well.

Desk

Lab

Figure 12: Debug via Internet/Intranet Using Hardware Server

X14/41-062315

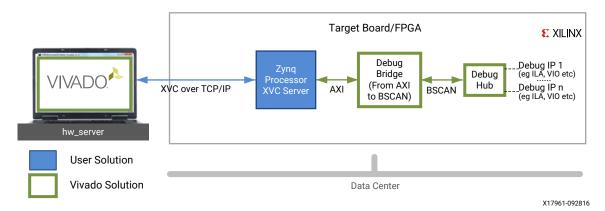

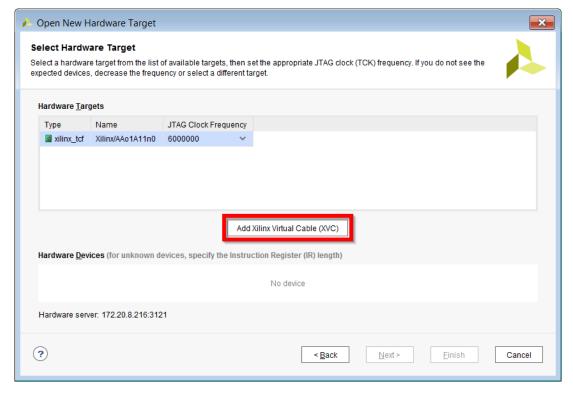

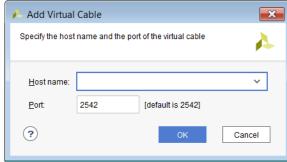

# Xilinx Virtual Cable (XVC)

Vivado IDE supports the Xilinx Virtual Cable (XVC) protocol. Xilinx Virtual Cable lets you access and debug a Xilinx device without using USB or parallel configuration cable. This capability helps facilitate Vivado IDE to debug for designs that:

- Have the FPGA in a hard-to-access location, where a "lab-PC" is not convenient.

- Do not have direct access to the device pins on the board for example, if the JTAG pins are only accessible with a local microprocessor interface.

XVC is an internet-based (TCP/IP) protocol that acts like a JTAG cable. It has very basic cable commands. This allows XVC to debug a system over an intranet, or even the internet. With this capability you can save on costly or impractical travel and reduce the time it takes to debug a remote system.

Another common use of XVC is for shared systems that are not co-located with teams that need access to them. It can also be used when there are physical constraints to using the system, such as when the JTAG connector is not available or accessible. XVC implementation is programming language and platform independent.

Rather than using a dedicated JTAG header, an existing Ethernet connection can be used to create the appropriate JTAG commands from a processor to a target device. With the XVC v1.0 Protocol, Vivado can communicate the same JTAG commands over an Ethernet connection and still support all of the existing Vivado debug features.

**IMPORTANT!** If the Vivado Debug Bridge IP is used for XVC, Vivado IDE does not support programming features. The assumption is that the device is programmed before using XVC to debug the design. The Debug Bridge IP is not compatible with Versal ACAP.

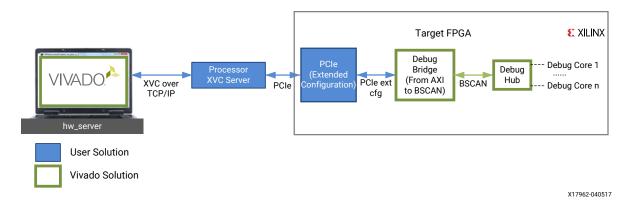

# Vivado Debug Bridge IP and Xilinx Virtual Cable (XVC) Flow

Note: Vivado Debug Bridge IP is not supported on Versal® devices.

The Vivado Debug Bridge IP core is a controller that provides multiple options to communicate with the debug cores in the design. This design can be a flat design or a Dynamic Function eXchange design. In addition, the Debug Bridge IP core can also be configured to take advantage of debugging designs using a JTAG cable or remotely through Ethernet, PCle<sup>®</sup>, or other interfaces without the need for a JTAG cable.

Different modes in Debug Bridge IP facilitate the support of various use cases.

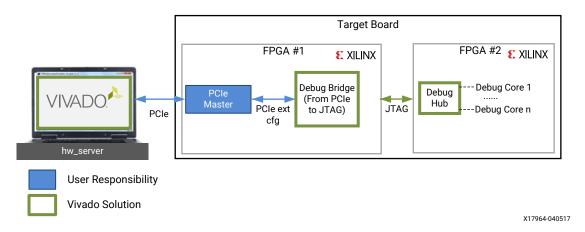

#### Debug Bridge in XVC Modes

There are five modes in the Debug Bridge that are used in Xilinx Virtual Cable (XVC) implementations.

- From AXI to BSCAN: In this mode, the Debug Bridge receives XVC Commands via AXI4-Lite slave interface.

- From JTAG to BSCAN: In this mode, the Debug Bridge receives XVC Commands via JTAG slave interface driven by user logic.

- From PCle to BSCAN: In this mode, the Debug Bridge receives XVC Commands via PCle Extended Configuration slave interface.

- From PCle to JTAG: In this mode, the Debug Bridge receives XVC Commands via PCle Extended Configuration interface. This Debug Bridge brings out the JTAG pins out of the FPGA through I/O pins. This mode is mainly used to debug design on another board over XVC.

- From AXI to JTAG: In this mode, the Debug Bridge receives XVC commands via AXI4-Lite interface to send over the JTAG pins to a target device.

In all of these modes the Debug Bridge can further communicate with other debug cores/ Debug Bridge instances in the design via the Soft-BSCAN (Boundary Scan) interface. The Soft BSCAN master interface enables extension of the JTAG interface to internal USER defined scan chains/ Debug Bridge instances.

#### Using Debug Bridge IP in Dynamic Function eXchange Designs

The Debug Bridge IP can be used in both flat and Dynamic Function eXchange designs. Below are the details on the Debug Bridge configurations used in the static or Reconfigurable Partition (RP) region of a Dynamic Function eXchange design. Multiple Debug Bridge instances are permitted in a partition depending on the design requirements.

- **BSCAN Primitive:** This mode is used when a Debug Bridge containing a BSCAN primitive is required in the static region. The BSCAN master interface of this Debug Bridge can be connected to another Debug Bridge instance in the static and/or RP region(s) providing one or more communication pathways for debugging those regions.

- From BSCAN to Debug Hub: In this mode, the Debug Bridge uses the BSCAN slave interface to communicate to Vivado Hardware Manager. It uses the Debug Hub interface to communicate with the design cores within the relevant static or RP region. You can also optionally add additional BSCAN Masters to the output of this Debug Bridge, which enables debugging other debug cores like MicroBlaze™ Debug Module (MDM) or other Debug Bridge instances.

**Note:** The tool automatically connects the debug cores in an RP to the Debug Bridge if this is the only Debug Bridge instantiated in the partition.

- From AXI to BSCAN: In this mode, the Debug Bridge receives XVC Commands via AXI4-Lite slave interface. This Debug Bridge can further communicate with other debug cores/ Debug Bridge instances in the design via the Soft-BSCAN (Boundary Scan) master interface. The Soft BSCAN interface enables extension of the JTAG interface to internal USER defined scan chains/Debug Bridge instances.

- From JTAG to BSCAN: In this mode, the Debug Bridge receives XVC Commands via JTAG slave interface driven by user logic. This Debug Bridge can further communicate with other debug cores/ Debug Bridge instances in the design via the Soft-BSCAN (Boundary Scan) master interface. The Soft BSCAN interface enables extension of the JTAG interface to internal USER defined scan chains/Debug Bridge instances.

- From PCle to BSCAN: In this mode, the Debug Bridge receives XVC Commands via PCle

Extended Configuration slave interface. This Debug Bridge can further communicate with

other debug cores/ Debug Bridge instances in the design via the Soft-BSCAN (Boundary Scan)

interface. The Soft BSCAN master interface enables extension of the JTAG interface to

internal USER defined scan chains/Debug Bridge instances.

Note: This mode is only available for UltraScale+ and UltraScale device architectures

• From PCle to JTAG: In this mode, the Debug Bridge receives XVC Commands via PCle Extended Configuration interface. This Debug Bridge brings out the JTAG pins out of the FPGA through I/O pins. This mode is mainly used to debug design on another board over XVC.

Note: This mode is only available for UltraScale+ and UltraScale device architectures.

• From AXI to JTAG: In this mode, the Debug Bridge receives XVC commands via AXI4-Lite interface to send over the JTAG pins to a target device.

#### JTAG Fallback Support

The XVC based debug solution can be used with AXI masters such as the PCle® XDMA IP. If the AXI master is in a hang situation or is otherwise not functioning properly, there are no methods to debug those scenarios. To provide a JTAG-based fall back debug pathway that is parallel to the XVC pathway, Xilinx® recommends using the Debug Bridge in BSCAN Primitive mode. A Debug Bridge in BSCAN Primitive mode can be instantiated in static region and its BSCAN master interface can be connected to the BSCAN slave interface of a second Debug Bridge that is configured with the JTAG Fallback Support enabled. There are two JTAG Fallback Support types:

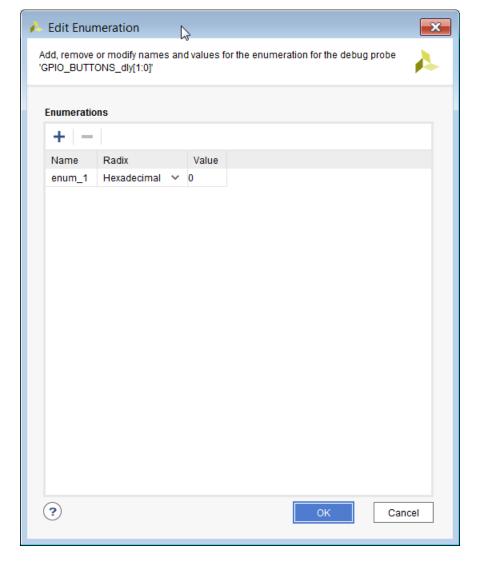

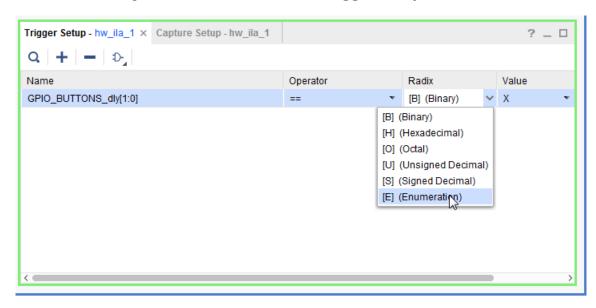

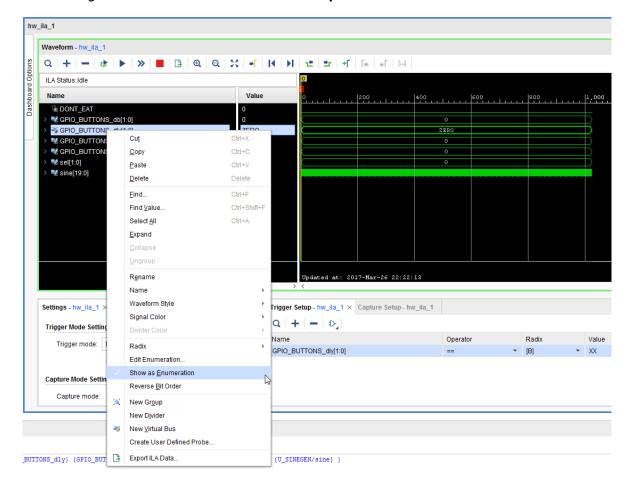

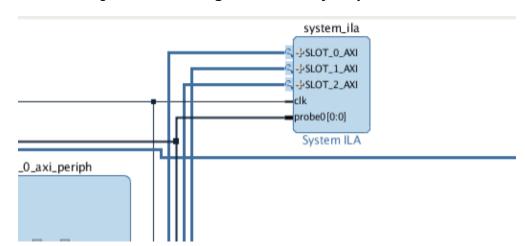

- 1. If the Debug Bridge that you want to provide JTAG Fallback for resides in a RP region, you need to enable the External BSCAN Master JTAG Fallback Support.