Faster Design Iterations

Overview

Design iterations are common as devlopers add new features and debug their design. In many cases these iterations are incremental changes and in most cases the changes are within a small portion of the design. The Vivado ML Edition offers two key technologies that significantly reduce design iteration times: Incremental compile and Abstract Shell.

Incremental Compile

In the fast-evolving world of FPGA design, when large and complex designs are built, achieving speed in design iterations is paramount. It’s common to make iterative changes to the design source code, constraints, and settings. In a traditional flow, making these changes would necessitate a complete recompilation of the entire design, which can be time-consuming and resource intensive.

Vivado Incremental Compile addresses this challenge by intelligently identifying and recompiling only the portions of the design that have been modified, rather than full compile. This approach slashes compilation time as small design changes are made and helps designers iterate their designs faster - allowing engineers to swiftly validate their design changes.

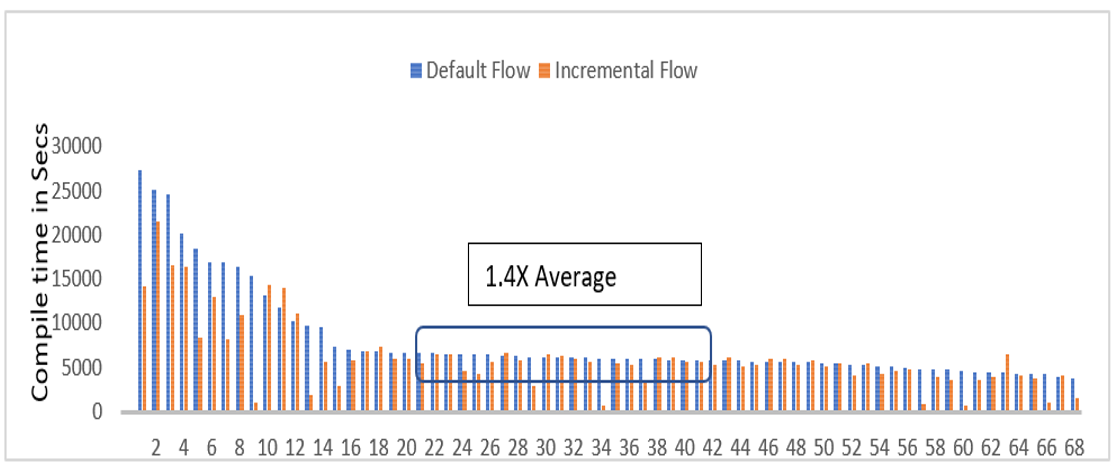

The benchmark data below shows the compile times for the default compile in Blue and the incremental flow in red for 68 designs in 2022.2 version of the Vivado ML Edition. The benchmark shows an average 1.4x faster recompile times with Incremental Compile.

Incremental Compile Benchmark Results for UltraScale+ Device Designs Using 2022.2

Footnote: Measurements are done by Vivado™ engineering team as of October 2022, on 68 designs comparing Default vs. Incremental compile on Vivado ML software tool 2022.2. Six outlier compares in excess of 6x were discarded to provide a more representative performance average. 5% of design incrementally compiled for comparison. Actual improvement uplift for commercial systems may vary based on factors including system hardware, software and driver versions, and BIOS settings.

In Summary, Vivado Incremental Compile is a feature within the Vivado Design Suite that allows FPGA designers to work more effectively, enabling faster turnaround times for design changes and accelerating the development of FPGAs.

Abstract Shell

Abstract Shell introduces a cutting-edge approach to achieve rapid compilation times for large and complex designs. It offers a way to create a trimmed down version of a portion of the design, while providing context for the rest of the design. By isolating specific regions of the design, Abstract Shell allows engineers to implement and validate modules independently, without the need for full design recompilation. Abstract Shell allows designers to mark off the portion of the design that is changing and the portion of the design that is not touched.

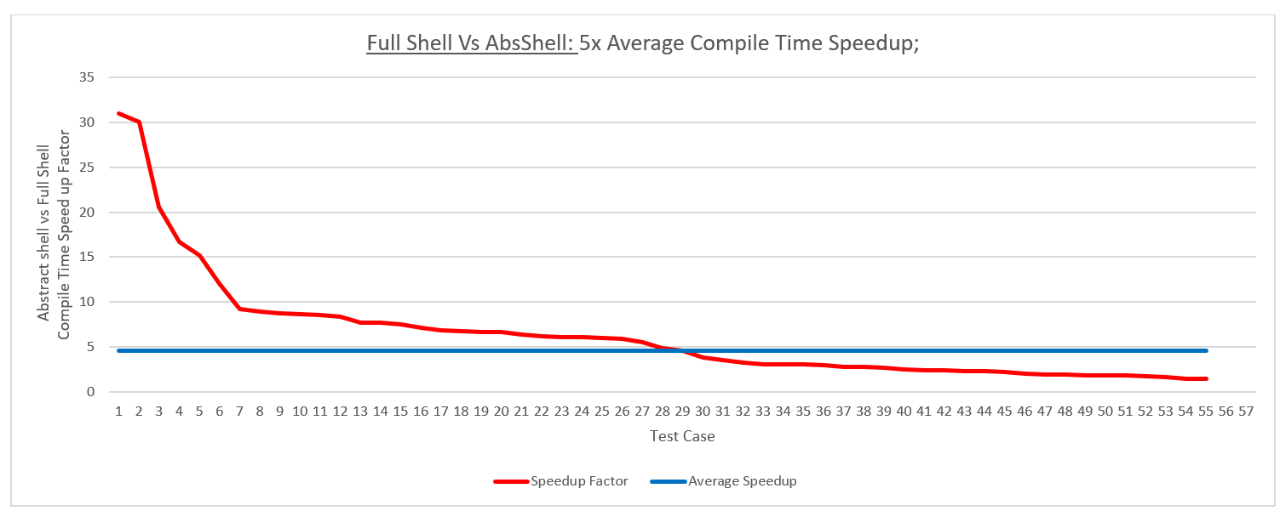

The benchmark data below shows an average of 5x compile times speedup of Abstract shell vs Full shell. The Red line shows the compile time speedup of Abstract shell runs over the Full shell runs. The Blue bar shows the 5x average compile time speed up over 55 test cases.

Abstract Shell Benefits Benchmark Results for UltraScale+ Device Designs Using 2021.1

Footnote: Measurements are done by Vivado™ engineering team as of June 2021, on 55 designs comparing Default vs. Abstract Shell compile on Vivado ML software tool 2021.1. Actual improvement uplift for commercial systems may vary based on factors including system hardware, software and driver versions, and BIOS settings.

In summary, Abstract Shell revolutionizes FPGA design by offering a fast, efficient, and modular approach that transforms the way designers create, modify, debug, and optimize the FPGA designs.

Resources

Access Documentation and Blogs