Vitis Model Composer

AMD Vitis™ Model Composer is a model-based design tool that enables rapid design exploration within the MathWorks MATLAB® and Simulink® environment. It can be purchased as an add-on license to Vivado™ ML Standard or Enterprise Editions and the Vitis development environment.

Overview

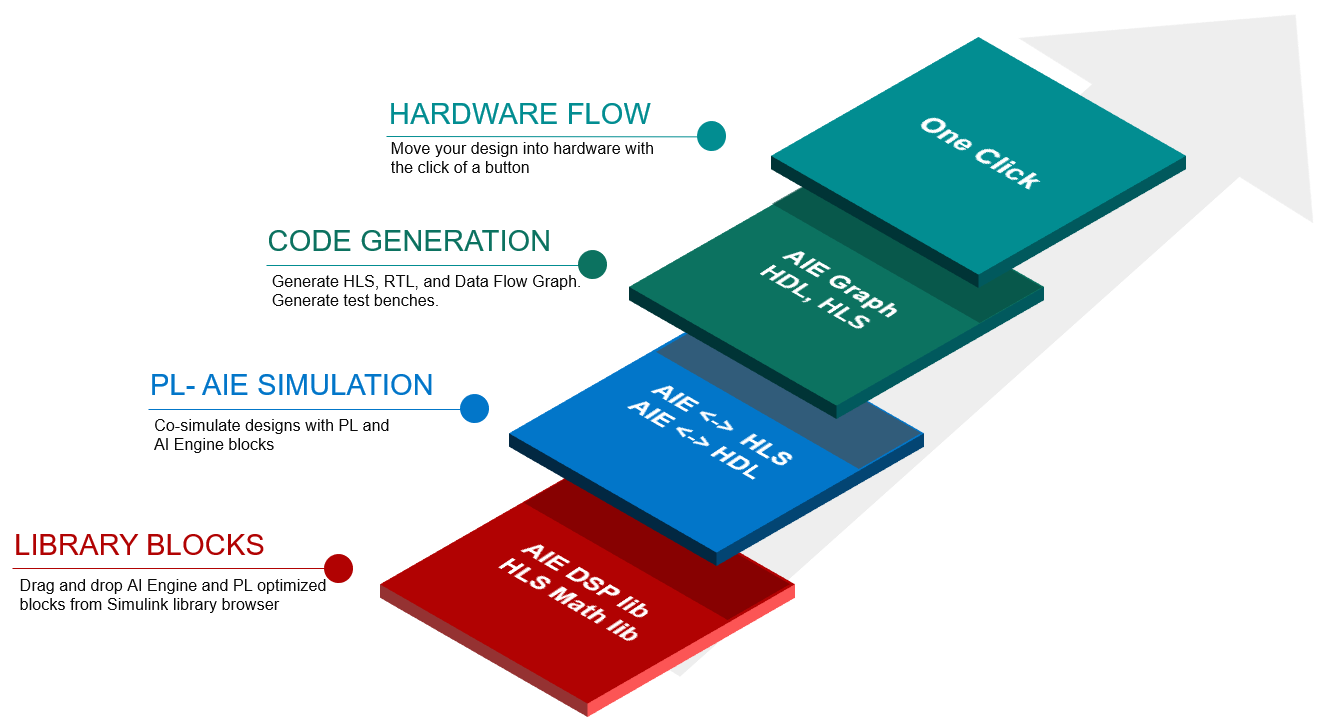

Vitis Model Composer Overview

Vitis™ Model Composer is a model-based design tool that enables rapid design exploration within the MathWorks MATLAB® and Simulink® environment and accelerates the path to production on AMD devices through automatic code generation.

You can design your DSP algorithms and iterate through them using high-level, performance-optimized blocks and validate functional correctness through system-level simulations. Vitis Model Composer transforms your design into a production-quality implementation through automatic optimizations.

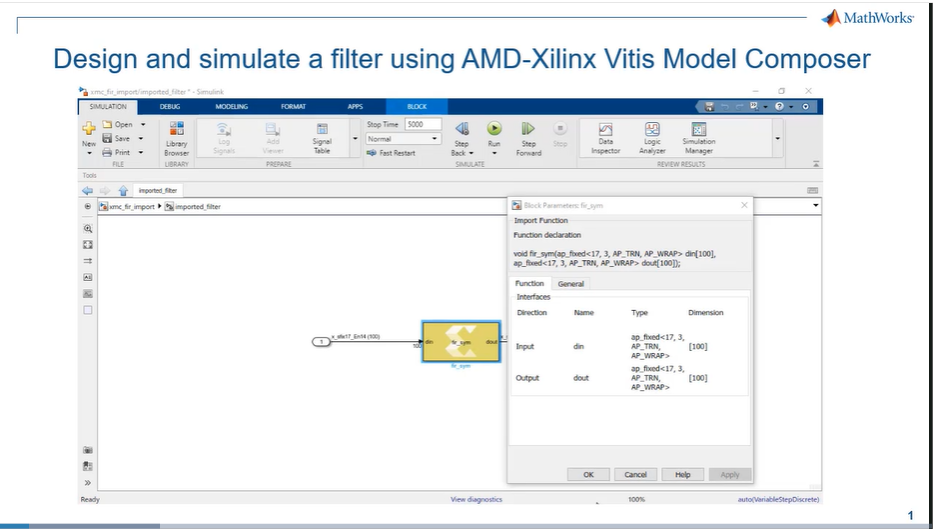

The tool provides a library of more than 200 HDL, HLS, and AI Engine blocks for the design and implementation of algorithms on AMD devices. It also enables importing custom HDL, HLS, and AI Engine code as blocks into the tool.

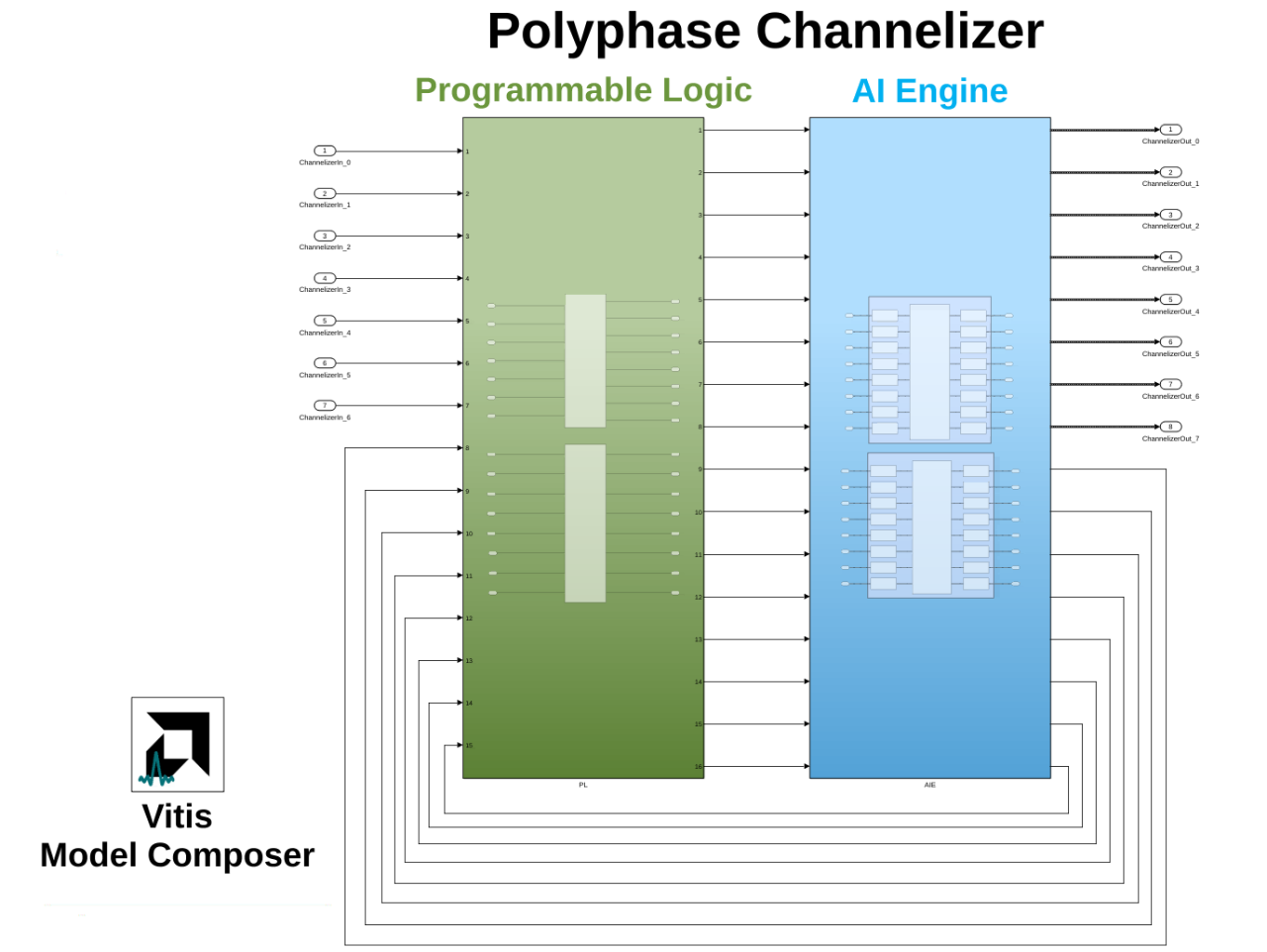

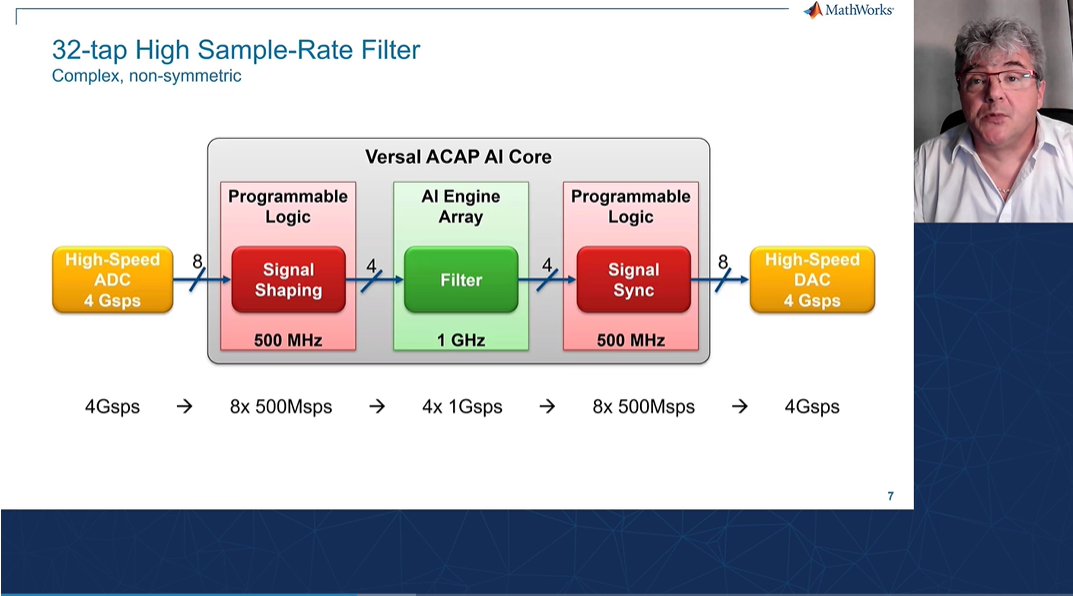

Vitis Model Composer offers a way to design the Versal™ adaptive SoCs. The tool can help designers create complex systems targeting both the PL and the AI Engine array. Learn how to use Versal AI Engines with Vitis Model Composer.

Vitis Model Composer includes all the functionality of AMD System Generator for DSP, which is no longer shipped as a standalone tool since 2021.1.

Designing Versal AI Engines

Learn how to develop Versal AI Engines

Using Vitis Model Composer

Visit the new webpage >

Vitis Model Composer Features

Here's a quick overview of Vitis™ Model Composer features. Click the other tabs for complete details.

Analysis, Debugging & Visualization

Use the MATLAB and Simulink environment to analyze and visualize your design:

- Use optimized AI Engine, HLS, and HDL blocks directly from the Simulink library browser

- Import custom AI Engines, HLS, and HDL code as blocks

- Run fast simulations in the Simulink environment

- Compare the results with golden references in the MATLAB and Simulink environment

- Tap into intermediate signals to debug and get visibility into the design

Co-Simulation of AI Engines and Adaptable Engines

Co-simulate a heterogeneous system:

- Directly use optimized AI Engines/HLS/Adaptable Engines from the library browser or import code as blocks

- Seamlessly connect AI Engine arrays with HLS kernel blocks or HDL blocks

Code Generation

Increase productivity by generating code from your design:

- Generate graph code along with constraints

- Generate RTL (Verilog/VHDL)

- Generate optimized HLS code with inserted pragmas

- Generate a test bench

Validation of Design in Hardware

Easily validate your design in hardware:

- Generate data movers, processing system code, config files

- Generate the make files to build the design for hardware

- Move the design into hardware with a click of a button

What's New

2023.2 Release Highlights

AI Engine block updates

- Support for importing AIE-ML graphs as blocks into Vitis Model Composer

- New DSPlib functions for AIE and AIE-ML implementation in Vitis Model Composer

- Plotting of AIE simulator output for internal signals in the Simulink® tool

HLS Kernel block updates

- Automatic test bench generation

- Expanded data type support for HLS Kernel blocks

Integration of Vitis Model Composer and Vitis tool

- Generation of .xo and libadf.a files directly from Vitis Model Composer

Other enhancements

- MATLAB® tool version support : R2021a, R2021b Update 6, R2022a Update 6, R2022b

- Additional topologies supported for the hardware validation flow

- New example collaterals available from GitHub

2023.1 Key Features and Enhancements

AI Engine

- Significant improvement in the responsiveness of AI Engine DSP blocks

- Support for importing AI Engine graphs with the non-default constructor.

HLS

- HLS Kernel block is now supported on the Windows platform.

- In HLS Kernel block, users can designate an input argument as an input parameter or an input port.

- HLS Kernel block now supports new data types including hls::stream<ap_int<BITS> >, hls::stream<ap_uint<BITS> >, ap_uint<BITS>, ap_int<BITS>.

HDL

- New Floating point DSPFP32 block to support Versal devices. This block comes with fast simulation capability.

- Added new Vector FFT floating point block optimized for Versal devices

- Gateway-In AXIS block now supports broader output data types (similar to Gateway-In block).

General

- Improvement to the Hub block:

- Added option to configure the number of AI Engine parallel builds.

- Added the mechanism to display the list of invalid blocks in a Subsystem.

- Added field to provide AI Engine Simulator options.

- Support for MATLAB tool version R2021a, R2021b, R2022a

2022.2 Features and Enhancements

In 2022.2, Vitis Model Composer includes many new feature additions and enhancements.

Features For Versal AI Engine Design

- You can now add graph constraints to AI Engine DSP blocks – better implementation control for performance/utilization

- After running the cycle approximate AI Engine simulation, the tool shows the throughput for part of the output data bounded by the cursers in the Simulink Data Inspector

- Ease of use enhancements to the AI Engine Graph Import block:

- Use of *.cpp to import a graph is now deprecated

- The tool automatically detects RTP ports and the user no longer needs to specify the RTP ports manually

- Enhancements to DSP Library Blocks

- Added new Stream-based Dynamic Point FFT block

- Added new Window and Stream-based Window Function blocks

- Super sample rate (SSR> 1) supported on all stream-based FIR blocks

- Decimate Polyphase (TP_PARA_DECI_POLY) parameter added to Halfband Decimator block

- Interpolate Polyphase (TP_PARA_INTERP_POLY) parameter added to Halfband Interpolate block

- Upshift center tap parameter added for FIR Halfband interpolator window and stream blocks

- Added buffer_1d support as Early Access

- sync, async, cyclic buffer_1d are supported.

- Specifying size through GUI or kernel code supported

- Margin can be specified through kernel code

HLS

- Enhancement to HLS Kernel block to support extended templatized parameters

- Enhanced Window Processing Block to target URAM resource

HDL

- Major improvements to the Blackbox RTL import flow in to Vitis Model Composer

- Extended support for Input Port Data types of SIGNED, UNSIGNED, BOOLEAN, FLOAT32 and FLOAT64

- Added support for Input Port Data types of UFIXED, SFIXED with some manual intervention requires in case of having binary point position greater than 0

- Added support to bring arrays of Integers or Float values using generic parameter

- Added new API called addDirectory() to bring multiple HDL files

- Updated the Questa third Party Simulator block GUI to provide the precompiled unisim library

General

- Major overhaul to the Vitis Model Composer Hub block

- Major user interface upgrade to support Heterogenous designs.

- Automatic detection of valid AI Engine, HDL, and HLS subsystems

- System Generator token is now deprecated, and existing System Generator designs can be automatically upgraded to use the new Hub block

- Hardware validation flow is enhanced to also support HDL only designs and HDL → AI Engine → HDL designs for Versal platforms

- MATLAB Support - R2021a and R2021b

- Right click options on canvas as well as blocks such as AMD BlockAdd, BlockConnect, and AMD Tools have been removed

- Improved patch usage mechanism

In 2022.1, Vitis Model Composer includes many new feature additions and enhancements.

For more details, see below:

- AI Engines

- Over 50% reduction in compilation time during Simulink simulation for AI Engine DSP blocks.

- Enabled streaming support for DSP library blocks.

- Added the Following Blocks to DSP Library:

- Stream FFT and IFFT

- Stream DDS and Mixer

- Dynamic Point FFT

- FIR Resampler

- Stream based FIR counter parts for all existing window FIR blocks (Decimators, Filters and Interpolators)

- PLIO and FIFO blocks are now two separate blocks and the AIE Signal Spec block is deprecated.

- You can now specify PLIO and FIFO constraints in the constraint manager.

- AI Engine import blocks can now be masked as part of a bigger subsystem and their parameters can use the parameter values from the mask.

- Constraint manager variables can now use the mask parameters from the subsystem mask that contains the AI Engine blocks.

- HLS

- HLS Kernel import block now supports template functions.

- Ease of use enhancement to HLS Kernel block.

- HDL

- Black-box import with Vivado simulator flow is now updated to support VHDL2008 for Simulation and Code Generation by default.

- New Gateway-in AXI Stream and Gateway-out AXI Stream utility blocks to facilitate connectivity between AI Engine and HDL domains.

- Vitis Model Composer no longer depends on Qt libraries. This will bring a consistent look and feel to the block GUIs and improve the stability of the tool while keeping functionality the same. As a result of this update, block GUIs come up faster than Qt-based block GUIs.

- HDL blocks now use Simulink native GUI instead of Qt GUI by default.

- Resource analyzer is updated to use MATLAB app designer instead of Qt-based GUI.

- Timing analyzer is updated to use MATLAB app designer instead of Qt-based GUI.

- New SSR-FIR demo showing efficient implementations of very high data rate (over 1 Gsps) filter.

- General

- Major overhaul of the Vitis Model Composer hub block for scalability and ease of use.

- System Generator Token functionality is now merged into the Vitis Model Composer hub block.

- System Generator Token will be deprecated in 2022.2

- Hardware validation flow now supports Linux in addition to bare-metal.

- "AIE to HDL" and "HDL to AIE" blocks no longer include the HDL gateway blocks.

- The product is now shipped with a snapshot of the examples for customers who do not have access to the internet. The tool will prompt the user to download a new revision of the examples from GitHub if available.

- For ease of use, utility blocks that are not part of code generation are now presented with a white background color.

- Enhanced and reorganized the library browser for ease of use.

- RHEL 8.x support.

- MATLAB Support - R2021a and R2021b

- Major overhaul of the Vitis Model Composer hub block for scalability and ease of use.

In 2021.2, Vitis Model Composer includes many new feature additions and enhancements.

For more details, see below:

- AI Engines

- With a click of a button, run a design with AI Engines and PL (HLS, HDL) blocks into a Versal AI Core hardware.

- Significant speed up in Simulink simulation by parallel compilation of AIE blocks.

- Enhancements to AI Engine constraint editor

- Addition of DDS and Mixer blocks in the AIE DSP library

- Enhancements to "to fixed size" and "to variable size" blocks

- Support of int64 and uint64 data types

- Support for accfloat and caccfloat

- Enhancement to GitHub examples and incorporation of HLS examples in GitHub

- Generated data flow graph code now includes PLIO specification

- Enhanced usability to download and browse examples from GitHub

- Support for AIE source blocks

- xmcVitisRead and xmcVitisWrite utilities to read/write data files for AIE Simulator and/or x86Simulator

- Systematize GUI parameters of AIE dsplib blocks

- New 64x32 Pseudo Inverse design example

- New Dual-Stream SSR Filter example with 64 AI Engine kernels and up to 16 GSPS throughput

- HDL

- Support of Asymmetric read/write data widths for FIFO block

- HLS

- Supports simulation and implementation of HLS based C code that utilizes the AMD FIR, FFT, DDS Logicores

- General

- MATLAB Support - R2020a, R2020b, and R2021a

- Newly added support for Ubuntu 20.04

Vitis Model Composer now contains the functionality of AMD System Generator for DSP. Users who have been using AMD System Generator for DSP can continue development using Vitis Model Composer.

- AI Engines

- A comprehensive constraint editor enables users to specify any constraint for AI Engine kernels in Vitis Model Composer. The generated ADF graph will contain these constraints.

- Addition of AI Engine FFT and IFFT blocks to the library browser.

- Users now have access to many variations of AI Engine FIR blocks in the library browser.

- Ability to specify filter coefficients using input ports for FIR filters.

- Addition of two new utility blocks "RTP Source" and "To Variable Size".

- Enhanced AIE Kernel import block now also supports importing templatized AI Engine functions.

- Ability to specify AMD platforms for AI Engine designs in the Hub block.

- Through the Hub block, users can relaunch Vitis Analyzer at any time after running AIE Simulation.

- Users can now plot cycle approximate outputs and see estimated throughput for each output using Simulink Data Inspector.

- Enhanced usability to import a graph as a block using only the graph header file.

- Revamping of the progress bar with cancel button

- Usability improvement during importing an AI Engine kernel or simulation of a design when MATLAB working directory and model directory are not the same.

- Profiling during AIE Simulation is now disabled by default. It can be optionally enabled from the Model Composer Hub block.

- New TX Chain 200MHz example.

- New 2d FFT examples showcasing designs with HLS, HDL, and AI Engine blocks.

- HDL

- Simulation speed enhancement for SSR FIR (more than 10x improvement), and SSR FFT.

- Simulation speed enhancement for memory blocks like RAMs, and FIFOs

- Questa Simulator updated with VHDL 2008 in the Black-box import flow

- General

- Vitis Model Composer now contains the functionality of AMD System Generator for DSP. Users who have been using AMD System Generator for DSP can continue development using Vitis Model Composer.

- MATLAB Support - R2020a, R2020b, and R2021a

In 2020.2, Add-on for MATLAB & Simulink is the Unification of AMD Model Composer and System Generator for DSP.

Three inter-connectable domains:

- RTL ( System Generator for DSP)

- HLS (Model Composer)

- AI Engine which is a new domain targetable by the Add-On for MATLAB & Simulink

AI Engine (Model Composer)

- Imports AI Engine Kernels: C, C++, templates, state encapsulation classes

- Imports Adaptive Dataflow Graphs: supports templates

- Gateways between

- AI Engine and RTL domain

- AI Engine and HLS kernel domain

- Accepts location constainst and FIFO insertion.

- Library contains AI Engine DSP Library blocks

- Runs SW Emulation and AI Engine Emulation

Documentation

Training & Videos

Training

Videos

Designing AI Engines of AMD Versal ACAP Using Simulink and Vitis Model Composer

Designing a FIR filter on Avnet ZUBoard using Vitis Model Composer

Early FPGA/SoC Design Verification with Simulink and the Vivado Simulator from AMD

Download

Buy

Vitis Model Composer can be purchased as an add-on license to Vivado ML standard or enterprise editions and Vitis™ unified software platform.

To evaluate, generate a free 90-day evaluation license from the Product Licensing Site.

Download

Vitis Model Composer can be additionally selected as a Design Tool and installed through Vivado Installer or Vitis installer.