Overview

Overview of the AI Engine - DSP design process

Designing high-performance DSP functions targeting AMD Versal™ AI Engines can be done using either the AMD Vitis™ development tools or by using the Vitis Model Composer flow—taking advantage of the simulation and graphical capabilities of the MathWorks Simulink® tool.

In either case, mapping the DSP application into functions to implement in the FPGA or the AI Engines or a combination of FPGA logic and AI Engines is crucial. This requires an understanding of the device capabilities as well as the overall system.

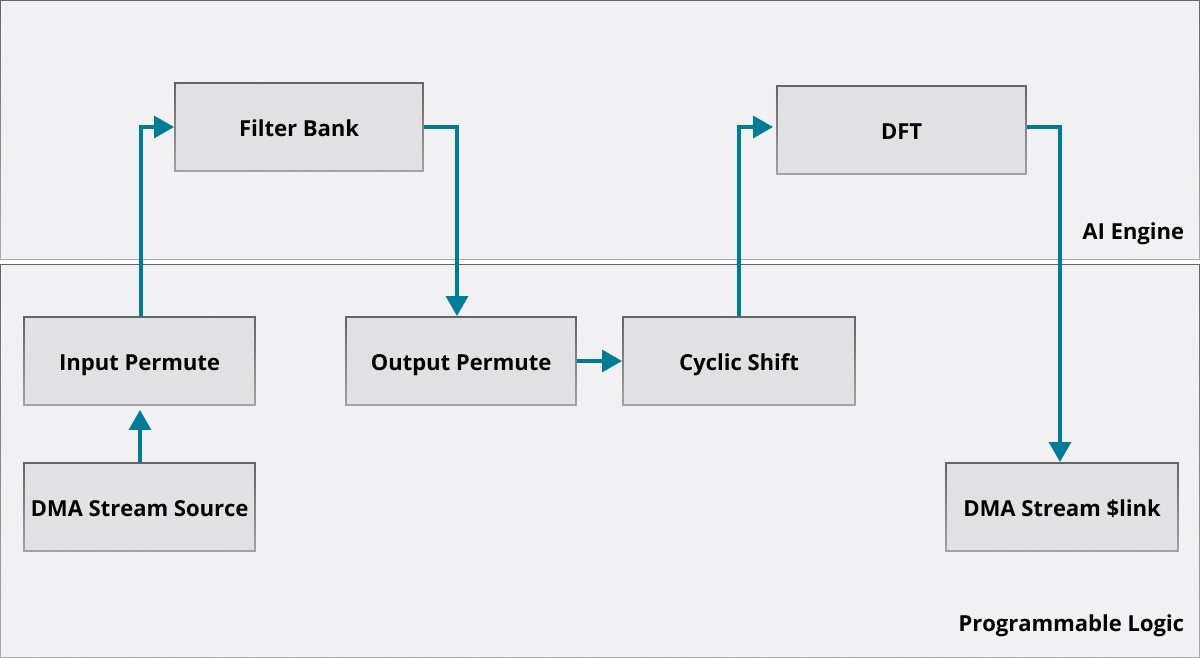

Typically, compute-intensive functions are better suited to AI Engine implementation, while functions that require data moving/re-ordering are better suited to an FPGA implementation.

In the example shown below, complex filtering and Fourier transforms are typically better suited within the AI Engine array.

Once functions have been clearly identified as AI Engine appropriate, they can be implemented into the AI Engine using any of the options below.

Note: A hybrid approach using multiple options from the list below is also possible.

Option 1

Vitis DSP Library Function Call

dsplib::fft::dit1ch::fft_ifft_dit_1ch

- Easiest to use

- Parameterizable

- Fastest development

Option 2

Vectorized Programming with AI Engine APIs

aie::vector<int8_t, sizeTileA> A0

aie::vector<int8_t, sizeTileA> A1

- Customizable

- Faster development

Option 3

Vectorized Programming with Intrinsics

Acc0 = mac16(acc0, Bbuff, 0, 0x00000000, 8, 0x3120, Abuff0, 0, 0xCC884400, 2, 0x3210);

Acc0 = mac16(acc0, Bbuff, 32, 0x00000000, 8, 0x3120, Abuff0, 0, 0xCC884400, 2, 0x3210);

- Full, low-level customization

- Lengthiest Development

To get started with AI Engines for DSP, it is highly recommended to start with Vitis DSP Library functions (C based) or with Vitis Model Composer (model based). While hand coding can result in a more optimized implementation, using the methods above is the fastest way to get started with AI Engines for DSP while also delivering strong performance.

Different AI Engine functions are then interconnected using graph C code, which is C++ code describing a network of multiple AI Engine tiles.

Using Vitis Model Composer allows for a graphical interconnection between the different AI Engine functions. This graphical representation can be converted push button into the graph C code by Vitis Model Composer. The robust simulation capabilities of the MathWorks Simulink environment can also be leveraged to verify the design.

To learn more about Versal AI Engine development using Vitis Model Composer, please visit the Versal AI Engine Development using Vitis Model Composer page.

Licensing the AI Engine Tools

Compiler and Simulator

While the AI Engine compiler and simulator tools are part of the AMD Vitis™ software installer, these tools still require a free license for use. You can get this license from the Product Licensing Site.

Enter your details and choose the “AI Engine Tools License” option.

Design Examples

Polyphase Channelizer Design for AI Engines

The polyphase channelizer down-converts simultaneously a set of frequency-division multiplexed (FDM) channels carried in a single data stream using an efficient approach based on digital signal processing. Channelizer use is ubiquitous in many wireless communication, radar, aerospace/defense, & medical imaging systems. In this tutorial, we implement two different channelizer designs using a combination of AI Engine and programmable logic (PL) resources in AMD Versal™ Adaptive SoC devices.

Resources

AMD Versal AI Engine design flow

Github Design Examples and Tutorials

- Vitis Design Tutorials (Vitis Tool-Based Flow)

Includes:- AMD Vitis™ Model Composer (Getting Started with Your First AI Engine Design)

- Super Sample Rate (SSR) FIR

- Polyphase Channelizer

- Beamforming

- General Matrix Multiply (GeMM)

- Vitis Model Composer (Model-based / Simulink® Flow)