Versal AI Core Series VCK190 Evaluation Kit

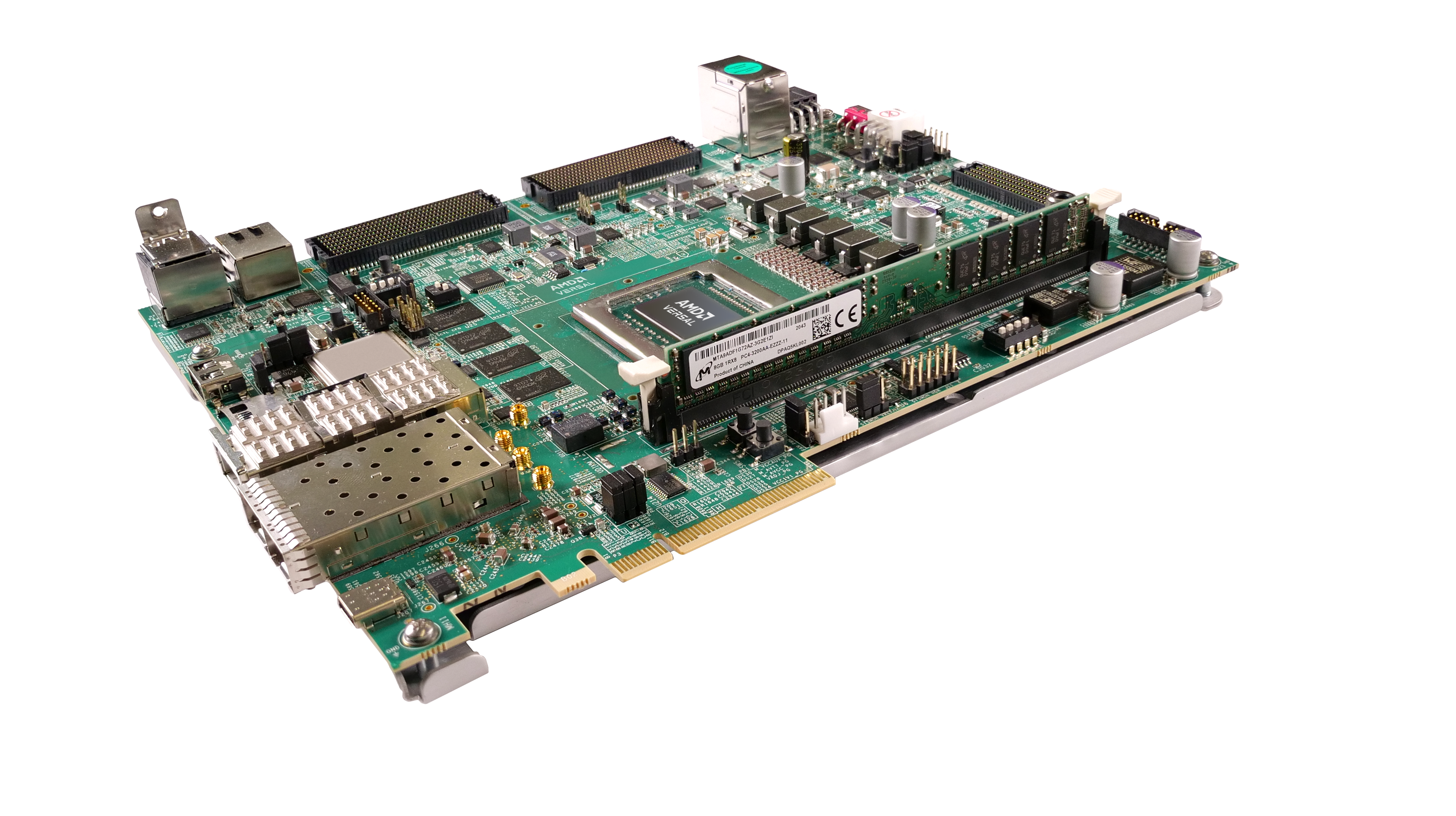

VCK190 is the first Versal™ AI Core series evaluation kit, enabling designers to develop solutions using AI and DSP engines capable of delivering over 100X greater compute performance compared to current server class CPUs. With a breadth of connectivity options and standardized development flows, the Versal AI Core series VC1902 adaptive SoC, providing the portfolio's highest AI inference and signal processing throughput for cloud, network, and edge applications.

Overview

Product Description

The VCK190 kit is the first Versal™ AI Core series evaluation kit, enabling designers to develop solutions using AI and DSP engines capable of delivering over 100X greater compute performance than today's server-class CPUs.

With a breadth of connectivity options and standardized development flows, the VCK190 kit features the Versal AI Core series VC1902 device, providing the portfolio's highest AI inference and signal processing throughput.

The VCK190 kit is an ideal platform supporting high throughput AI inference and signal processing applications from the cloud to edge, such as:

- Data center compute

- 5G radio & beamforming (DFE)

- Cable-access (Head-End)

- Wireless test equipment

- Automotive/ADAS prototyping

- A&D radar, early warning

Key Features & Benefits

Versal AI Core Series Capabilities

- Equipped with Versal AI Core VC1902 device

- AI and DSP Engines providing 100X greater compute over today’s server-class CPUs

- Pre-built partner reference designs for rapid prototyping

Breadth of Connectivity Options for Rapid Application Development

- PCIe® Gen4 interface for high compute performance markets

- HDMI for video processing applications

- SFP28 and QSFP28 optical interfaces and RJ-45 Ethernet port for networking

- DDR4 and LPDDR4 memory interfaces

- FMC expansion connectors supporting a variety of optional plug-in cards including camera sensors and displays

Co-Optimized Tools and Debug Method

- Vivado™ design suite, Vitis™ unified software platform, Vitis AI, AI Engine tools

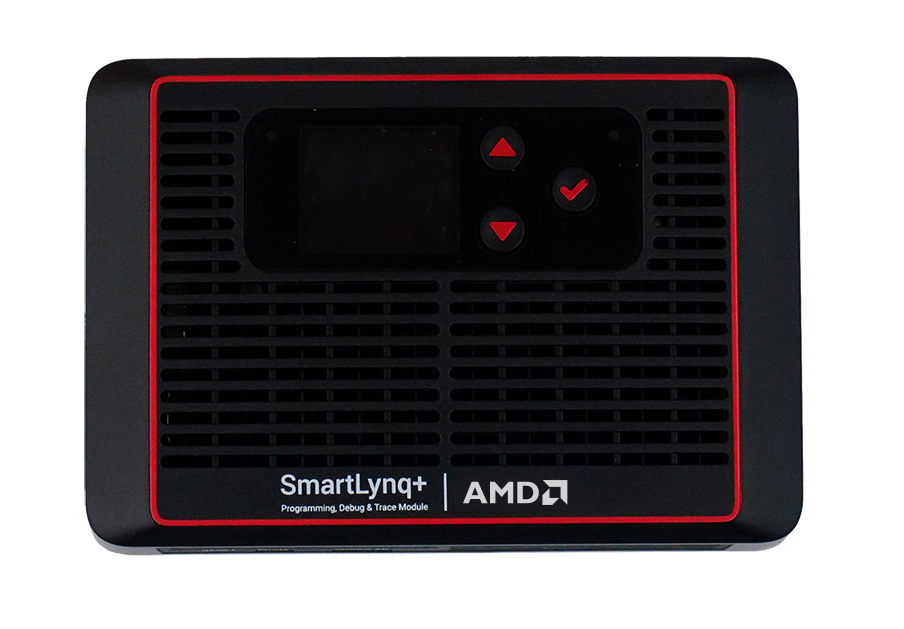

- SmartLynq+ module for high-speed debug, performance analysis, and event trace

Featured AMD Devices

Featuring the Versal AI Core XCVC1902-2MSEVSVA2197 Adaptive SoC

| AI Engines | 400 |

|---|---|

| DSP Engines | 1,968 |

| System Logic Cells (K) | 1,968 |

| LUTs | 899,840 |

| Application Processing Unit | Dual-Core Arm® Cortex®-A72 |

| Real-Time Processing Unit | Dual-Core Arm Cortex-R5F |

| Maximum I/O Pins | 770 |

| Programmable NoC Ports | 28 |

| Integrated Memory Controllers | 4 |

Product Information

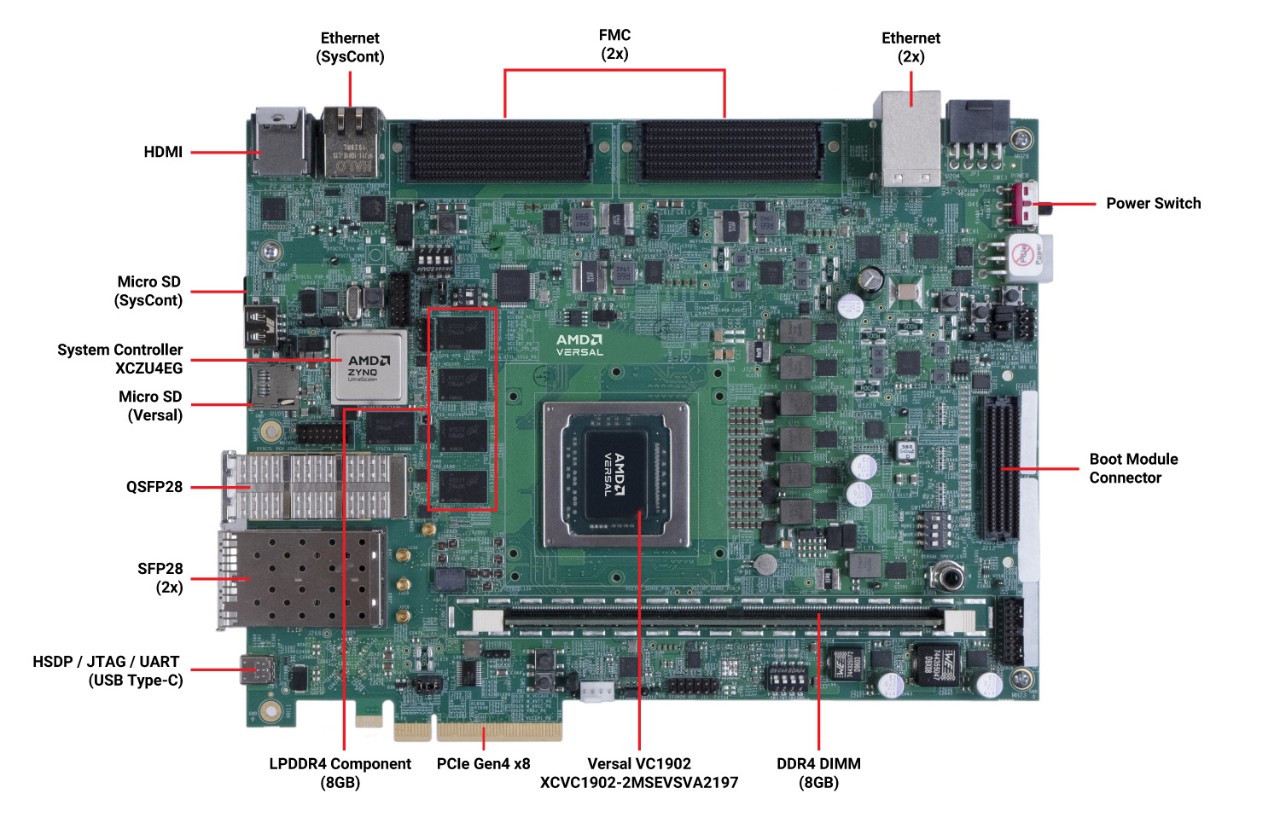

Board Features

Featuring the Versal™ AI Core XCVC1902-2MSEVSVA2197 Adaptive SoC

| Board Specifications | Value |

|---|---|

| Length | 9.50 inches (24.13 cm) (¾ PCIe length) |

| Height | 7.477 inches (18.992 cm) |

| Thickness | 66.87 mil ±10% (1.698 mm ±10%) |

| Operating Environmental Temperature | 0°C to +45°C |

| Storage Environmental Temperature | –25°C to +60°C |

| Configuration | |

| JTAG | Yes |

| QSPI | Yes |

| MicroSD | 2 |

| Memory |

|

| DDR4 DIMM | 8 GB @ 3200 Mb/s |

| LPDDR4 Component | 8 GB (4x16 Gb) @ 3900 Mb/s |

| MicroSD Socket | 16 GB |

| Control I/O | |

| User Pushbuttons | 6 |

| DIP Switches | 4 |

| User LEDs | 4 |

| SYSMON | Yes |

| System Controller | Yes |

| PMBUS | Yes |

| Expansion Connectors | |

| VITA 57.4 FMC+ (12 GTYs per connector) | 2 |

| PCIe® Gen4 x8 | 1 |

| Communication & Networking | |

| UART to USB Bridge | 1 |

| CAN-FD Header | 1 |

| RJ-45 Tri-Speed Ethernet Connectors | 3 |

| SFP28 | 2 |

| QSFP28 | 1 |

| Display | |

| HDMI Video Output | 1 |

| HDMI Video Input | 1 |

| Clocking | |

| Programmable DDR4 DIMM | 1 |

| Programmable LPDDR4 Component | 2 |

| PCIe Reference Clock | 1 |

| HDMI | 1 |

| Programmable zSFP | 1 |

| Programmable HSDP | 1 |

| Programmable 1588 eCPRI | 4 |

| Programmable System Controller | 1 |

| Power | |

| 180W (12V) Power Supply | Yes |

| Power-on Reset | Yes |

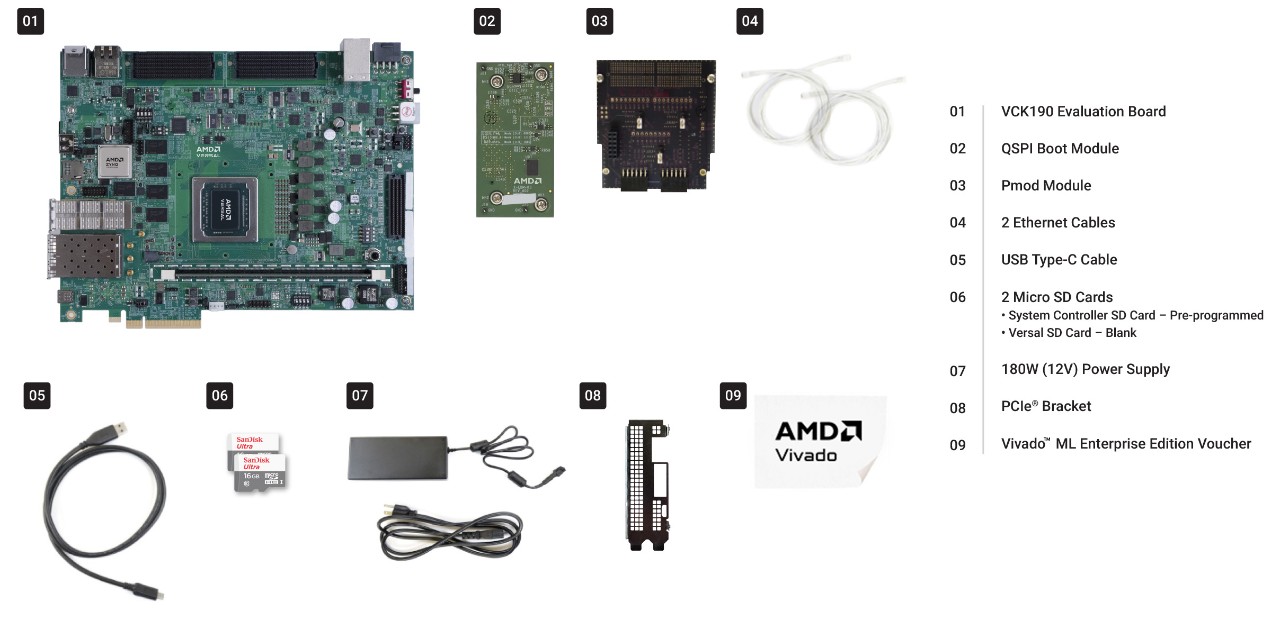

What's Inside the Box

Featuring the Versal™ AI Core XCVC1902-2MSEVSVA2197 Adaptive SoC

Resources

Design Tools

- Vivado™ Design Suite: The EDA tool suite to create projects for the VCK190 board. Node-locked and device-locked to the Versal™ AI Core XCVC1902 device, with one year of updates.

- Vitis™ Unified Software Platform: The full suite of tools for developing embedded software, debugging Versal devices, and running targeted reference designs and example designs.

- Vitis™ Model Composer: The Model-Based Design tool for the MathWorks MATLAB® and Simulink® targeting AI Engines and Programmable Logic design through automatic code generation.

PetaLinux Tools, Board Support Packages, and Prebuilt Images

- To build custom Linux images with modifications, visit the PetaLinux tool page to get an installer and latest board supported packages (BSP).

- To boot with Linux images without modifications, download pre-built PetaLinux images.

Get Started with VCK190

To jump-start prototyping and application development with the VCK190, visit the Wiki page.

- Prep work

- Board setup

- Run the PetaLinux BSP pre-built image

- Run the PetaLinux BSP out of the box example