Overview

Important Notice

This development kit has been discontinued and is no longer offered for sale. The solutions targeted for this product will not be updated moving forward with limited support available from AMD.

Product Description

The Kintex™ UltraScale™ FPGA Acceleration Development Kit is an excellent starting point for hyperscale application developers. This kit is based on a production-ready PCI card accessible in the cloud with the frameworks, libraries, drivers and development tools to support easy application programming with OpenCL, C, C++ through SDAccel. Get started in the cloud, with this physical kit or both to move through development with AMD and go to production with one of AMD ecosystem partners.

Key Features & Benefits

- Specialized reprogrammable hardware for computationally intensive applications, specifically targeting the fast-growing markets for live video transcoding, data analytics, and artificial intelligence (AI) applications using machine learning

- Single slot PCIe® half-length full height form-factor compliant: Actual dimensions are 6.600 in x 4.199 in

- Delivers 10-30x performance acceleration over traditional CPUs with a card designed to support 75W

- Supported with SDAccel™ Development Environment for OpenCL, C, C++

- Open Sources examples

- SDAccel Platform Reference Design for custom board support

Featured AMD Devices

Featuring the XCKU115-2FLVB2104E

| System Logic Cells (K) | 1,451 |

|---|---|

| DSP Slices | 5,520 |

| Block RAM (Mb) | 75.9 |

| 16.3Gb/s Transceivers | 64 |

| I/O Pins | 832 |

Product Information

Board Features

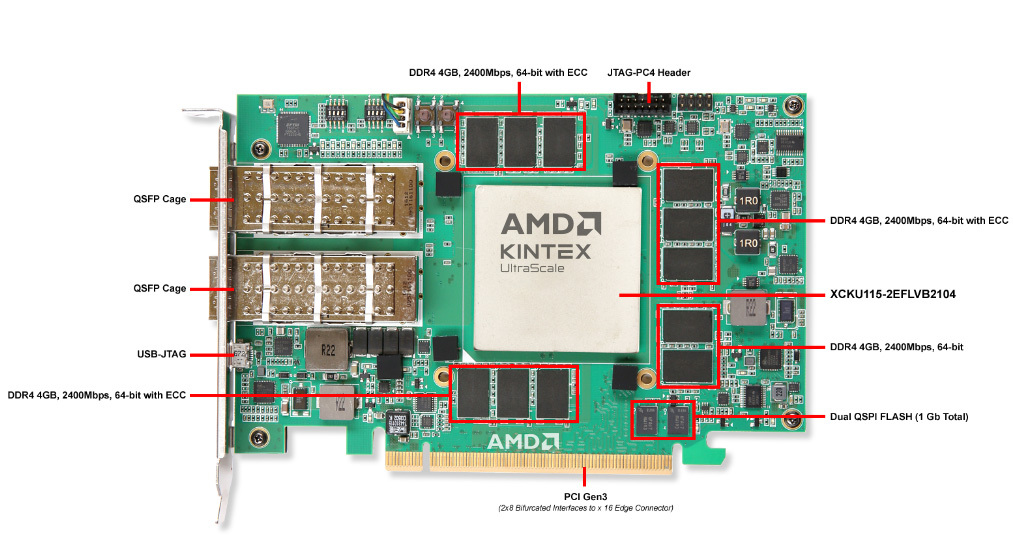

Featuring the KCU1500 Board

Memory

- 16 GB DDR 4 memory

- 3x DDR4 4GB, 2400Mbps, 64-bit w/ ECC

- 1x DDR4 4GB, 2400Mbps, 64-bit w/ no ECC

- 1Gb Dual Quad SPI Flash

Power & Thermal

- Chassis powered supporting 75W maximum operation

- Fan or passive heat sink

- On-board power telemetry via PMBus

Configuration

- JTAG PC4 Header and USB-JTAG Header

- Dual Quad-SPI flash memory

Communication & Networking

- Two QSFP cages

- PCIe Gen3 : Two x8 interfaces bifurcated to x16 edge connector

What's Inside

KCU1500 board featuring the XCKU115-2FLVB2104E

Voucher providing access to underlying programming tools

Vivado and SDAccel

USB Cable

Resources

Design Tools

| Name | Description | License Type |

|---|---|---|

| Vivado Design Suite Design Edition | The AMD Vivado™ Design Suite is a revolutionary IP and System Centric design environment built from the ground up to accelerate the design for FPGAs and SoCs. | Node locked and device-locked to the KCU1500 FPGA, with one year of updates. Supports Dynamic Function eXchange |

| SDAccel Development Environment | SDAccel is a development environment for OpenCL applications targeting PCIe®-based AMD FPGA accelerator cards. This environment enables concurrent programming of the system processor and the FPGA logic without the need for RTL design experience. | Node locked and device-locked to the KCU1500 FPGA, with one year of updates. |

| Dynamic Function eXchange | Dynamic Function eXchange is the ability to dynamically modify blocks of logic by downloading partial bit files while the remaining logic continues to operate without interruption. AMD Dynamic Function eXchange technology allows designers to change functionality of the accelerator board on the fly, eliminating the need to fully reconfigure and re-establish PCIe links while reloading. | Node locked and device-locked to the KCU1500 FPGA, with one year of updates. |

Intellectual Property

| Name | Description | License Type |

|---|---|---|

| DDR4 SDRAM Controller | DDR4 SDRAM controller is a free IP core in the Vivado IP Catalog. | No-Charge IP |

| DMA for PCI Express (PCIe) Subsystem | The AMD LogiCORE™ DMA for PCI Express (PCIe) implements a high performance, configurable Scatter Gather DMA for use with the PCI Express 3.x integrated block. The IP provides an optional AXI4 or AXI4-Stream user interface. | No-charge IP |

| AMD SmartConnect Technology | The AMD SmartConnect Technology enables unprecedented levels of performance for the UltraScale+™ device portfolio, by solving the system interconnect bottlenecks on high density, multi-million system logic cell designs. | No-charge IP |

| SDAccel Platform Reference Design for Custom Board Support | SDAccel projects are compiled against a target platform. The SDAccel Platform Reference Design is the combination of board and hardware/software infrastructure components on which the kernels of an OpenCL application are executed. This reference design is intended to be used as a starting point to help platform developers add SDAccel support for their custom PCIe boards. | No-charge IP |