Software Defined

- Design Tools

- Legacy Tools

- SDAccel Development Environment

Note: Starting 2019.2, AMD SDK, SDSoC™ and SDAccel™ development environments are unified into an all-in-one Vitis™ unified software platform for application acceleration and embedded software development. There will be no 2019.2 or future releases of AMD SDAccel Development Environment.

Introduction

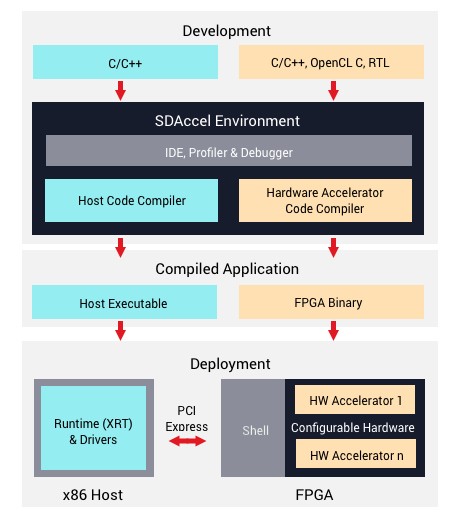

The SDAccel™ environment is an integrated development environment for applications targeting AMD Alveo Data Center accelerator cards, AWS F1 instances and other FPGA-as-a-Service offerings.

It provides a familiar software development flow with:

- An Integrated Development Environment (IDE)

- A profiler to guide application optimization

- Compilers for host & FPGA-accelerated code

- Emulation flows for rapid development and debug

- Automatic communication between software and hardware

The host application is developed in C/C++ and uses standard OpenCL API calls to interact with the FPGA-accelerated functions which can be modeled in either RTL, C/C++, or OpenCL. This provides familiar entry points for hardware designers and software engineers alike.

The SDAccel IDE provides all the features of a standard software development environment: optimized compiler for host applications, cross compiler for the adaptable hardware, a robust debugging environment, and profilers to identify performance bottlenecks and optimize the application.

The Xilinx runtime (XRT) and board-specific shells automatically manage communication between the FPGA accelerators and the host application. The software developer does not need to implement any of these connection details.

Advantages

Benefits of Adaptable Hardware Acceleration

- Performance increase of 10x-1000x*

- Lower latency

- Lower power consumption

- Less CPU time consumed

- Ease of use with the SDAccel Development Environment

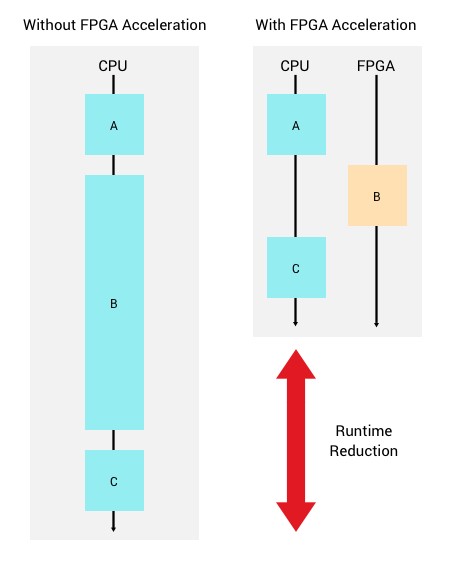

AMD FPGAs and ACAP devices are uniquely suitable for low latency acceleration of high performance algorithms and workloads.

The decline in Moore's Law and Dennard Scaling, coupled with Amdahl’s Law means Design-Specific Architectures or DSAs are becoming the tool of choice for developers needing the highest performance, lowest latency and lowest energy consumption for their accelerated applications.

FPGA and ACAP devices are adaptable, allowing DSAs to be built to accelerate specific parts of the code, as opposed to general-purpose CPUs and GPUs.

The SDAccel development environment provides a comprehensive set of tools and reports to profile the performance of your host application, and determine opportunities for acceleration.

The tools also provide automated runtime instrumentation of cache, memory and bus usage to track real-time performance on the hardware.

* Performance increase of 10x to 1000x is application dependent.

Deployment Options

Applications developed with the SDAccel environment can be targeted at a range of deployment options:

Key Documents

SDAccel

Buy Online From Xilinx

Software Only

-

Buy Node-Locked License

- Price: $2995

- Lead Time: Immediate

-

Buy Floating License

- Price: $3595

- Lead Time: Immediate

SDAccel Licenses for Alveo

Buy Online From Xilinx

Software Only

-

Buy Node-Locked License

- Price: $100

- Lead Time: Immediate

-

Buy Floating License

- Price: $100

- Lead Time: Immediate

Note: If you have already purchased a Vivado HLx license, your account holds a free license to develop for AWS F1 on-premise.

Free 30-day trial offered in all SDAccel starting with release 2018.2 XDF Edition. Download software and select free trial at the end of install.