- Technology

- Functional Safety

Functional Safety

Highest Levels of Safety and Reliability

AMD provides a comprehensive TUV SUD certified design flow solution for our customers to simplify and accelerate certifications based on functional safety specifications across Aerospace & Defense, Automotive, Medical and Industrial markets where safety and reliability are key.

Functional Safety Standards Supported

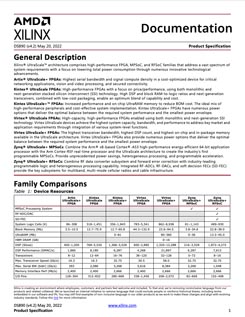

| Application | Standard |

|---|---|

| Automotive | ISO 26262 |

| Industrial and Medical | IEC 61508, IEC 62061 and ISO13849 |

| Aerospace & Defense |

DO-254/DO178b |

AMD Unique Value Proposition

AMD has decades of proven success and experience across a wide variety of mission-critical industries and applications. Our customers choose our portfolio of FPGAs and SoCs for to enable:

- Configurability and increased performance at lower power

- Integration of complex and complete systems into a single device

- Reliability and long product life time

- Faster time to market

Certified Hardware and Software Design Tools

- Design and verification tools certified for use in Functional Safety applications

- Certified Compiler tools

- Functional Safety Certificate and Reports

- Functional Safety Package

Certified Methodologies & IPs

- Certified functional safety design methodologies enable integration of safety and non-safety functions in the same device

- Isolation Design Flow (IDF) and Vivado Isolation Verifier (VIV) / Isolation Verification Tools (IVT) provide a certified methodology to separate areas on a single device. Designs placed into these regions are physically isolated. The areas can be changed at any time without impacting other isolated regions, proven by the VIV/IVT tools (impact analysis)

- Certified Soft Error Mitigation (SEM) IP cores perform Single Event Upset (SEU) detection, correction, and classification for configuration memory. The cores utilize device primitives such as ICAP and FRAME_ECC to clock and observe the Readback CRC feature as part of the SEU detection function. For SEU correction, the IP cores perform the necessary operations to locate and correct errors. For SEU classification, the IP cores use AMD Essential Bits technology to further increase system availability.

Assessed Safety Concept Design

The Zynq™ 7000 SoC has been reviewed and assessed for on-chip redundancy by TuV Rheinland. This Safety Concept Design study states AMD technology can be used to create a single chip solution that will support 2 independent safety channels for SIL3 safety functions referencing IEC61508 Part2 Annex-E.

Functional Safety Lounge

The Functional Safety Lounge provides access to solutions, documentation and additional resources to subscribers.

For paid subscribers only, log in.

Functional Safety Working Group (FSWG) 2024

The AMD Functional Safety Working Group is an annual multi-day FREE event in North America and Europe that brings together AMD Industrial, Automotive and Avionics customers, academic representatives, Alliance Partners and certification authorities to discuss the latest Functional Safety solutions from AMD.

The AMD Functional Safety Working Group provides an excellent forum for participants to learn from AMD functional safety leaders and where attendees can connect with their functional safety peers in the industry. Attendees will develop a better understanding of industry’s safety requirements for today and tomorrow as well as learn about innovative and unique solutions coming from AMD.

The unique aspect about this working group is that an NDA is required. This allows AMD to present roadmap and detailed design information that would not normally be presented in such a forum. ALL PARTICIPANTS WILL REQUIRE A CURRENT NDA

The AMD Functional Safety Working Group events for 2024 will be held in two locations:

AMD Functional Safety Working Group 2024. Registration is now Open!

For more information, feel free to contact your local AMD sales representative.

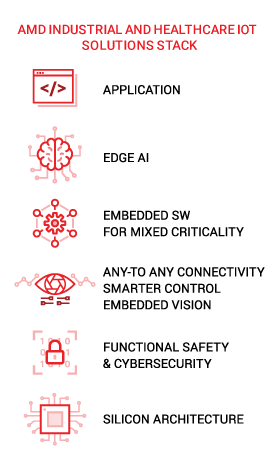

Some Industrial IoT products need all elements of the AMD IIoT Solutions Stack, all need some. The AMD IIoT Solutions Stack is comprised of optimized AMD and Ecosystem building blocks and solutions used across Industrial and Healthcare IoT platforms. Starting from scratch is never something you will have to do with an AMD-based Industrial IoT system. Minimize development time and cost and maximize design reuse on your next Industrial IoT platform by exploring the different elements of the AMD IIoT Solutions stack.