- Applications

- Aerospace and Defense

- Avionics & UAV

Avionics

30+ years of heritage in airborne systems, supporting adaptability, certification, and reliability.

Enabling Airborne Platforms: Civil, Military, and Unmanned Systems

With 30+ continuous years of heritage serving commercial and military avionics applications, AMD offers Commercial-grade and Defense-grade FPGA and SoC devices, a full range of IP cores, advanced tool flow support, industry leading SEU solutions, and superior device reliability.

AMD has established use in certified platforms, and now offers an MCFA data package to address avionics certification of the multi-core processing system within Zynq UltraScale+™ MPSOC device.

Through collaboration with technology leaders, industry experts, and the user community, AMD offers a comprehensive ecosystem of DO-254 and DO-178 certification solutions and expertise, providing developers with the practical guidance and certification support to reduce the cost, risk and time to market of next-generation avionics.

Access the Avionics Developers’ Site

The Avionics Developer's Site contains Information to aide in FPGA and SoC application development for avionic equipment and other high reliability systems. This site contains specific guidance, tools and solutions such as SEU guidance and SEU FIT Rate Calculator.

Click here for access: Avionics Developers' Site

AMD Functional Safety Extends Avionics Solutions

Avionics, Automotive, Industrial, and Medical share a common base of certification requirements that aim to address safety and reliability in the development of critical systems. Complementing investment by AMD in reliability and quality initiatives we have invested in Functional Safety certification for Industrial and Automotive applications requiring compliance with IEC 61508 and ISO 26262. AMD has received functional safety certification for tool chains and devices as well as the Isolation Design Flow (IDF). Functional safety initiatives by AMD for industrial and automotive applications can be used to complement our certifiable avionics solutions.

Adoption in a Broad Set of Avionics & UAV Applications

UAV / Drone and other Applications Support

AMD and Topic Embedded partnered to bring to market a UAV and Robotics Platform (URP) which enables a full host of capabilities required in such applications. The URP is built on the Zynq UltraScale+ MPSOC ZU7EV or ZU5EV device. The expansive feature set is offered in a compact single board. This platform is fully software programmable, delivered with the core infrastructure of embedded software and drivers and programmable logic IP platform. For more info see the URP product brief.

Related Cross-Domain Solutions

AMD solves for certification with domain expertise and ecosystem partnership. Refer to the Overview, Ecosystem, and Documentation tabs on this page for more detail on addressing DO-254 and DO-178 for commercial and defense systems.

Refer back to the main A&D page for Defense-grade XQ Ruggedized device needs and for guidance to get started developing on AMD.

Specific solutions for Milcom & Satcom as well as Radar may be of additional interest for avionics applications.

As functional safety solutions can assist in avionics certification, industrial motor control and automotive camera based driver assist solutions can complement avionics applications development. For additional information on functional safety and common applications, visit our Industrial and Automotive application pages.

Refer to the following table for Partner page links on AMD.com as well as link to key products or announcement of relevant solutions for AMD devices.

The additional webinar recordings can provide further insights using the referenced solution with AMD.

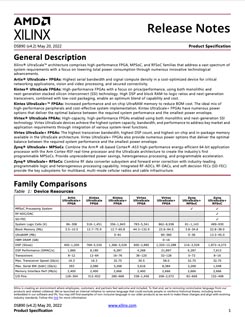

| Partner | Solution Domain | Key Offering(s) |

|---|---|---|

| CoreAVI | DO-178 & Embedded Graphics | OpenGL SC embedded drivers |

| DDC-I | DO-178 & Embedded | Deos RTOS |

| Green Hills | DO-178 & Embedded | Integrity 178 RTOS |

| Logicircuit | DO-254 & DO-178 Certification | DO-254 IP Portfolio and DO-254 / DO-178 service work |

| Lynx Software | DO-178 & Embedded | Lynx Secure separation kernel and DO-178 RTOS |

| Rapita Systems | DO-178 & Embedded | Multi-core verification tools and services |

| Topic Embedded | Platforms (Hardware + Embedded) | UAV and Robotics Platform (built on ZU7EV / ZU5EV) |

| Wind River | DO-178 & Embedded | VxWorks 653 RTOS and other |

| Webinar Recordings | Companies and Solutions Presented |

|---|---|

| Zynq UltraScale+ MPSOC for Avionics Certification | DDC-I, Logicircuit, and AMD

|

| Multi-core Certification, Interference Analysis and WCET | DDC-I and Rapita Systems (based on Zynq UltraScale+) |