- Applications

- Test & Measurement Solutions

- Semiconductor Automated Test Equipment

Semiconductor Automated Test Equipment

Comprehensive solutions enable next-generation SoC, signal, radar, and memory test platforms

Next-generation SoC testers need to test a broader range of I/O protocols, which have increasing complexity and speed. Industry-leading SerDes and HSSIO technology offer the most flexibility at the right cost point to realize high volume SoC, mixed signal, radar/camera sensor, and memory testers. Integrated hard IP for memory controllers and chip-to-chip interconnect reduce resource usage to enable cost-effective solutions.

| Design Examples | Description | Device Support |

|---|---|---|

Click to enlarge |

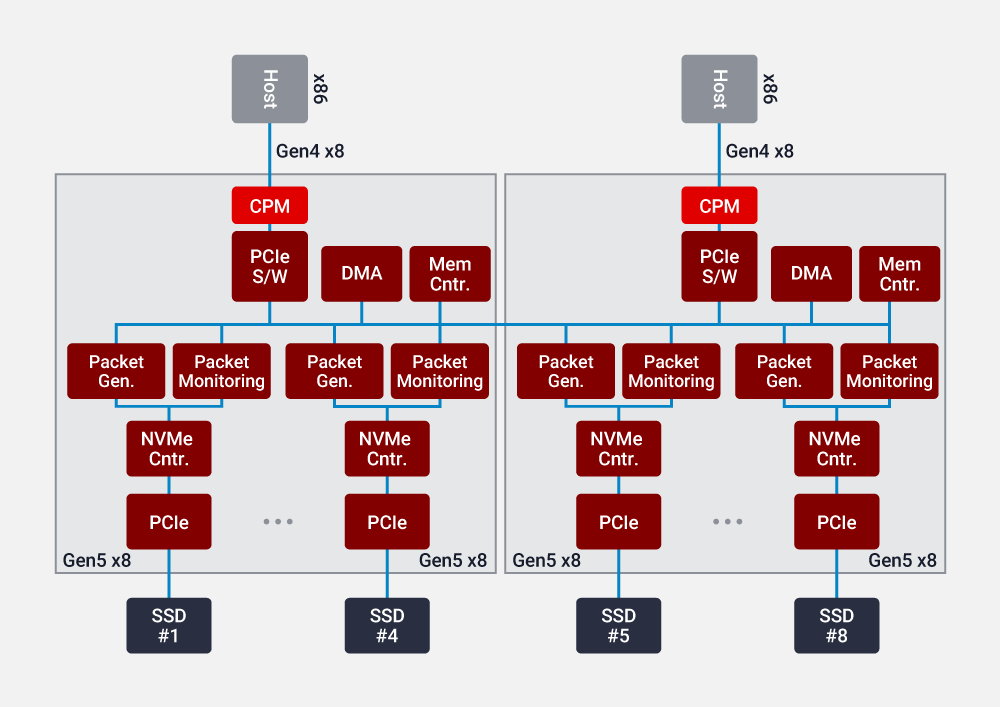

SoC and Storage Testers The innovative Versal™ architecture gives system designers performance, flexibility, and power-optimized hard IP that are not available in any other device solution. AI Engines and DSP Engines in the Versal Premium adaptive SoCs provide unmatched signal processing capacity with on/off-chip memory bandwidth at higher speed. 7.5M system logic cells in the Adaptable Engines play a critical role in developing ATE by providing flexibility for custom IP, traffic generation, and monitoring functionality. Scalable 112G PAM4 transceivers and power-optimized Hard IP such as 600G Ethernet MAC, 400G High-Speed Crypto Engines, DDR memory controller, and integrated PCIe® Gen5 blocks are pre-engineered to enable the most popular interface standards with a wide variety of feature and performance options. |

Versal Premium Adaptive SoC |

Click to enlarge |

Semi-ATE: Image Acquisition Image Acquisition requires high performance transceivers and DSP capability while keeping the power consumption and device cost low for this cost sensitive application. Kintex™ UltraScale+™ provides the best price/performance/watt balance delivering the most cost-effective solution for high-end capabilities including 32Gbps transceivers, 6.3 TeraMACs of DSP compute performance, 2.6Gbs DDR4, and PCIe Gen4x8 support. |

|

Click to enlarge |

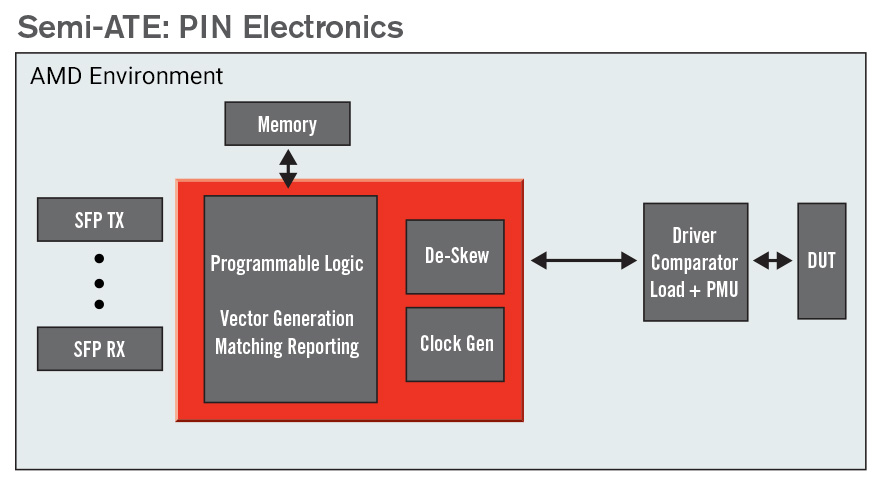

Semi-ATE: PIN Electronics PIN Electronics calls for cost-effective FPGAs for vector generation and analysis as well as large number of high-performance I/Os to connect to a large number of ASSPs with parallel interfaces. Given the 1Gb/s+ link speed, unfriendly channel, and fewer reference clocks, the I/O buffers and clock generation/distribution capability need to be sophisticated to manage skew across multiple lanes and over PVT. Kintex UltraScale+ FPGAs have high- performance and feature-rich SelectIO™ transceivers with signal conditioning capabilities, PLL and DLL based clock generation and distribution resources, and skew management capabilities. This makes the Kintex UltraScale+ FPGA ideally suited for PIN Electronics applications. |