Automotive Grade Zynq UltraScale+ MPSoCs

- Devices

- SoCs, MPSoCs and RFSoCs

- Automotive Grade Zynq UltraScale+ MPSoCs

Automotive grade Zynq UltraScale+ MPSoC Product Advantages

The AMD Automotive XA Zynq™ UltraScale+™ MPSoC family is qualified according to AEC-Q100 test specifications with full ISO26262 ASIL-C level certification. The product integrates a feature-rich 64-bit quad-core Arm® Cortex®-A53 and dual-core Arm Cortex-R5 based processing system (PS) and AMD programmable logic (PL) UltraScale architecture in a single device. This scalable solution is ideally suited for various automotive customer platforms by delivering the right performance/watt while integrating critical functional safety and security features.

| Value | Features |

|---|---|

| Smarter, Optimized & Most Secure Solution |

|

| Unmatched Integration, Performance, and Power |

|

| Proven Productivity |

|

Processing System (PS)

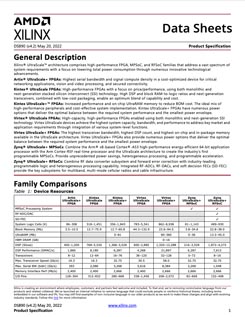

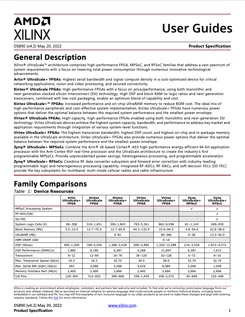

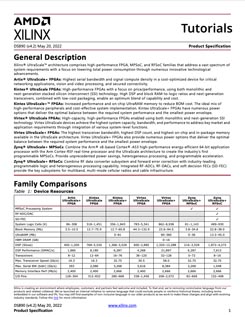

| Features | All Devices |

|---|---|

| Application Processing Unit | Quad-core Arm Cortex-A53 MPCore with CoreSight; NEON & Single/Double Precision Floating Point; 32 KB/32 KB L1 Cache, 1 MB L2 Cache |

| Real-Time Processing Unit | Dual-core Arm Cortex-R5 with CoreSight; Single/Double Precision Floating Point; 32 KB/32 KB L1 Cache, and TCM |

| Embedded and External |

Memory256 KB On-Chip Memory w/ECC; External DDR4; DDR3; DDR3L; LPDDR4; LPDDR3; External Quad-SPI; NAND; eMMC |

| General Connectivity | 214 PS I/O; UART; CAN; USB 2.0; I2C; SPI; 32b GPIO; Real Time Clock; WatchDog Timers; Triple Timer Counters |

| High-Speed Connectivity | 4 PS-GTR; PCIe Gen1/2; Serial ATA 3.1; DisplayPort™ 1.2a; USB 3.0; SGMII |

| Graphic Processing Unit | Arm Mali™-400 MP2; 64 KB L2 Cache |

Programmable Logic (PL)

| ZU1EG | ZU2EG | ZU3EG |

ZU4EV | ZU5EV | ZU7EV | ZU11EG |

|

| System Logic Cells (K) | 82 | 103 | 154 | 192 | 256 | 504 | 653 |

| Memory (Mb) | 3.8 | 5.3 | 7.6 | 18.5 | 23.1 | 38.0 | 43.6 |

| DSP Slices | 216 | 240 | 360 | 728 | 1,248 | 1,728 | 2,928 |

| Video Code Unit (VCU) | 1 | 1 | 1 | ||||

| Maximum I/O Pins | 252 | 252 | 252 | 252 | 252 | 204 | 464 |

Note: Some restrictions may apply. Refer to UG585, Zynq 7000 SoC Technical Reference Manual and DS188, XA Zynq 7000 SoC Overview for details.