- Applications

- Test & Measurement Solutions

- Wired & Wireless Testers

Wired & Wireless Testers

Enabling Next Generation Testers for Data Center, Wired and Wireless Next-Generation Networks

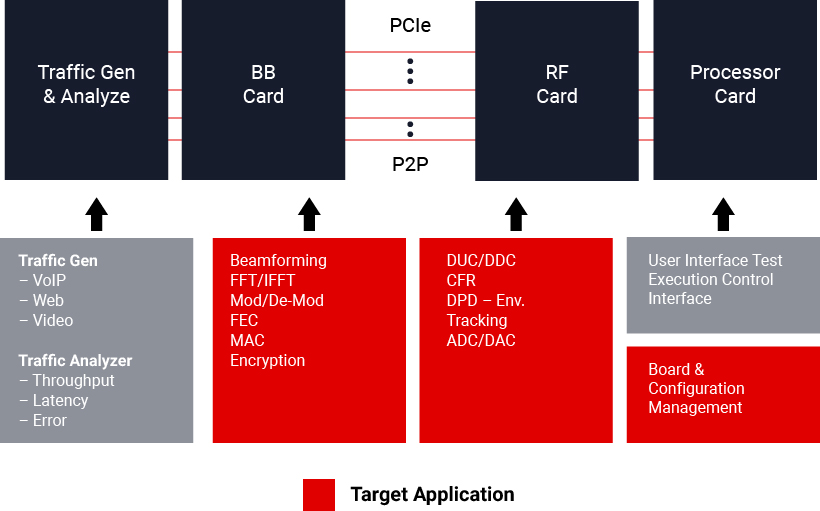

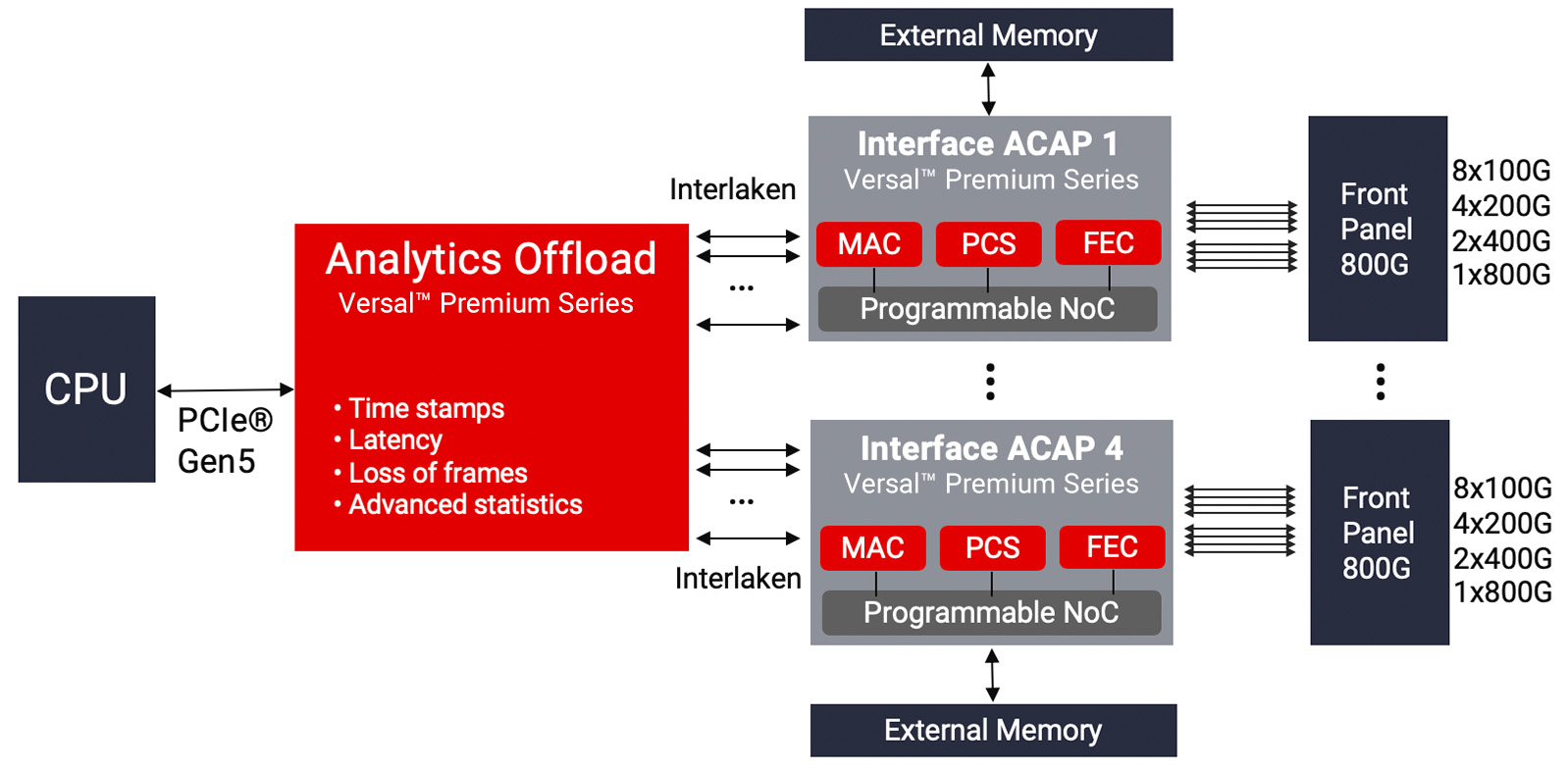

Data center testers require the highest serial I/O throughput and thermally efficient solution to implement PCS, FEC, and MAC. The Versal™ Premium adaptive SoC offers 112G PAM4 transceivers as well as massive networked hard IP including 600G channelized multirate Ethernet subsystem (DCMAC) with KP4/KR4 FEC, integrated 600G Interlaken with FEC, and 400G High-Speed Crypto (HSC) Engines to enable the fastest and most advanced test equipment.

Wireless testers require signal processing as well as a high I/O count for interfacing with data-converters, CPU, and memory. The Versal Premium series offers 24TOPs of signal processing capacity, 9Tb/s serial I/O bandwidth, and 136GB/s of external memory bandwidth to provide the high-performance compute density.

| Design Examples | Description | Device Support |

|---|---|---|

Click to enlarge |

Mobile Phone Tester

|

|

Click to enlarge |

Ethernet Tester: Layer 1-3

|